Auf dem jüngsten RISC-V-Gipfel fand in der allerletzten Sitzung eine Podiumsdiskussion über Chiplets statt Chiplets im RISC-V-Ökosystem. Moderiert wurde es von Calista Redmond, dem CEO von RISC-V International. Die Diskussionsteilnehmer waren:

- Laurent Moll, COO von Arteris

- Aniket Saha, Vizepräsident des Produktmanagements von Tenstorrent

- Dale Greenley, VP of Engineering von Ventana Microsystems

- Rob Aitken, angesehener Architekt von Synopsys

Für mich ist das eine etwas seltsame Themenkombination. Natürlich können Sie einen RISC-V-Prozessor auf einem Chiplet unterbringen, aber die Herausforderungen unterscheiden sich nicht wirklich von denen anderer Prozessoren. Aber RISC-V ist heiß, genau wie Chiplets, und Unternehmen wie Ventana kombinieren sie.

Lassen Sie mich Ihnen ein paar Hintergrundinformationen zu den Unternehmen geben, um sie in einen Kontext zu bringen:

- Wie Sie wahrscheinlich wissen, stellt Arteris Networks-on-Chip (NoCs) her. Es ist ein neutrales Unternehmen unter den Chiplet-Anbietern (und IP-Anbietern).

- Tenstorrent entwickelt ein Portfolio sehr leistungsstarker Multicore-RISC-V-Chips

- Ventana verfügt über RISC-V-IP, liefert es aber auch als Chiplets

- Synopsys ist offensichtlich ein EDA-Unternehmen, aber sie haben bereits früher auf dem Gipfel RISC-V-Kerne angekündigt

]

Die eigentliche Diskussion

Die erste Frage von Calista war eine Softballfrage nach dem Wert von Chiplets.

Dale sagte, es gebe nichts Spezifisches zu RISC-V für Chiplets, aber der Markt entscheide, wann man große monolithische Dinge oder Chiplets mache. Es hängt davon ab, wofür ein Kunde Sie bezahlen wird. „Wir bieten sowohl IP als auch Chiplets an, es gibt Platz für beides.“

Aniket sagte: „Die Herstellung von Chiplets ist nicht billig, aber die Herstellung von Chiplets und RISC-V ist flexibel und man kann schnell neue Produkte entwickeln.“

Laurent entschied sich für die Produktionskosten. Es ist sehr wichtig, NRE unter Kontrolle zu halten, da nicht viele Leute 100 Millionen Teile bauen. Es gibt also mehr beteiligte Anbieter und eine komplizierte Lieferkette. Ein SoC ist komplex, aber Chiplets sind noch schlimmer.

Rob wies auf Heterogenitäten wie das Hinzufügen von Chiplets für HF und Analog, einen optionalen Beschleuniger usw. hin. Dies eröffnet potenziell neue Märkte.

Calista fragte weiter, wo wir in der Automobilbranche stehen.

Aniket wies darauf hin, dass die Automobilindustrie sehr konservativ sei und nun aggressiv gegenüber Plattformen vorgehe, die von Low-End-Autos zu High-End-Autos skaliert werden könnten. Bei Chiplets hat sich niemand wirklich Gedanken über die funktionale Sicherheit gemacht.

Rob ging in die Luft- und Raumfahrt (nicht ganz in die Automobilindustrie) und diskutierte, dass es normalerweise ein festes physisches Volumen gibt, das vor Jahrzehnten definiert wurde. Es ist schwierig, die Dinge unterzubringen.

Laurent: Automobilunternehmen sind die ultimativen Katalogkäufer und Chiplets ermöglichen es ihnen, das Beste aus den Bereichen KI, Radar, Infotainment usw. herauszuholen.

Wie bringen Sie die Software zum Laufen?

Rob: Wenn man das System klein macht, ist das in Ordnung. Aber der Einkauf im Autokatalog macht es schwieriger.

Aniket: Verwandte Aussage: „Wenn Sie es hinzufügen, werden wir es nicht verwenden.“ Automotive-Software-Stacks werden RISC-V in 5 Jahren unterstützen, was schnell ist. Arm brauchte 15 Jahre, um dorthin zu gelangen.

F: Was brauchen wir für die Konnektivität?

Laurent: Es ist sehr komplex, vor allem wenn die Leute Chiplets kaufen. PHYs verschiedener Anbieter können interoperabel sein. Jeder ist von UCIe begeistert. Die Menschen wollen Standards, die dafür sorgen, dass Chiplets besser passen.

Aniket beklagte, dass es keine Standard-Designabläufe für Chiplets gebe. Ein großer Mangel an Standards.

Rob ist der Meinung, dass wir einen Standard-Flow entwickeln können, aber mit verschiedenen Chiplets wollen wir keine unterschiedlichen Design-Flows.

F: Wo sehen Sie die Dinge in 3-5 Jahren?

Rob: Wir werden mit anderen Dingen weiterkommen

„Katalogeinkauf hängt möglicherweise von den Automobilherstellern ab. Es wird große Anstrengungen der Industrie erfordern. Alle heterogenen Dinge werden länger dauern.

Aniket sagte, dass Chiplets zunächst im Rechenzentrum und dann im Automobilbereich eingesetzt werden. Aber die erste Welle wird ein einzelner Anbieter sein.

Zusammenfassung

Dies ist eine Kombination aus den Aussagen der Teilnehmer und meiner eigenen Meinung.

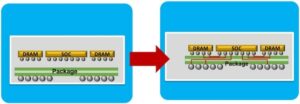

Ich denke, dass Chiplet-basierte RISC-V-Designs vorerst eine Einzelunternehmensarbeit sein werden (mit Ausnahme vielleicht von High-Bandwidth-Memory (HBM). Es ist zu komplex, Designs mit mehreren Chiplets verschiedener Unternehmen, Interposern, zu bauen und das Netzwerk, um sie alle zu verbinden, normalerweise bekannt als RDL.

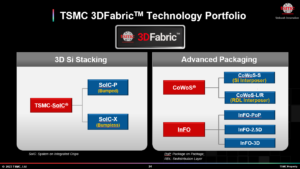

Die Designs werden in absehbarer Zukunft 2.5D und nicht echtes 3D sein (wobei die Chips übereinander gestapelt sind und mit Siliziumdurchkontaktierungen oder TSVs kommunizieren).

Die Automobilindustrie hat ihre eigenen Herausforderungen, insbesondere die Gewährleistung, dass Chiplet-basierte Designs in einer Umgebung mit vielen Vibrationen zuverlässig sind. Dies erfordert umfangreiche Tests. Ein weiteres Problem ist die Gewährleistung der funktionalen Sicherheit in einer Multi-Die-Umgebung.

UCIe ist vielversprechend und basiert in gewisser Weise auf PCIe. PCIe-Unternehmen sorgten durch Plugfests für Zuverlässigkeit. Ich sehe keine Möglichkeit, die UCIe-Interoperabilität in Chiplets durch einen ähnlichen Mechanismus wirtschaftlich sicherzustellen.

Schließlich gibt es zusätzlich zu den technischen Herausforderungen auch kommerzielle Herausforderungen, wenn wir das Nirvana erreichen wollen, Chiplets von der Stange zu kaufen und sie zu angemessenen Kosten zu Systemen zusammenzubauen. Die größte Herausforderung besteht darin, wer für die Bestände an Chiplets aufkommt und diese verwaltet. Wenn alle Chiplets nach Bedarf hergestellt werden müssen, gehen viele Vorteile einer schnellen Zykluszeit verloren.

Aber RISC-V-Chiplets in Form von Multi-Die-Designs auf 2.5D-Interposern, die von einem einzigen Unternehmen gebaut werden, sind sicherlich schnell auf dem Vormarsch.

Lesen Sie auch:

NoCs bieten Architekten Flexibilität beim System-in-RISC-V-Design

Durch die Paarung von RISC-V-Kernen mit NoCs werden SoC-Protokolle miteinander verbunden

Teile diesen Beitrag über:

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :hast

- :Ist

- :nicht

- :Wo

- $UP

- 100M

- 15 Jahre

- 15%

- 167

- 200

- 300

- 3d

- a

- Fähig

- LiveBuzz

- Beschleuniger

- präsentieren

- hinzufügen

- Hinzufügen

- Zusatz

- Vorteilen

- Luft- und Raumfahrt

- aggressiv

- vor

- AI

- Alle

- entlang

- ebenfalls

- unter

- an

- und

- angekündigt

- Ein anderer

- jedem

- Architekten

- SIND

- ARM

- um

- AS

- fragen

- fragen

- At

- Automobilindustrie

- Hintergrund

- basierend

- BE

- Sein

- BESTE

- Besser

- Big

- Größte

- Bit

- beide

- bauen

- Building

- erbaut

- aber

- by

- namens

- CAN

- Autos

- Katalog

- CEO

- sicherlich

- Kette

- challenges

- Herausforderungen

- billig

- Farbe

- Kombination

- Vereinigung

- wie die

- Kommen

- kommerziell

- mit uns kommunizieren,

- Unternehmen

- Unternehmen

- Komplex

- kompliziert

- Vernetz Dich

- Konnektivität

- konservativ

- betrachtet

- Kontext

- Smartgeräte App

- gurren

- Kosten

- Kosten

- Kunde

- Zyklus

- Datacenter

- Jahrzehnte

- definiert

- liefert

- Abhängig

- hängt

- Design

- Entwerfen

- Designs

- Sterben

- anders

- diskutiert

- Diskussion

- Distinguished

- do

- Dabei

- Nicht

- jeder

- Früher

- Anstrengung

- Ende

- Entwicklung

- gewährleisten

- gesichert

- Gewährleistung

- Arbeitsumfeld

- insbesondere

- jedermann

- Außer

- umfangreiche

- FAST

- Ende

- Vorname

- passen

- fixiert

- Flexibilität

- flexibel

- Fluss

- Fließt

- Aussichten für

- absehbar

- unten stehende Formular

- für

- funktional

- weiter

- Zukunft

- bekommen

- ABSICHT

- hart

- Schwerer

- Haben

- mit

- GUTE

- Hohe Leistungsfähigkeit

- HEISS

- Ultraschall

- HTTPS

- i

- if

- wichtig

- in

- Energiegewinnung

- International

- Flexible Kommunikation

- interoperabel

- in

- Inventar

- beteiligt

- IP

- Problem

- IT

- SEINE

- jpg

- Scharf

- Behalten

- Wissen

- bekannt

- Mangel

- Nachname

- lassen

- Gefällt mir

- länger

- verloren

- Los

- Sneaker

- um

- MACHT

- Management

- hergestellt

- viele

- viele Leute

- Markt

- Märkte

- max-width

- Kann..

- vielleicht

- me

- Mechanismus

- Monolithisch

- mehr

- mehrere

- my

- Need

- Netzwerk

- Neutral

- Neu

- nicht

- nichts

- jetzt an

- of

- on

- On-Demand

- EINEM

- öffnet

- Meinungen

- or

- Andere

- besitzen

- Tafel

- Podiumsdiskussion

- Teilnehmer

- besondere

- Teile

- AUFMERKSAMKEIT

- Personen

- vielleicht

- physikalisch

- Plattformen

- Plato

- Datenintelligenz von Plato

- PlatoData

- Mappe

- Post

- möglicherweise

- wahrscheinlich

- Prozessor

- Produkt

- Produktmanagement

- Produktion

- Produkte

- aussichtsreich

- Protokolle

- die

- Kauf

- setzen

- Frage

- ganz

- Radar

- Lesen Sie mehr

- wirklich

- vernünftig

- kürzlich

- bezogene

- Zuverlässigkeit

- zuverlässig

- erfordern

- Zimmer

- Führen Sie

- Sicherheit

- Said

- Skalieren

- sehen

- Sitzung

- kompensieren

- Shoppers

- Shopping

- ähnlich

- da

- Single

- klein

- So

- Software

- etwas

- spezifisch

- gestapelt

- Stacks

- Standard

- Normen

- Erklärung

- Gipfel

- liefern

- Supply Chain

- Support

- System

- Systeme und Techniken

- Nehmen

- sprechen

- Technische

- Testen

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Sie

- dann

- Dort.

- vom Nutzer definierten

- think

- Thinks

- fehlen uns die Worte.

- Durch

- Krawatten

- Zeit

- zu

- auch

- nahm

- Top

- Themen

- was immer dies auch sein sollte.

- letzte

- für

- Aktualisierung

- -

- gewöhnlich

- Wert

- Verkäufer

- Anbieter

- sehr

- Volumen

- vp

- wollen

- wurde

- Wave

- we

- ging

- waren

- Was

- wann

- welche

- WHO

- werden wir

- mit

- schlimmer

- Jahr

- U

- Zephyrnet