Beim Betrieb moderner CPU-Geräte werden 80 bis 90 % des Energieverbrauchs und der Zeitverzögerungen durch die Datenübertragung zwischen der CPU und dem Off-Chip-Speicher verursacht. Um dieses Leistungsproblem auszuräumen, fügen Entwickler ihren CPUs zusätzlichen On-Chip-Speicher hinzu. Traditionell war SRAM der am weitesten verbreitete On-Chip-CPU-Speichertyp. Leider ist SRAM derzeit auf eine Größe von Hunderten von Megabyte beschränkt. Diese Einschränkung des On-Chip-Speichers reicht für Spitzenanwendungen möglicherweise nicht aus.

Zukünftige CPU-Anwendungen, wie etwa die Programmierung von KI-Sprachmodellen und die Bildverarbeitung für 8K-UHD-Videos, erfordern eine I/O-Speicherzugriffsbandbreite im Bereich von 10 Terabyte/Sek. Um diese Bandbreitenanforderungen zu erfüllen, muss der On-Chip-CPU-Speicher größer als 1 Terabyte sein. Möglicherweise ist eine SRAM-Alternative erforderlich, um diese zukünftigen On-Chip-Speicheranforderungen zu erfüllen. Eine mögliche Lösung für dieses Problem wäre die Verwendung von Resistive Random Access Memory (ReRAM). [1,2,3]

Ein ReRAM-Gerät ist eine nichtflüchtige Speicherzelle, die Memristormaterialien enthält. Diese Materialien wirken als dielektrischer Isolator. Wenn eine ausreichend hohe Spannung angelegt wird, entsteht ein Leitungspfad. Zu den typischen Speichermaterialien, die als Memristoren verwendet werden, gehört HfO2,Ta2O5und TiO2. [4] Der Widerstandszustand der Speicherzelle kann mithilfe elektronischer Schaltkreise gelesen werden, um festzustellen, ob die Speicherzelle programmiert oder gelöscht ist, und so den Zustand des Speicherbits zu identifizieren. ReRAM-Speicherzellen können wie bei der 3D-NAND-Architektur vertikal gestapelt werden, um die Speicherdichte zu erhöhen.

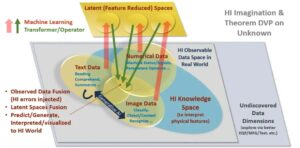

In diesem Artikel SEMulator3D Virtuelle Fertigung wird zur Prozesspfadfindung und Visualisierung potenzieller 3D-ReRAM-Architekturen verwendet. Wir werden den Zellwiderstand als Funktion der Speicherzellenform abschätzen, zusammen mit der Id-Vg-Leistung des eingebetteten Kanaltransistors in einem ReRAM-Gerät.

Ein 3D-ReRAM-Modell ist in Abbildung 1 dargestellt. Das Gerät verfügt über 64 Wortleitungsschichten (WL) mit Säulen, die in einem sechseckigen Abstand angeordnet sind. Die Wortleitungen bestehen aus abwechselnden Schichten metallischer Leiter und Oxiddielektrikum. Die Säulen werden durch die WL geätzt und dann wird eine dünne Schicht aus Gedächtnismaterial auf die Seitenwände der Säulen aufgebracht. Das Memory-Material wird von der Unterseite und der Oberseite der Säulen entfernt, so dass nur das Material an den Seitenwänden der Säule zurückbleibt. Anschließend werden die Säulen mit feuerfestem Metall und Wolfram gefüllt.

Unter den Array-Schichten befinden sich Kontakte und Metallverbindungen zu Source, Drain und Gates von Gate-Allround-Feldeffekttransistoren (GAA-FET). Der Transistor-Drain ist mit der Speicherarray-Säule verbunden und sorgt in Verbindung mit der WL-Schaltung für die Funktion jeder Speicherzelle.

Die Speicherzelle besteht aus zwei Metallelektroden: der metallischen Leiterwortleitung und einer feuerfesten Metallelektrode (Abbildung 2). Während der virtuellen Prozesssimulation dieses Geräts verwenden wir Prozessvariablen, um den Memristor einzustellen und zurückzusetzen. Eine absichtlich angelegte Spannung erzeugt mikroskopisch kleine Leiterbahnen, sogenannte leitende Filamente. Wenn elektrische Signale unterschiedlicher Polarität angelegt werden, bewegen sich die geladenen Ionen im Memristor, um den leitenden Faden zu bilden (einzustellen) oder aufzulösen (zurückzusetzen).

Der Widerstand des leitenden Filaments variiert bei unterschiedlichen Programmspannungen. Der Zustand mit niedrigem Widerstand liegt im Bereich von 10 kOhm (eingestellt) und der Zustand mit hohem Widerstand liegt im Bereich von 1 M Ohm (zurückgesetzt). [5] Wir haben ein virtuelles Modell entwickelt, um die Schaltwiderstände eines 3D-ReRAM-Geräts zu demonstrieren. Die Ergebnisse sind in Abbildung 3 dargestellt. Der hochohmige Zustand des Memristors ist etwa 100-mal höher als der niederohmige Zustand.

Anschließend wurde eine virtuelle Versuchsplanung (DOE) durchgeführt, um den Zusammenhang zwischen dem Widerstandsverhältnis der Speicherzelle und der Größe und Form der Speicherzelle besser zu verstehen. Die Variablen des Experiments waren Säulen-CD, WL-Dicke und Memristordicke. Die Analyse der DOE-Ergebnisse zeigt, dass die Säulen-CD und die Dicke des Memristors die signifikanteste Reaktion auslösten. Abbildung 4 zeigt ein Konturdiagramm des Speicherzellenwiderstandsverhältnisses im Vergleich zu diesen beiden Variablen. Bei hohen Werten für Säulenradius und Memristordicke kam es zu einer dreifachen Änderung des Speicherzellenwiderstands. Die Unterschiede in der Form der Speicherzelle im untersuchten Bereich wirken sich nicht auf die Fähigkeit aus, die Speicherzustände des Memristors zu lesen, könnten sich jedoch auf die Fähigkeit auswirken, Programmzustände in einem Gerät mit mehreren Bits pro Zelle zu erkennen.

Der Memristor kann mit einem Strom < 0.10 uA und einer Spannung < 0.5 V programmiert werden. Diese Spannungs- und Stromeinstellungen ermöglichen die einfache Integration von Memristoren (ReRAM-Speicher) als On-Chip-Speicher in fortschrittliche Logikgeräte. Die SEMulator3D-Gerätesimulation hat zuvor gezeigt, dass ein GAA-FET-Unterarray-Transistor in der Lage sein sollte, die Spannung und den Strom zu steuern, die für die Setz- und Rücksetzzustände einer Memristor-Speicherzelle erforderlich sind. [6]

Zwei Hauptprobleme moderner CPU-Geräte sind der Energieverbrauch und die Verzögerungszeit, die durch die Datenbewegung zwischen der CPU und dem Off-Chip-Speicher verursacht werden. Eine Vergrößerung des On-Chip-Speichers könnte diese Probleme lösen. In dieser Studie haben wir SEMulator3D verwendet, um die Integration einer SRAM-Alternative (ReRAM) für die CPU für den On-Chip-Speicher zu untersuchen. Wir haben ein virtuelles Modell verwendet, um Prozessschritte und potenzielle Layoutprobleme für einzelne Memristorzellen besser zu verstehen. Wir haben auch Studien durchgeführt, um die Setz- und Reset-Zustände des Memristors und die Auswirkung der Geräteabmessungen (Form und Größe der Speicherzelle) auf den Wortleitungswiderstand zu untersuchen. Wir haben hervorgehoben, dass der integrierte ReRAM-Speicher mit fortschrittlicher Logik integriert werden kann, indem ein elektrischer GAA-pFET-Transistorausgang zum Setzen und Zurücksetzen der Memristorzellen verwendet wird. Diese Ergebnisse bestätigen, dass Resistive Random Access Memory (ReRAM) eine vielversprechende Alternative zum integrierten SRAM-Speicher für zukünftige Logikanwendungen mit hoher Bandbreite ist.

Bibliographie

- Lanza, Mario (2014). „Ein Überblick über das Widerstandsschalten in High-k-Dielektrika: Eine nanoskalige Sichtweise unter Verwendung eines leitfähigen Rasterkraftmikroskops“. Materialien, Bd. 7, Ausgabe 3, S. 2155–2182, doi:10.3390/ma7032155.

- N. Sedghi, et al., „Die Rolle der Stickstoffdotierung in ALD Ta2O5 und ihr Einfluss auf die mehrstufige Zellschaltung in RRAM“, März 2017, Applied Physics Letters, DOI:10.1063/1.4978033

- Y. Bai, et al., „Study of Multi-level Characteristics for 3D Vertical Resistive Switching Memory“, Scientific Reports Band 4, Artikelnummer: 5780 (2014)

- Chen, YC, Sarkar, S., Gibbs, JG, Huang, Y., Lee, JC, Lin, CC und Lin, CH (2022). „Nanohelical-Shaped Dual-Functional Resistive Memory for Low Power Crossbar Array Application“, ACS Applied Engineering Materials, 1(1), 252-257.

- Y. Wu, et al., „Nanometer-Scale HfOx RRAM“, IEEE Electron Device Letters, Band: 34, Ausgabe: 8, August 2013), doi:10.1109/LED.2013.2265404

- V. Sreenivasulu et al., „Circuit Analysis and Optimization of GAA Nanowire FET Towards Low Power and High Switching“, 11. November 2021, Informatik, doi:10.1007/s12633-022-01777-6.

Brett Lowe

Brett Lowe ist Manager im Halbleiterprozess- und Integrationsteam bei Coventor, einem Lam-Forschungsunternehmen. Er ist seit mehr als 35 Jahren in der Entwicklung von Halbleitertechnologie tätig. Er begann seine Karriere bei Philips Semiconductors, wo er als Verfahrensingenieur in der Fertigung und Prozessentwicklung in den Bereichen Fotolithographie, Trockenätzung und Nassprozess tätig war. Anschließend verbrachte er acht Jahre bei Zilog und arbeitete an der Prozessentwicklung. Später wechselte Brett zu Micron Technology, wo er in der Entwicklung und Integration von DRAM- und 3D-NAND-Prozessen arbeitete. Bei Coventor liegt sein Schwerpunkt auf der Unterstützung der Kunden des Unternehmens bei ihren Anforderungen an die 3D-Halbleiterprozessmodellierung und Technologieentwicklung.

- SEO-gestützte Content- und PR-Distribution. Holen Sie sich noch heute Verstärkung.

- PlatoData.Network Vertikale generative KI. Motiviere dich selbst. Hier zugreifen.

- PlatoAiStream. Web3-Intelligenz. Wissen verstärkt. Hier zugreifen.

- PlatoESG. Kohlenstoff, CleanTech, Energie, Umwelt, Solar, Abfallwirtschaft. Hier zugreifen.

- PlatoHealth. Informationen zu Biotechnologie und klinischen Studien. Hier zugreifen.

- Quelle: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- :hast

- :Ist

- :nicht

- :Wo

- 1

- 10

- 100

- 10k

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35%

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- Fähigkeit

- Fähig

- Zugang

- über

- Handlung

- Hinzufügen

- Zusätzliche

- advanced

- beeinflussen

- AI

- AL

- Alle

- Alle Beiträge

- lindern

- erlauben

- entlang

- ebenfalls

- Alternative

- an

- Analyse

- und

- Anwendung

- Anwendungen

- angewandt

- ca.

- Architektur

- SIND

- Bereiche

- Feld

- Artikel

- AS

- At

- Atom-

- AUGUST

- b

- Bandbreite

- BE

- war

- begann

- Besser

- zwischen

- Bit

- Schwarz

- Boden

- braun

- bündeln

- aber

- by

- namens

- CAN

- Karriere

- verursacht

- CD

- Zelle

- Die Zellen

- Center

- Übernehmen

- Kanal

- Charakteristik

- berechnet

- vereint

- Unternehmen

- Unternehmen

- verglichen

- Computer

- Computerwissenschaften

- Hautpflegeprobleme

- Dirigent

- Schichtannahme

- Connects

- besteht

- Verbrauch

- Kontakte

- enthält

- Korrelation

- könnte

- CPU

- erstellen

- erstellt

- Cross

- Strom

- Zur Zeit

- Kunden

- Dunkel

- technische Daten

- verzögern

- Verzögerungen

- zeigen

- Synergie

- Dichte

- hinterlegt

- Design

- Designer

- Bestimmen

- entwickelt

- Entwicklung

- Entwicklung

- Gerät

- Geräte

- Unterschied

- Unterschiede

- anders

- Größe

- erkennen

- angezeigt

- Displays

- DOE

- abtropfen

- Zeichnung

- Antrieb

- trocknen

- im

- E & T

- jeder

- leicht

- Edge

- bewirken

- acht

- elektronisch

- eingebettet

- Energie

- Energy Consumption

- Ingenieur

- Entwicklung

- schätzen

- Äther (ETH)

- untersuchen

- ausgeführt

- Experiment

- Experimente

- FET

- Feld

- Abbildung

- gefüllt

- Setzen Sie mit Achtsamkeit

- Aussichten für

- Zwingen

- unten stehende Formular

- gebildet

- Formen

- gefunden

- für

- Funktion

- Zukunft

- Tor

- Gates

- Generation

- Graph

- mehr

- Grün

- Haben

- he

- GUTE

- höher

- Besondere

- seine

- HTTPS

- Huang

- hunderte

- ID

- Identifizierung

- IEEE

- if

- Image

- in

- das

- Erhöhung

- zunehmend

- zeigen

- Krankengymnastik

- beeinflussen

- innerhalb

- integrieren

- integriert

- Integration

- in

- untersuchen

- Problem

- SEINE

- beigetreten

- Lam

- Sprache

- später

- Schicht

- Lagen

- Layout

- führenden

- lernen

- Verlassen

- Lee

- links

- Gefällt mir

- Limitiert

- lin

- Logik

- Sneaker

- Maschine

- Maschinelles Lernen

- Dur

- Manager

- Herstellung

- März

- Mario

- Ihres Materials

- Materialien

- max-width

- Kann..

- Triff

- Memory

- Metall

- Mikron

- Modell

- Modellieren

- modern

- mehr

- vor allem warme

- schlauer bewegen

- Bewegung

- Need

- erforderlich

- weiter

- November

- Anzahl

- of

- OHM

- on

- EINEM

- einzige

- Betrieb

- Optimierung

- or

- Andere

- Möglichkeiten für das Ausgangssignal:

- Weg

- Pfade

- für

- Leistung

- Philips

- Physik

- Säule

- Säulen

- pink

- platziert

- Plato

- Datenintelligenz von Plato

- PlatoData

- Points

- Perspektive

- möglich

- BLOG-POSTS

- Potenzial

- Werkzeuge

- vorher

- Aufgabenstellung:

- Probleme

- Prozessdefinierung

- Verarbeitung

- Programm

- programmierten

- Programmierung

- aussichtsreich

- die

- zufällig

- Angebot

- Verhältnis

- Lesen Sie mehr

- Rot

- Entfernt

- Meldungen

- erfordern

- falls angefordert

- Voraussetzungen:

- Forschungsprojekte

- Robustes Design

- Antwort

- Die Ergebnisse

- Überprüfen

- Recht

- Rollen

- s

- Wissenschaft

- wissenschaftlich

- Abschnitt

- Halbleiter

- Halbleiter

- kompensieren

- Einstellungen

- Form

- sollte

- gezeigt

- Seite

- Signale

- signifikant

- Simulation

- Größe

- Lösung

- LÖSEN

- Quelle

- verbrachte

- gestapelt

- Bundesstaat

- Staaten

- Shritte

- Lagerung

- sucht

- Es wurden Studien

- Studie

- so

- Unterstützung

- Team

- Technologie

- Technische Entwicklung

- als

- zur Verbesserung der Gesundheitsgerechtigkeit

- Das

- Der Graph

- Die Quelle

- Der Staat

- ihr

- dann

- Dort.

- Diese

- fehlen uns die Worte.

- Durch

- So

- Zeit

- mal

- zeitliche Koordinierung

- zu

- Top

- gegenüber

- traditionell

- XNUMX

- tippe

- typisch

- für

- verstehen

- Unglücklicherweise

- Einheit

- -

- benutzt

- Verwendung von

- Werte

- verschiedene

- Gegen

- vertikal

- vertikal

- Video

- Anzeigen

- Assistent

- Visualisierung

- Stromspannung

- Volumen

- vs

- wurde

- we

- webp

- waren

- wann

- während

- Weiß

- weit

- werden wir

- mit

- gearbeitet

- arbeiten,

- würde

- wu

- Jahr

- Zephyrnet