I løbet af 2010-tiåret begyndte fordelene ved Moores lov at falde fra hinanden. Moores lov sagde, at transistortætheden fordobledes hvert andet år, og omkostningerne ved beregning ville falde med tilsvarende 50%. Ændringen i Moores lov skyldes øget designkompleksitet udviklingen af transistorstruktur fra plane enheder til Finfets. Finfets har brug for flere mønstre til litografi for at opnå enhedsdimensioner til under 20 nm noder.

I begyndelsen af dette årti er computerbehovet eksploderet, mest på grund af udbredelsen af datacentre og på grund af mængden af data, der genereres og behandles. Faktisk bruges anvendelsen af kunstig intelligens (AI) og teknikker som Machine Learning (ML) nu til at behandle stadigt stigende data og har ført til, at servere har øget deres computerkapacitet markant.

Servere har tilføjet mange flere CPU-kerner, har integreret større GPU'er, der udelukkende bruges til ML, bruges ikke længere til grafik, og har indlejret tilpassede ASIC AI-acceleratorer eller komplementær, FPGA-baseret AI-behandling. Tidlige AI-chipdesign blev implementeret ved hjælp af større monolitiske SoC'er, nogle af dem nåede størrelsesgrænsen pålagt af trådkorset, omkring 700 mm2.

På dette tidspunkt ser opdeling i en mindre SoC plus forskellige computer- og IO-chiplets ud til at være den rigtige løsning. Flere chipproducenter som Intel, AMD eller Xilinx har valgt denne mulighed for produkter, der skal i produktion. I den fremragende hvidbog fra The Linley Group, "Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small", blev det vist, at denne mulighed fører til bedre omkostninger sammenlignet med monolitiske SoC'er på grund af udbytteeffekten af større.

Den største indvirkning af denne tendens på IP-leverandører er for det meste på de sammenkoblingsfunktioner, der bruges til at forbinde SoC'er og chiplets. På dette tidspunkt (Q3 2021) er der flere protokoller, der bliver brugt, hvor industrien forsøger at opbygge formaliserede standarder for mange af dem.

Nuværende førende D2D-standarder inkluderer i) Advanced Interface Bus (AIB, AIB2) oprindeligt defineret af Intel, og har nu tilbudt royaltyfri brug, ii) High Bandwidth Memory (HBM), hvor DRAM-matricer er stablet oven på en silicium-interposer og er forbundet ved hjælp af TSV'er, iii) Open Domain-Specific Architecture (ODSA) undergruppe, en industrigruppe, har defineret to andre grænseflader, Bunch of Wires (BoW) og OpenHBI.

Heterogent chiplet-design giver os mulighed for at målrette mod forskellige applikationer eller markedssegmenter ved kun at ændre eller tilføje de relevante chiplets, mens resten af systemet holdes uændret. Nye udviklinger kunne lanceres hurtigere på markedet med væsentligt lavere investeringer, da redesign kun vil påvirke pakkesubstratet, der bruges til at huse chiplets.

For eksempel kan computerchiplet redesignes fra TSMC 5nm til TSMC 3nm for at integrere større L1-cache eller højere ydende CPU-kerner, mens resten af systemet holdes uændret. I den modsatte ende af spektret er det kun den chiplet, der integrerer SerDes, der kan redesignes til hurtigere hastigheder på nye procesknuder, der tilbyder mere IO-båndbredde for bedre markedspositionering.

Intel PVC er et perfekt eksempel på heterogen integration (forskellige funktionelle chiplet, CPU, switch osv.), som vi kunne kalde vertikal integration, når den samme chipproducent ejer de forskellige chiplet-komponenter (undtagen hukommelsesenheder).

Chipproducent, der udvikler SoC'er til avancerede applikationer, såsom HPC, datacenter, AI eller netværk, vil sandsynligvis være early adopters for chiplet-arkitekturer. Specifikke funktioner, såsom SRAM'er til større L3-cache eller AI-acceleratorer, enten Ethernet-, PCIe- eller CXL-standarder bør være den første grænsefladekandidat til chiplet-design.

Når disse tidlige brugere har demonstreret gyldigheden af heterogene chiplets, der udnytter flere forskellige forretningsmodeller, og naturligvis fremstillingsgennemførligheden for test og emballering, vil det skabe et økosystem, der er afgørende for at understøtte denne nye teknologi. På dette tidspunkt kan vi forvente en bredere markedsadoption, ikke kun for højtydende applikationer.

Vi kunne forestille os, at heterogene produkter kan gå længere, hvis en chipproducent vil lancere et system lavet af forskellige chiplets på markedet, der er målrettet computer- og IO-funktionalitet. Denne tilgang gør konvergens på en D2D-protokol obligatorisk, da en IP-leverandør, der tilbyder chiplets med en intern D2D-protokol, ikke er attraktiv for industrien.

En analogi til dette er SoC-bygningen i 2000'erne, hvor halvledervirksomheder går over til at integrere forskellige design-IP'er, der kommer fra forskellige kilder. IP-leverandørerne fra 2000'erne vil uundgåeligt blive chiplet-leverandørerne i 2020'erne. For visse funktioner, såsom avancerede SerDes eller komplekse protokoller, som PCIe, Ethernet eller CXL, har IP-leverandører den bedste knowhow til at implementere det på silicium.

For kompleks design-IP, selvom simuleringsverifikation er blevet kørt før afsendelse til kunder, skal leverandører validere IP'en på silicium for at garantere ydeevne. For digital IP kan funktionen implementeres i FPGA, fordi det er hurtigere og langt billigere end at lave en testchip. For mix-signal IP, som en SerDes-baseret PHY, vælger leverandørerne Test Chip (TC)-indstillingen, som gør det muligt for silicium at karakterisere IP'en i silicium, før de sendes til kunden.

Selvom en chiplet ikke blot er en TC, fordi den vil blive grundigt testet og kvalificeret, før den bruges i marken, er mængden af trinvis arbejde, der skal udføres af leverandøren for at udvikle en produktionschiplet, langt mindre. Med andre ord er IP-leverandøren den bedst positionerede til hurtigt at frigive en chiplet bygget fra sin egen IP og tilbyde den bedst mulige TTM og minimere risikoen.

Forretningsmodellen for heterogen integration går ind for, at forskellige chiplets fremstilles af den relevante IP-leverandør (f.eks. ARM til ARM-baserede CPU-chiplets, Si-Five til Risc-V-baserede computerchiplets og Alphawave til højhastigheds-SerDes-chiplets) siden de er ejer af Design IP.

Intet af dette forhindrer chipproducenter i at designe deres egne chiplets og kilde komplekse design-IP'er for at beskytte deres unikke arkitekturer eller implementere hjemmelavede sammenkoblinger. I lighed med SoC Design IP i 2000'erne, vil køb eller tag-beslutningen for chiplets blive vægtet mellem kernekompetencebeskyttelse og sourcing af ikke-differentierende funktioner.

Vi har set, at den historiske og moderne design-IP-forretningsvækst siden 2000'erne er blevet understøttet af en kontinuerlig anvendelse af ekstern sourcing. Begge modeller vil eksistere side om side (chiplet designet internt eller af en IP-leverandør), men historien har vist, at købsbeslutningen til sidst overtager fabrikatet.

Der er nu konsensus i branchen om, at et manisk fokus på at opnå Moores lov ikke længere er gyldigt for avancerede teknologiknuder, f.eks. 7nm og derunder. Chipintegration sker stadig, og flere transistorer tilføjes pr. mmXNUMX ved hver ny teknologisknude. Men prisen pr. transistor vokser også højere for hver ny node.

Chiplet-teknologi er et nøgleinitiativ til at drive øget integration til den primære SoC, mens ældre noder bruges til anden funktionalitet. Denne hybridstrategi reducerer både omkostningerne og designrisikoen forbundet med integration af anden Design IP direkte på hoved-SoC'en.

IPnest mener, at denne trend vil have to hovedeffekter i interface IP-branchen, den ene vil være den stærke vækst i D2D IP-indtægter snart (2021-2025), og den anden er skabelsen af det heterogene chiplet-marked for at øge high-end silicium IP-markedet.

Dette marked forventes at bestå af komplekse protokoller funktioner som PCIe, CXL eller Ethernet. IP-leverandører, der leverer interface-IP integreret i I/O SoC'er (USB, HDMI, DP, MIPI osv.), kan beslutte at levere I/O-chiplets i stedet.

De andre IP-kategorier, der er påvirket af denne revolution, vil være SRAM-hukommelseskompiler IP-leverandører til L3-cache. I sagens natur forventes cachestørrelsen at variere afhængigt af processoren. Ikke desto mindre kan design af L3-cache-chiplet være en måde for IP-leverandører at øge Design IP-indtægter ved at tilbyde en ny produkttype.

Ligeledes kan NVM IP-kategorien påvirkes positivt, da NVM IP ikke længere er integreret i SoC'er designet på avancerede procesknudepunkter. Det ville være en måde for NVM IP-leverandører at skabe ny forretning ved at tilbyde chiplets.

Vi tror, at FPGA- og AI-acceleratorchiplets vil være en ny indtægtskilde for ASSP-chipproducenter, men vi mener ikke, at de strengt taget kan rangeres som IP-leverandører.

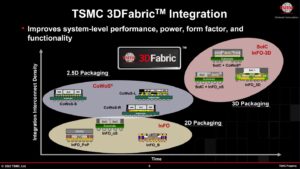

Hvis Interface IP-leverandører bliver store aktører i denne siliciumrevolution, vil siliciumstøberierne, der adresserer de mest avancerede noder som TSMC og Samsung, også spille en nøglerolle. Vi tror ikke, at støberier vil designe chiplets, men de kunne træffe beslutningen om at understøtte IP-leverandører og skubbe dem til at designe chiplets, der skal bruges med SoC'er i 3nm, som de gør i dag, når de understøtter avancerede IP-leverandører til at markedsføre deres avancerede SerDes så hård IP i 7nm og 5nm.

Intels nylige overgang til 3rd partsstøberier forventes også at udnytte tredjeparts IP'er, såvel som heterogen chiplet-adoption af halvleder-sværvægtere. I dette tilfælde er der ingen tvivl om, at Hyperscalars som Microsoft, Amazon og Google også vil vedtage chiplet-arkitekturer ... hvis de ikke går forud for Intel i chiplet-adoption.

By Erik Esteve (PhD.) Analytiker, Ejer IPnest

Del dette opslag via: Kilde: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- accelerator

- acceleratorer

- Vedtagelse

- Advanced Technology

- AI

- tillade

- Amazon

- AMD

- analytiker

- applikationer

- arkitektur

- ARM

- kunstig intelligens

- Kunstig intelligens (AI)

- ASIC

- BEDSTE

- bygge

- Bygning

- Bunch

- bus

- virksomhed

- forretningsmodel

- købe

- ringe

- Kapacitet

- lave om

- chip

- Chips

- kommer

- Virksomheder

- Compute

- computing

- Konsensus

- Omkostninger

- Kunder

- data

- leverer

- Design

- udvikle

- Enheder

- digital

- Tidligt

- tidlige adoptører

- økosystem

- etc.

- evolution

- Fornavn

- Fokus

- FPGA

- Gratis

- funktion

- GPU'er

- gruppe

- Dyrkning

- Vækst

- Høj

- historie

- hus

- HTTPS

- Hybrid

- KIMOs Succeshistorier

- Forøg

- industrien

- initiativ

- integration

- Intel

- Intelligens

- investering

- IP

- IT

- holde

- Nøgle

- lancere

- Lov

- førende

- læring

- Led

- Leverage

- LINK

- machine learning

- større

- maker

- Making

- Produktion

- Marked

- microsoft

- ML

- model

- netværk

- nyt produkt

- noder

- tilbyde

- tilbyde

- åbent

- Option

- Andet

- ejer

- emballage

- Papir

- ydeevne

- Produkt

- produktion

- Produkter

- beskytte

- beskyttelse

- priser

- redesign

- REST

- Risiko

- Kør

- Samsung

- halvleder

- Levering

- simulation

- Størrelse

- standarder

- Strategi

- support

- Kontakt

- systemet

- mål

- teknikker

- Teknologier

- prøve

- top

- us

- usb

- leverandører

- Verifikation

- hvidt papir

- ord

- Arbejde

- år

- Udbytte