与会专家:半导体工程公司与半导体工程公司产品管理集团总监 Frank Ferro 坐下来讨论日益异构系统中存储器的发展道路 Cadence公司;史蒂文·吴(Steven Woo),杰出发明家 Rambus公司; Jongsin Yun,内存技术专家 西门子EDA; Randy White,内存解决方案项目经理 Keysight; Frank Schirrmeister,解决方案和业务开发副总裁 动脉。以下是该谈话的摘录。此讨论的第一部分可以找到 此处.

![[从左到右]:Frank Ferro,Cadence;史蒂文·吴(Steven Woo),《Rambus》; Jongsin Yun,西门子 EDA;兰迪·怀特(Randy White),是德科技;和弗兰克·席尔迈斯特(Frank Schirrmeister),《阿特里斯》。](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[从左到右]:Frank Ferro,Cadence;史蒂文·吴(Steven Woo),《Rambus》; Jongsin Yun,西门子 EDA;兰迪·怀特(Randy White),是德科技;和 Frank Schirrmeister,Arteris

SE:当我们努力应对 AI/ML 和电力需求时,需要重新考虑哪些配置?我们会看到冯诺依曼架构的转变吗?

吴: 在系统架构方面,业界存在分歧。作为主要主力的传统应用程序(我们在基于 x86 的服务器上在云中运行)不会消失。数十年的软件已经被构建和发展,并且将依赖于该架构来良好运行。相比之下,AI/ML 是一个新类别。人们重新思考了架构并构建了非常特定领域的处理器。我们发现,大约三分之二的能量用于在处理器和 HBM 设备之间移动数据,而只有大约三分之一的能量用于实际访问 DRAM 内核中的位。现在,数据移动更具挑战性且成本更高。我们不会消除记忆。我们需要它,因为数据集越来越大。所以问题是,“前进的正确方法是什么?”关于堆栈有很多讨论。如果我们将内存直接放在处理器之上,它会为您做两件事。首先,当今的带宽受到海岸线或芯片周边的限制。这就是 I/O 所在的位置。但是,如果您将其直接堆叠在处理器之上,那么现在您可以利用芯片的整个区域进行分布式互连,并且您可以获得内存本身的更多带宽,并且它可以直接馈送到处理器。链路变得更短,电源效率可能会提高 5 到 6 倍。其次,由于与内存的更多区域阵列互连,您可以获得的带宽量也会增加几个整数倍。将这两件事结合起来可以提供更多带宽并提高能效。无论需求是什么,行业都会不断发展,这绝对是我们看到存储系统在未来开始发展以变得更加节能并提供更多带宽的一种方式。

铁: 当我在 2016 年左右第一次开始研究 HBM 时,一些更高级的客户询问它是否可以堆叠。他们已经研究如何将 DRAM 堆叠在顶部相当长一段时间了,因为这样做有明显的优势。从物理层来看,PHY 基本上可以忽略不计,从而节省了大量的功耗和效率。但现在你有一个 100W 的处理器,上面有一个内存。记忆无法承受热量。它可能是热链中最薄弱的环节,这带来了另一个挑战。好处是有的,但他们仍然需要弄清楚如何应对热气流。现在有更多的动力推动这种类型的架构向前发展,因为它确实确实在性能和功耗方面确实为您节省了总体成本,并且会提高您的计算效率。但必须应对一些物理设计挑战。正如史蒂夫所说,我们看到各种架构正在涌现。我完全同意 GPU/CPU 架构不会消失,它们仍然会占据主导地位。与此同时,地球上的每家公司都在努力想出更好的捕鼠器来实现他们的人工智能。我们看到片上 SRAM 和高带宽存储器的组合。由于功率的原因,近来关于如何在数据中心利用 LPDDR 的问题,LPDDR 引起了相当大的关注。我们甚至看到 GDDR 被用于一些人工智能推理应用程序以及所有旧的内存系统。他们现在正试图在占地面积上压缩尽可能多的 DDR5。我见过你能想到的所有架构,无论是 DDR、HBM、GDDR 还是其他架构。这取决于您的处理器核心的总体附加值,以及如何突破您的特定架构。与之配套的内存系统,因此您可以根据可用的情况来调整 CPU 和内存架构。

云: 另一个问题是非波动性。例如,如果人工智能必须处理运行基于物联网的人工智能之间的电源间隔,那么我们需要大量的电源关闭和打开,并且用于人工智能训练的所有这些信息都必须一次又一次地轮换。如果我们有某种类型的解决方案,可以将这些权重存储到芯片中,这样我们就不必总是为相同的权重来回移动,那么这将节省大量电量,特别是对于基于物联网的人工智能而言。将有另一种解决方案来满足这些电力需求。

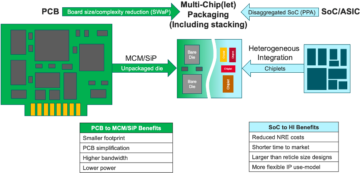

席尔梅斯特: 从 NoC 的角度来看,我发现令人着迷的是,您必须优化从处理器到 NoC 的这些路径,访问内存接口,控制器可能通过 UCIe 将一个小芯片传递到另一个小芯片,然后该小芯片将内存存储在它。这并不是说冯·诺依曼架构已经消亡。但现在有很多变化,具体取决于您想要计算的工作负载。它们需要放在记忆的背景下考虑,而记忆只是一方面。从数据本地获取数据的地方,它在这个 DRAM 中是如何排列的?我们正在研究所有这些事情,例如内存的性能分析,然后优化其上的系统架构。它激发了新架构的大量创新,这是我在大学学习冯·诺依曼时从未想到的。在极端的另一端,你有网格之类的东西。现在有很多介于两者之间的架构需要考虑,并且它是由内存带宽、计算能力等驱动的,而不是以相同的速度增长。

白色: 目前存在一种涉及分解计算或分布式计算的趋势,这意味着架构师需要拥有更多可用的工具。内存层次结构已扩展。其中包括可用于闪存和 DRAM 的语义以及 CXL 和不同的混合存储器。数据中心的一个并行应用是汽车。汽车领域始终采用 ECU(电子控制单元)来计算传感器。我对它如何演变为数据中心感到着迷。快进到今天,我们有了分布式计算节点,称为域控制器。这是同一件事。它试图解决这样的问题:也许功率并不是那么大的问题,因为计算机的规模没有那么大,但延迟对于汽车来说肯定是一个大问题。 ADAS 需要超高带宽,您需要进行不同的权衡。然后你会有更多的机械传感器,但数据中心也有类似的限制。您拥有不需要低延迟的冷存储,然后您还有其他高带宽应用程序。架构师的工具和选项发生了多大的变化,这真是令人着迷。该行业在应对方面做得非常好,我们所有人都提供了进入市场的各种解决方案。

SE:内存设计工具是如何演变的?

席尔梅斯特: 当我在 90 年代开始使用第一批芯片时,最常用的系统工具是 Excel。从那时起,我一直希望它能够在我们在系统级、内存、带宽分析等方面所做的事情在某一时刻崩溃。这对我的团队影响很大。在当时,这是非常先进的东西。但就兰迪的观点而言,现在某些复杂的事物需要以一定的保真度进行模拟,而以前如果没有计算,这是不可能实现的。举个例子,假设 DRAM 访问存在一定的延迟可能会导致错误的架构决策,并可能导致芯片上数据传输架构的设计错误。反面也是如此。如果你总是假设最坏的情况,那么你就会过度设计架构。让工具执行 DRAM 和性能分析,并为控制器提供适当的模型,使架构师能够模拟所有这些,这是一个令人着迷的环境。我从 90 年代开始就希望 Excel 可能会在某一时刻打破作为一个系统级工具实际上可能会实现,因为某些动态影响您无法再在 Excel 中执行,因为您需要将它们模拟出来 - 特别是当您引入具有 PHY 特性的芯片到芯片接口,然后是链路层时诸如所有检查一切是否正确以及可能重新发送数据之类的特征。不进行这些模拟将导致架构次优。

铁: 我们所做的大多数评估的第一步是为他们提供内存测试平台,以开始查看 DRAM 效率。这是一个巨大的进步,即使是像运行本地工具来进行 DRAM 模拟这样简单的事情,然后进入全面的模拟。我们看到越来越多的客户要求这种类型的模拟。确保您的 DRAM 效率高达 90 左右是任何评估中非常重要的第一步。

吴: 全系统仿真工具兴起的部分原因是 DRAM 变得更加复杂。现在,即使在酒吧中使用 Excel 等简单工具来处理某些复杂的工作负载也非常困难。如果您查看 90 年代 DRAM 的数据表,这些数据表大约有 40 页。现在它们有数百页。这只是说明了为了获得高带宽而需要的设备的复杂性。再加上内存是系统成本以及与处理器性能相关的带宽和延迟的驱动因素。它也是功率的重要驱动因素,因此您现在确实需要在更详细的级别进行模拟。就工具流程而言,系统架构师明白内存是一个巨大的驱动因素。因此,这些工具需要更加复杂,并且需要与其他工具很好地接口,以便系统架构师能够全面了解正在发生的情况,尤其是内存如何影响系统。

云: 随着我们进入人工智能时代,使用了大量的多核系统,但我们不知道哪些数据去了哪里。它还与芯片更加并行。内存的大小要大很多。如果我们使用ChatGPT类型的AI,那么模型的数据处理需要大约350MB的数据,这对于一个权重来说是一个巨大的数据量,而实际的输入/输出要大得多。所需数据量的增加意味着存在许多我们以前从未见过的概率效应。查看与如此大的内存量相关的所有错误是一项极具挑战性的测试。 ECC 随处可见,甚至在 SRAM 中,传统上不使用 ECC,但现在它在最大的系统中非常常见。对所有这些进行测试非常具有挑战性,需要 EDA 解决方案的支持来测试所有这些不同的条件。

SE:工程团队每天面临哪些挑战?

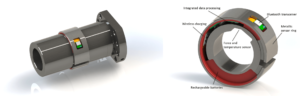

白色: 在任何一天,你都会在实验室找到我。我卷起袖子,双手弄脏,拨弄电线、焊接等等。我对硅后验证思考了很多。我们讨论了早期的模拟和片上工具——BiST,以及类似的东西。最终,在发货之前,我们想要进行某种形式的系统验证或设备级测试。我们讨论了如何克服记忆墙。我们将内存、HBM 等东西放在一起。如果我们回顾一下封装技术的发展,我们会从含铅封装开始。它们对信号完整性不太有利。几十年后,我们转向优化信号完整性,例如球栅阵列 (BGA)。我们无法访问它,这意味着您无法测试它。因此,我们提出了称为设备中介层(BGA 中介层)的概念,这使我们能够夹入一个特殊的夹具来路由信号。然后我们可以将它连接到测试设备。快进到今天,现在我们有了 HBM 和小芯片。如何将我的夹具夹在硅中介层之间?我们不能,这就是斗争。这是一个让我彻夜难眠的挑战。我们如何在 OEM 或系统客户无法获得 90% 效率的情况下进行现场故障分析。链接中存在更多错误,无法正确初始化,并且训练不起作用。是系统完整性问题吗?

席尔梅斯特: 您是否宁愿通过虚拟界面在家中完成此操作,而不是步行到实验室?答案难道不是在芯片中内置更多的分析功能吗?借助小芯片,我们可以进一步集成一切。将烙铁放入其中并不是真正的选择,因此需要有一种进行片上分析的方法。 NoC 也有同样的问题。人们查看 NoC,然后发送数据,然后数据就消失了。我们需要将分析放在那里,以便人们可以进行调试,并将其扩展到制造水平,以便您最终可以在家工作并基于芯片分析完成这一切。

铁: 特别是对于高带宽内存,您无法实际进入其中。当我们获得 PHY 许可时,我们还拥有一款与之配套的产品,因此您可以关注这 1,024 位中的每一位。您可以从该工具开始读取和写入 DRAM,因此您无需亲自进入那里。我喜欢插入器的想法。在测试过程中,我们确实将一些引脚从中介层中取出,这是您在系统中无法做到的。进入这些 3D 系统确实是一个挑战。即使从设计工具流程的角度来看,似乎大多数公司都在许多 2.5D 工具上执行自己的单独流程。我们开始整合一种更标准化的方法来构建 2.5D 系统,从信号完整性、电源到整个流程。

白色: 随着芯片上的进展,我希望我们仍然可以保持相同的精度水平。我是 UCIe 外形规格合规小组的成员。我正在研究如何表征一个已知的良好模具,即黄金模具。最终,这将花费更多的时间,但我们将在所需测试的性能和准确性以及内置的灵活性之间找到一个折中的办法。

席尔梅斯特: 如果我研究小芯片及其在更开放的生产环境中的采用,测试是使其正常工作的更大挑战之一。如果我是一家大公司并且我控制它的各个方面,那么我可以适当地限制事情,以便测试等变得可行。如果我想谈谈 UCIe 的口号,即 UCI 与 PCI 只有一个字母的距离,并且我想象,从制造的角度来看,UCIe 组装的未来将变得像今天 PC 中的 PCI 插槽一样,那么测试方面确实是非常重要的。具有挑战性的。我们需要找到解决方案。还有很多工作要做。

相关文章

内存的未来 (上述圆形的第 1 部分)

从解决热和功率问题的尝试到 CXL 和 UCIe 的作用,未来为存储器带来了许多机遇。

- :具有

- :是

- :不是

- :在哪里

- $UP

- 1

- 2016

- 3d

- 40

- a

- 关于

- 以上

- ACCESS

- 访问

- 实际

- 通

- ADA

- 加

- 地址

- 采用

- 高级

- 优点

- 优点

- 再次

- AI

- 人工智能培训

- AI / ML

- 所有类型

- 允许

- 允许

- 还

- 时刻

- 量

- an

- 分析

- 分析

- 和

- 另一个

- 回答

- 任何

- 再

- 分析数据

- 应用领域

- 应用领域

- 适当

- 建筑师

- 架构

- 保健

- 国家 / 地区

- 围绕

- 安排

- 排列

- AS

- 问

- 方面

- 方面

- 组装

- 承担

- At

- 尝试

- 汽车

- 可使用

- 远离

- 背部

- 坏

- 球

- 带宽

- 酒吧

- 基于

- 基本上

- 基础

- BE

- 因为

- 成为

- 成为

- 很

- before

- 作为

- 好处

- 最佳

- 更好

- 之间

- 大

- 大

- 位

- 午休

- 带来

- 建立

- 建

- 商业

- 业务发展

- 但是

- by

- Cadence公司

- 被称为

- 来了

- CAN

- 可以得到

- 能力

- 案件

- Center

- 一定

- 当然

- 链

- 挑战

- 挑战

- 挑战

- 特点

- 特点

- 检查

- 芯片

- 碎屑

- 程

- 清除

- 云端技术

- 冷

- 冷库

- 组合

- 如何

- 未来

- 相当常见

- 公司

- 公司

- 复杂

- 复杂

- 符合

- 复杂

- 计算

- 电脑

- 计算

- 概念

- 条件

- 分享链接

- 考虑

- 约束

- 上下文

- 对比

- 控制

- 调节器

- 谈话

- 核心

- 正确

- 价格

- 可以

- 情侣

- 中央处理器

- 创建

- 顾客

- 合作伙伴

- data

- 数据中心

- 数据集

- 天

- 日复一日

- 一年中的

- 死

- 处理

- 几十年

- 决定

- 无疑

- 需求

- 根据

- 依靠

- 设计

- 设计

- 详细

- 研发支持

- 设备

- 死

- 不同

- 难

- 直接

- 副总经理

- 讨论

- 处理

- 杰出的

- 分布

- 分布式计算

- do

- 不

- 不会

- 做

- 域

- 优势

- 完成

- 别

- 向下

- 驱动

- 司机

- ,我们将参加

- 动态

- 早

- 影响

- 效率

- 高效

- 电子

- 结束

- 能源

- 工程师

- 整个

- 环境

- 设备

- 时代

- 故障

- 特别

- 醚(ETH)

- 评估

- 评价

- 甚至

- 终于

- 所有的

- 一切

- 到处

- 进化

- 发展

- 进化

- 演变

- 例子

- Excel

- 扩大

- 昂贵

- 扩展

- 极端

- 非常

- 眼部彩妆

- 面部彩妆

- 事实

- 因素

- 失败

- 迷人

- 高效率

- 可行

- 同伴

- 保真度

- 部分

- 数字

- 终于

- 找到最适合您的地方

- 姓氏:

- Flash

- 高度灵活

- 翻动

- 流

- 如下

- Footprint

- 针对

- 申请

- 向前

- 向前

- 发现

- 坦率

- 止

- ,

- 进一步

- 未来

- 得到

- 越来越

- 给

- 特定

- 全球

- Go

- GOES

- 去

- 金色的

- 走了

- 非常好

- 好工作

- 得到了

- 格

- 团队

- 成长

- 民政事务总署

- 处理

- 手

- 快乐

- 有

- 有

- 头

- 帮助

- 等级制度

- 高

- 持有

- 主页

- 抱有希望

- 创新中心

- How To

- HTML

- HTTPS

- 巨大

- 数百

- 杂交种

- i

- 主意

- if

- 想像

- 影响

- 影响

- 重要

- 改善

- in

- 刺激

- 包括

- 不正确

- 增加

- 日益

- 个人

- 行业中的应用:

- 信息

- 創新

- 内

- 整合

- 诚信

- 互连

- 接口

- 成

- 涉及

- 问题

- 问题

- IT

- 它的

- 本身

- 工作

- 只是

- 知道

- 已知

- 实验室

- 大

- 大

- 最大

- 潜伏

- 后来

- 层

- 铅

- 学习

- 邮件

- Level

- 执照

- 喜欢

- 有限

- 友情链接

- 链接

- 本地

- 看

- 寻找

- 占地

- 很多

- 低

- 保持

- 使

- 制作

- 颠覆性技术

- 经理

- 制造业

- 许多

- 市场

- 最大宽度

- 也许

- me

- 手段

- 意思

- 机械

- 中等

- 回忆

- 内存

- 可能

- 模型

- 更多

- 最先进的

- 移动

- 移动

- 运动

- 移动

- 许多

- my

- 需求

- 需要

- 决不要

- 全新

- 夜

- 节点

- 现在

- 数

- of

- 折扣

- 老

- on

- 一

- 仅由

- 打开

- 机会

- 优化

- 优化

- 追求项目的积极优化

- 附加选项

- 附加选项

- or

- 秩序

- 其他名称

- 其它

- 输出

- 最划算

- 克服

- 己

- 包

- 包装

- 网页

- 并行

- 部分

- 特别

- 通过

- 径

- 路径

- PC

- 员工

- 演出

- 性能

- 透视

- 的

- 物理

- 射梢类

- 行星

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 点

- 可能

- 可能

- 功率

- 总统

- 先前

- 大概

- 市场问题

- 处理器

- 处理器

- 产品

- 产品管理

- 生产

- 曲目

- 正确

- 正确

- 提供

- 放

- 题

- 相当

- 提高

- 率

- 宁

- 阅读

- 真

- 有关

- 依靠

- 必须

- 需要

- 解决

- 回应

- 导致

- 摆脱

- 右

- 上升

- 角色

- 滚

- 运行

- 运行

- 同

- 保存

- 储

- 说

- 鳞片

- 其次

- 看到

- 看到

- 似乎

- 看到

- 语义

- 半导体

- 提交

- 传感器

- 传感器

- 服务器

- 几个

- 表

- 转移

- 船

- 侧

- 双方

- Siemens

- 信号

- 信号

- 硅

- 类似

- 简易

- 模拟

- 模拟

- 自

- 单

- 尺寸

- 插槽

- So

- 软件

- 方案,

- 解决方案

- 一些

- 极致

- 说

- 特别

- 花费

- 挤

- 堆

- 堆叠

- 堆叠

- 标准化

- 立场

- 开始

- 开始

- 开始

- 步

- Steve (史蒂夫)

- 史蒂芬

- 仍

- 存储

- 商店

- 奋斗

- 这样

- 支持

- 肯定

- 系统

- 产品

- 表

- 采取

- 谈论

- 队

- 技术专家

- 专业技术

- 条款

- test

- 测试

- 测试

- 比

- 这

- 未来

- 其

- 他们

- 然后

- 那里。

- 热

- 博曼

- 他们

- 事

- 事

- 认为

- 第三

- Free Introduction

- 那些

- 思想

- 通过

- 次

- 至

- 今晚

- 一起

- 工具

- 工具

- 最佳

- 完全

- 权衡

- 传统

- 传统

- 产品培训

- 运输

- 趋势

- true

- 试图

- 二

- 三分之二

- 类型

- 理解

- 单位

- 大学

- us

- 使用

- 用过的

- 运用

- 验证

- 折扣值

- 变化

- 各个

- 非常

- 副

- 副总裁

- 查看

- 在线会议

- 的

- 步行

- 墙

- 想

- 是

- 方法..

- we

- 重量

- 井

- 为

- 什么是

- 任何

- ,尤其是

- 是否

- 这

- 而

- 白色

- 全

- 为什么

- 将

- 也完全不需要

- 魆

- 工作

- 在家里工作

- 加工

- 最差

- 写作

- 您

- 您一站式解决方案

- 和风网