器件尺寸缩小的趋势不断增加输入/输出(I/O)和电路密度的需求,这些需求鼓励开发具有细铜(Cu)再分布层的高密度扇出(HDFO)封装(RDL)。对于高性能移动和网络应用,HDFO 是一种新兴解决方案,因为与晶圆级扇出 (WLFO) 等其他封装类型相比,HDFO 可以应用更激进的设计规则。 HDFO 允许在一个封装中组装多个芯片,并且大多数精细的 Cu RDL 用于互连芯片。此外,HDFO可根据应用进行晶圆级和基板级制作,在封装尺寸方面具有更好的可扩展性。

HDFO 中的 Cu RDL 嵌入了聚酰亚胺 (PI) 等介电层,可在芯片之间或从基板到芯片传输信号。当电流流过 Cu RDL 时,由于焦耳热的产生,热量会积聚在导体中。这种热量积累会导致性能下降。随着精细Cu RDL结构所需的电流密度和焦耳加热温度不断增加,它被视为HDFO封装性能的重要因素。

由于精细铜 RDL 应具有高可靠性性能,最近推出了各种 RDL 结构,例如嵌入式迹线 RDL (ETR) 和覆盖无机电介质的铜迹线,以实现高密度互连和可靠性性能 [1, 2]。也进行了许多关于评估优良 Cu RDL 可靠性性能的研究。

电迁移(EM)是评价Cu RDL可靠性和电特性的项目之一。 EM 是一种扩散控制机制,通过电子流导致导体中的金属原子逐渐移动。金属原子的这种质量传输导致在导体的阴极侧形成空隙并在阳极侧形成小丘。这些过程会导致电气连续性丧失。电迁移行为受到特征尺寸、应力条件、电子流方向和测试结构(例如接头冶金)的影响。在 Cu RDL EM 测试中,导体中不仅存在电子流力,还存在热梯度,因此 EM 退化归因于电势和热能 [3]。

利用 EM 测试结果,可以预测特定现场条件下的最大允许电流密度或寿命。在加速条件下执行的 EM 测试以及基于 EM 实验数据的外推可用于估计用例的当前值或生命周期值。在计算方面,广泛使用詹姆斯·布莱克 (James Black) 于 1969 年发表的布莱克模型。该模型中的一些因素是通过拟合威布尔和对数正态分布等故障分布模型来确定的。本文描述了 HDFO 封装中 ≤ 10 µm 的 Cu RDL 在各种电流和温度条件下的电磁特性和失效分析结果。此外,还提供了在工作温度和寿命的几种使用条件下估计的最大允许电流的增加比例。

HDFO 封装中的 Cu RDL 结构

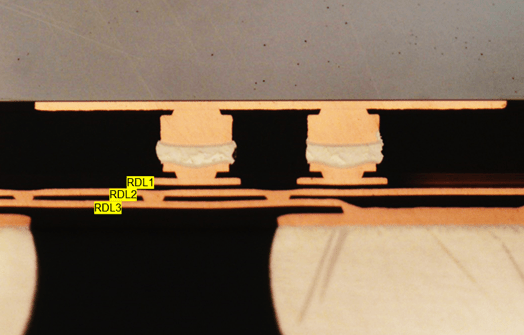

HDFO 包是为 Cu RDL EM 测试而制作的。封装体和芯片尺寸分别为 8.5 mm x 8.5 mm 和 5.6 mm x 5.6 mm。 HDFO TV 具有多层 RDL 结构,其中三层厚度为 3 µm,每个 RDL 都有 Ti/Cu 种子层。此外,聚酰亚胺被用作围绕精细 Cu RDL 的介电材料。 RDL 结构上方有铜柱凸块、芯片和模具。模具类型是包覆模具,覆盖模具顶部。 Cu RDL的总体结构如图1所示。

图 1:带有三个 RDL 的 HDFO 测试车辆的横截面视图。

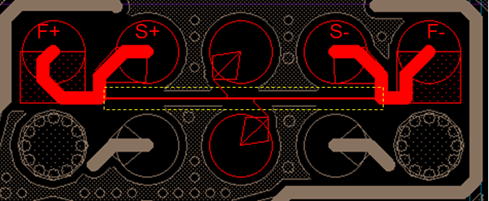

设计并测试了长度为 1000 µm、宽度为 2 µm 和 10 µm 的直 Cu RDL。 Cu RDL 是 HDFO 中的最底层 (RDL3)。四个球栅阵列 (BGA) 球连接到测试的 Cu RDL,用于电流强制和电压感测。图 2 显示了经过测试的 RDL 设计的示意图。

图 2:用于电迁移测试的 Cu RDL 设计。 “F”和“S”分别表示电流强制和电压感测。

电迁移测试

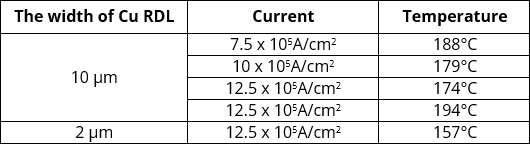

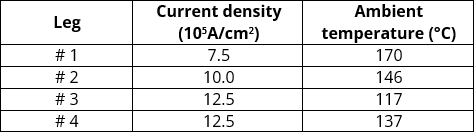

HDFO 测试车辆表面安装到测试板上,用于与 EM 测试系统进行电气连接,并且表面安装后不施加第二次底部填充。 10 µm 宽度的 Cu RDL 在 7.5、10 和 12.5 x 10 的直流电流下受到应力5安/厘米2 温度分别为174°C、179°C、188°C和194°C。 2 µm 宽度 Cu RDL EM 测试也在直流 12.5 x 10 下进行了测试5安/厘米2 温度为157°C。测试条件如表1所示。测试温度被认为是Cu RDL处的温度。因此,通过补偿焦耳加热量来设定烘箱温度。在每个应力电流下进行焦耳热校准,因为它取决于电流密度的大小。

为了校准焦耳热,在低电流和应力电流条件下在多个温度下测量电阻。低电流被视为产生非焦耳热的条件。电阻值随着环境温度的升高而增加,利用低电流条件下的电阻变化行为来获得热电阻系数(TCR)值。在几种温度条件下测量电阻后,使用TCR和低电流条件与测试电流条件之间的电阻差来计算焦耳热量。计算出的各试验电流条件下的焦耳加热温度和10μm宽度的Cu RDL处的温度如表2所示。

表 1:细线 Cu RDL EM 测试条件。

表 2:焦耳加热温度和 rdl 温度。细铜 RDL EM 测试进行了四种测试条件。

EM测试持续进行,直至电阻增加100%,并且确定用于计算最大允许电流的失效时间(TTF)的标准设置为电阻增加20%。如果所有结构都表现出非常相似的初始阻力,则已知阻力百分比增加的标准是最有效的。对于 0.7 µm 宽度的 Cu RDL,应力条件下的初始电阻为 0.8 至 10 欧姆,因此这些值看起来非常相似。在 EM 测试期间,使用 4 点测量技术测量 Cu RDL 的电阻。为了进行有意义的统计分析,测试样本的数量确定为18至20个。

除了光学显微镜之外,还使用聚焦离子束 (FIB)/场发射扫描电子显微镜 (FESEM) 进行故障分析,以了解电迁移测试期间的退化情况。除了顶视图图像分析之外,还通过镓 (Ga) 离子铣削对特定区域进行横截面,以观察 Cu 氧化和空隙导致的 Cu RDL 区域的减少。

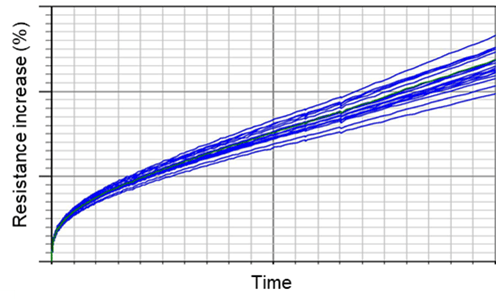

电阻变化行为

10 µm 宽度的 Cu RDL 在 EM 测试过程中的电阻增加行为如图 3 所示。电阻增加趋势可以分为两种不同的模式。初期电阻稳定增加,但达到一定电阻增加%后,电阻迅速发生变化。电阻增加两个阶段的原因是每个阶段主要发生的失效模式不同。

图3还显示了相同测试条件下不同温度条件下的不同寿命和失效时间(TTF)分布。据估计,相同条件下TTF分布的原因是由于每个Cu RDL的晶粒尺寸不同测试车辆之中。 Cu金属原子的扩散路径为晶界、材料界面和体金属,各扩散路径的活化能不同。由于晶界或材料界面的活化能低于块体金属的活化能,因此在 EM 过程中通过晶界或材料界面的扩散更占主导地位。因此,晶粒尺寸是决定电磁测试期间TTF的重要因素[4]。

如果电流密度较低7.5A/cm2,与高电流12.5A/cm相比,大多数样品表现出更低的电阻增加和更平滑的曲线2 如图3(c)所示。根据结果,预计这种低电流条件可能比高电流条件具有不太严重的故障模式,但高电流条件和低电流条件之间的故障模式看起来没有显着差异。在进一步的研究中,计划对电阻变化行为的步骤进行失效分析。

在相同电流密度条件(2×12.55安/厘米2)作为 10 µm 宽度的 Cu RDL 和较低的温度条件。 EM 测试期间电阻增加的绘图如图 4 所示。在这种情况下,即使在长达 10 Khrs 的长测试时间内,电阻变化行为也仅显示电阻稳定增加,这与 10 µm 宽度的 Cu RDL 情况不同。基于低温和高温条件下不同的电阻变化行为,怀疑高温和低温下的失效模式不相同。此外,预计 2μm 宽度 Cu RDL 的故障模式主要是由于电阻阶段稳定增加而发生的。

对于 10 µm 宽度的 Cu RDL,满足 20% 和 100% 电阻增加失效标准的单元数量如表 3 所示。所有测试单元均满足 20 小时内 8,000% 的失效标准,部分单元显示在 100 小时以下当测试时间为 10,000 小时时电阻增加百分比。由于故障单元的数量足以进行统计分析,因此 EM 测试在 10,000 小时时停止。此外,还确保了电阻增加 100% 的 EM 数据,因此可以根据各种故障标准计算最大电流容量。

图 3:10 次 EM 测试期间的电阻增加行为–微米 宽度RDL,12.5A/cm2 电流和 (a) 174°C 和 (b) 194°C 温度和 (c) 7.5A/cm2 和 188°C。

图 4:2 µm 宽度 RDL 的 EM 测试期间电阻增加行为。测试条件为电流密度12.5A/cm2 温度为157°C。

表3:10-不合格单位数量µ每种条件下 m 宽的 Cu RDL。

失效模式分析

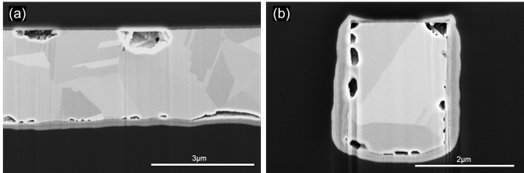

为了了解精细 Cu RDL EM 测试的失效机制,使用光学显微镜和 FIB/FESEM 观察顶部视图和横截面视图。图 5 显示了表面安装到测试板上后的 2 µm 和 10 µm 宽度的 Cu RDL。厚度和宽度与设计值吻合良好,Cu RDL处Cu与PI之间未出现表面不平整、空洞、分层等异常情况。如图5所示,确认了RDL中的晶粒尺寸发生变化。由于缺陷会影响电迁移性能,因此在进行 EM 测试之前应检查 Cu RDL 的质量。

图 5:表面安装后 Cu RDL 的 FIB/FESEM 图像:(a) 10 µm 和 (b) 2 µm 宽度。

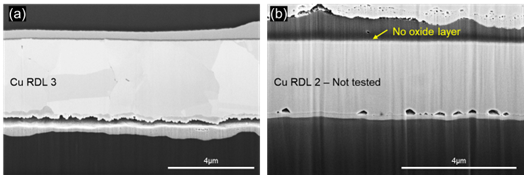

在 10 µm 宽度的 Cu RDL 的情况下,观察到各种失效模式,如图 6 所示。首先,在 Cu RDL 和钝化之间观察到分层和 Cu 氧化物,这导致 Cu RDL 面积减少,主要归因于阻力增加。 Cu RDL 面积的减少也导致 RDL 上的电流拥挤和更高的温度,并且 EM 退化也加速。在 EM 测试过程中,由于 Cu 原子的迁移而产生了空隙,而分层似乎是由于空隙沿着钝化层和 Cu RDL 之间的界面生长所致。电流密度指数值反映了空穴成核和生长之间哪种现象更占主导地位。 [5] 关于 Cu 氧化层和扩散到 PI 中,Cu 扩散似乎由于电子流或/和热梯度而加速,因为在 RDL2(未进行 EM 测试)下,Ti/Cu 籽晶层上没有氧化层作为阻挡层,如图6(b)所示。

在Cu RDL2 和PI 之间,仅观察到空隙和Cu 氧化层,这是由于热应力造成的。换句话说,在Cu RDL2处观察到的失效模式可以被视为长期高温存储(HTS)之一。

图 6:10×12.5 测试后 10 µm 宽度 Cu RDL 的光学显微镜和 FIB/FESEM 图像5A/cm2,174°C:(a) 在测试的 RDL3 处发生铜氧化和分层,(b) 在 RDL2 处 Ti/Cu 籽晶层上没有铜氧化(未进行 EM 测试)。

与 10 µm 宽度的 Cu RDL 不同,2 µm 宽度的 Cu RDL 没有出现 Cu RDL 和 PI 之间的分层,如图 7 所示。从受损程度较小的 2 µm 宽度 Cu RDL 来看,怀疑沿 Cu RDL 和 PI 之间界面的空洞生长导致了 10 µm 宽度 Cu RDL 中所示的分层。此外,人们认为这种分层可能是第二阶段阻力突然增加的主要因素。计划对更高电流条件下的2μm Cu RDL电迁移进行研究,以将Black方程中的失效模式和参数值与10μm Cu RDL电迁移结果进行比较。此外,预计通过进一步的研究确定每个阻力增加步骤的失效模式。

图 7:2×12.5 测试后 10 µm 宽度 Cu RDL 的光学显微镜和 FIB/FESEM 图像5安/厘米2,157°C:(a) RDL3 处的 Cu 氧化物空洞和 (b) Cu RDL3 上不同的 FIB 铣削轴。

焦耳热模拟

为了预测焦耳热量和失效位置,对 10 µm 宽度的 Cu RDL 进行了电热模拟。当铜迹线中的热量积累量不同时,不同位置的故障严重程度可能不同,因为电磁损伤不仅是由电子流力造成的,而且还由热梯度造成。如图8所示,HDFO电视和测试板的实际测试设计和结构反映在仿真模型中,并且还应用了每个结构的有效导热率。表 4 显示了基于烘箱温度和源电流的实验设计 (DOE)。烘箱温度可以被视为环境温度,并且焦耳加热量预计会随着源电流而变化。焦耳热模拟结果如图9所示。焦耳加热量模拟值与实验值相差1.3~4.2℃,两者值几乎相似。此外,局部温度最高的位置是连接金属焊盘的 Cu RDL 的中间,这与 EM 测试后的实际故障位置吻合良好。综上所述,焦耳热模拟结果在焦耳热量和失效位置方面与实际电磁测试结果吻合良好,有助于了解Cu RDL的电磁退化并预测失效位置。

图 8:10 µm 宽度 Cu RDL 的焦耳热仿真模型。

表 4:焦耳热模拟的 DOE。

图 9:焦耳热模拟结果:(a) 温度等值线和显示 12.5 x 10 下最高温度的点5安/厘米2 和137°C。 (b) 实验与模拟的焦耳加热量比较。

载流量计算

为了计算现场条件下的最大电流,广泛使用与电迁移测试中的失效时间相关的布莱克方程。

平均故障时间 = AJ-n 经验 (Ea/Kt) (1)

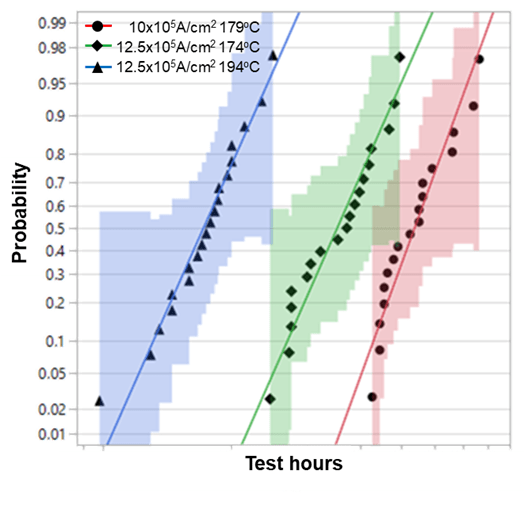

其中 MTTF 是平均故障时间,A 是经验常数,J 是电流密度,n 是电流密度指数,Ea 是活化能 (eV),K 是玻尔兹曼常数 (8.62×10-5 eV/K),T 是温度 (K)。用于确定布莱克方程的参数,如A、n和Ea,首先应进行统计分析。这非常重要,因为根据统计分析结果推断出较低的故障百分比可用于估计载流能力。描述电磁故障分布的两种典型方法是威布尔图和对数正态图。在分析金属线和通孔的失效时,首选对数正态分布,而当测试结构具有许多独立元素而导致失效(例如凸块和 BGA 球电迁移)时,通常使用威布尔模型。 [6] 由于在估计用例中的最大电流时拟合模型的选择可能至关重要,因此还进行了有关电迁移分布模型的研究[7]。本研究选择对数正态分布作为拟合模型,10μm宽度Cu RDL的对数正态分布图如图10所示。

最大载流量是在假设本次测试与用例之间的故障模式相同的情况下计算的,并且布莱克方程对于加速测试和现场条件都有效。用例中的最大电流容量使用公式 2 进行估计。在本例中,假设故障率为 0.1%,值 3.09 来自标准对数正态分布的 Z 分数。

J = [A exp (Ea/KT – 3.09σ)/TTF]-n (2)

其中 T 是使用条件温度,TTF 是使用案例中的预期寿命。对于 10 µm 宽度的 Cu RDL,Ea 和 n 分别确定为 0.74 和 1.88。一般来说,活化能和电流密度指数的值分别称为1和2。此外,电流密度指数值2和1通常分别被认为是空穴成核控制和生长控制。在此 EM 测试中,失效机制似乎是空洞成核和生长的混合,更具体地说,空洞成核似乎更占主导地位。如果由于试验条件恶劣或试验结构不同等原因导致失效机理与本研究不同,则估计值可能会有所不同。通常,当过应力条件通过焦耳热加速 EM 退化时,电流密度指数 (n) 值会增加。

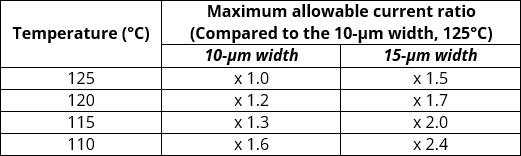

表5显示了与现场条件(寿命为100,000小时、占空比为100%、故障率为0.1%)下的值相比,估计的最大允许电流的增加率。比较的参考值是10℃时的125μm宽度,设置为1。当工作温度从125℃降低到110℃时,1.6μm和2.4μm的估计电流容量分别增加了10和15。宽度分别为 2 µm。失效准则影响最大允许电流值,因此选择设计的最大电流容量非常重要。如公式 (XNUMX) 所示,最大电流呈指数增加——与工作温度不成正比。当此电流估计值用于走线设计时,还应与 RDL 熔断电流一起考虑,因为计算出的最大允许电流与实际熔断电流之间存在交叉点。

图 10:10 µm 宽度 Cu RDL 失效概率图的对数正态分布。

表 5:几种现场条件下的最大允许电流 (mA) 比率。将 10°C 时 125 µm 宽度的值设置为 1。

结论

本研究报告了高密度扇出封装的细线 Cu RDL 的电迁移行为和失效模式。 Cu RDL 的测试宽度为 2 µm 和 10 µm,每种测试条件下由于电迁移降解而导致的电阻增加都不同。对于 10 µm 宽度的 Cu RDL,有两个阶段表现出不同的电阻变化行为。在第一步中,电阻稳步增加,预计空穴成核和生长是第一阶段主要发生的现象。第二步是阻力急剧增加的一段。此阶段仅在 10 µm 宽度的 Cu RDL 情况下出现,与低温测试的 2 µm 宽度 RDL 不同,Cu RDL 和 PI 之间出现分层,仅显示 Cu 氧化物和空隙。因此,可以得出结论,由于空隙生长而导致的分层是影响第二步电阻增加的主要因素。

电迁移后观察到的故障模式是由于铜氧化和空洞的产生/生长而导致铜面积减少。由于还观察到 Cu 迁移到 PI 中,因此似乎由于电子流或/和热梯度而加速。由于Cu RDL EM测试中需要考虑PI的热降解,因此进行了电热模拟来预测容易损坏的薄弱位置,结果与实际测试结果吻合良好。此外,模拟得到的焦耳热量与实际实验值几乎相似。

根据 10 µm 宽度的 Cu RDL EM 结果,完成 Black 方程,从而可以计算出最大载流能力。采用对数正态分布进行统计分析,Ea和电流密度指数的计算值分别为0.74和1.88。现场条件下估计的最大电流可用于设计 RDL,但需要考虑一些因素,例如实际熔断电流值以及 Ea 和电流密度指数对故障模式和测试条件的依赖性。

承认

这项研究得到了 Amkor Technology 全球研发中心的支持。作者要感谢研发工艺/材料研究团队为高密度扇出电视所做的准备。同时,感谢研发实验室的同事们配合进行DUT准备和故障分析。

参考资料

- S. Jin、W. Do、J. Jeong、H. Cha、Y. Jeong 和 J. Khim,“采用细间距嵌入式迹线 RDL 的基板硅晶圆集成扇出技术 (S-SWIFT) 封装”,2022 年 IEEE 第 72 届电子元件和技术会议 (ECTC),2022 年,第 1355-1361 页,doi:10.1109/ECTC51906.2022.00218。

- H. Kudo 等人,“用于先进细间距封装的增强型亚 2 微米级 Cu 再分布层的高电迁移电阻演示”,2017 年 IEEE CPMT 日本研讨会 (ICSJ),2017 年,第 5-8 页,doi :10.1109/ICSJ.2017.8240055。

- C.-L。梁,Y.-S。林,C.-L。 Kao, D. Tarng 等人,“采用细间距 2μm/2μm L/S Cu 再分配线的先进高密度扇出封装的电迁移可靠性”,IEEE Transactions on Components Packaging and Manufacturing Technology,第 1438-1445 页,2020。

- M. Rovitto,“三维集成技术互连中的电迁移可靠性问题”,未发表。

- M. Hauschildt 等人,“Cu 和 Cu(Mn) 互连中的电迁移早期失效空洞成核和生长现象”,2013 年 IEEE 国际可靠性物理研讨会 (IRPS),美国加利福尼亚州蒙特雷,2013 年,第 2C.1.1- 页2C.1.6,doi:10.1109/IRPS.2013.6531951。

- JEP154,“恒流和温度应力下焊料凸点电迁移特性指南”,JEDEC,2008 年。

- A. Basavalingappa、JM Passage、MY Shen 和 JR Lloyd,“电迁移:对数正态分布与威布尔分布”,2017 年 IEEE 国际综合可靠性研讨会 (IIRW),美国加利福尼亚州南太浩湖,2017 年,第 1-4 页,doi: 10.1109/IIRW.2017.8361224。

- :具有

- :是

- :不是

- :在哪里

- $UP

- 000

- 09

- 1

- 1.3

- 10

- 100

- 12

- 173

- 179

- 20

- 2008

- 2013

- 2017

- 2020

- 2022

- 212

- 521

- 7

- 8

- 820

- 9

- a

- 以上

- 突然

- 加速

- 加速

- 积累

- 积累

- 法案

- 活化

- 实际

- 增加

- 高级

- 影响

- 影响

- 后

- 侵略性

- AL

- 所有类型

- 允许

- 几乎

- 沿

- 还

- 环境

- 其中

- 量

- an

- 分析

- 分析

- 和

- 出现

- 应用领域

- 应用的

- 保健

- 国家 / 地区

- 地区

- 排列

- AS

- 组装

- 假定

- 假设

- At

- 作者

- 轴

- b

- 球

- 屏障

- 基于

- BE

- 光束

- 因为

- 很

- before

- 行为

- 更好

- 之间

- 黑色

- 板

- 身体

- 都

- 半身裙/裤

- 边界

- 但是

- by

- CA

- 计算

- 计算

- 计算

- 计算

- 来了

- CAN

- 容量

- 进行

- 携带

- 案件

- 原因

- Center

- 一定

- 更改

- 特点

- 图表

- 检查

- 芯片

- 碎屑

- 选择

- 同事

- 相比

- 对照

- 完成

- 组件

- 总结

- 流程条件

- 条件

- 进行

- 进行

- 电导率

- 导体

- 研讨会 首页

- CONFIRMED

- 已联繫

- 地都

- 注意事项

- 考虑

- 常数

- 持续

- 连续性

- 连续

- 贡献

- 铜

- 可以

- 覆盖

- 覆盖

- 标准

- 危急

- USB和Thunderbolt Cross

- 电流

- 曲线

- 周期

- 损伤

- data

- 下降

- 需求

- 密度

- 依赖

- 根据

- 依靠

- 描述

- 描述

- 设计

- 设计

- 确定

- 决心

- 确定

- 确定

- 研发支持

- 设备

- DID

- 死

- 差异

- 不同

- 扩散

- 直接

- 方向

- 分配

- 分

- do

- 美国能源部

- 优势

- 裁员

- 两

- ,我们将参加

- Ë&T

- EA

- 每

- 早

- 早期

- 容易

- 有效

- 电子

- 分子

- 嵌入式

- 新兴经济体的新市场。

- 发射

- 鼓励

- 能源

- 增强

- 评估

- 估计

- EV

- 评估

- 评估

- 甚至

- 预期

- 实验

- 试验

- 实验

- 成倍

- 因素

- 因素

- 失败

- 失败

- 专栏

- 少数

- 部分

- 数字

- 结束

- 姓氏:

- 配件

- 流

- 流动

- 重点

- 针对

- 力

- 强迫

- 训练

- 四

- 止

- 进一步

- 融合

- 其他咨询

- 通常

- 产生

- 产生

- 代

- 给

- 全球

- 逐步

- 格

- 事业发展

- 有

- 有帮助

- 高

- 更高

- 最高

- HTTPS

- 相同

- IEEE

- if

- 图片

- 图像分析

- 重要

- in

- 其他

- 增加

- 增加

- 增加

- 增加

- 独立

- 表示

- 影响

- 初始

- 集成

- 积分

- 互连

- 互连

- 接口

- 国际

- 成

- 介绍

- 问题

- IT

- 项目

- 它的

- 詹姆斯

- 日本

- 联合

- 已知

- 实验室

- 湖泊

- 层

- 层

- 信息

- 导致

- 长度

- 减

- Level

- 一生

- 喜欢

- 林

- Line

- 本地

- 圖書分館的位置

- 地点

- 长

- 长时间

- 看

- 看着

- 离

- 低

- 降低

- 制成

- 主要

- 主要

- 制造业

- 许多

- 质量

- 匹配

- 材料

- 最大宽度

- 最多

- 意味着

- 有意义的

- 测量

- 数据监测

- 机制

- 某些金属

- 方法

- 显微镜

- 显微镜

- 中间

- 移民

- 混合

- 联络号码

- 时尚

- 模型

- 模式

- 更多

- 最先进的

- 大多

- 运动

- 多

- 需要

- 工业网络

- 没有

- 数

- 观察

- 观察

- 获得

- 获得

- 发生

- 发生

- of

- OHM

- on

- 一

- 仅由

- 操作

- or

- 其他名称

- 输出

- 超过

- 最划算

- 包

- 包装

- 纸类

- 参数

- 通道

- 径

- 路径

- 百分比

- 性能

- 执行

- 现象

- 物理

- 支柱

- 沥青

- 计划

- 柏拉图

- 柏拉图数据智能

- 柏拉图数据

- 点

- 位置

- 可能

- 潜力

- 预测

- 首选

- 准备

- 呈现

- 可能性

- 过程

- 提供

- 出版

- 质量

- 相当

- R

- 研发

- 急速

- 率

- 比

- 达

- 原因

- 原因

- 最近

- 减少

- 参考

- 反映

- 反映

- 视

- 关于

- 有关

- 可靠性

- 报道

- 必须

- 研究

- 抵制

- 尊重

- 分别

- 导致

- 结果

- 成果

- 上升

- 定位、竞价/采购和分析/优化数字媒体采购,但算法只不过是解决问题的操作和规则。

- 同

- 满意

- 可扩展性

- 扫描

- 得分了

- 其次

- 部分

- 担保

- 种子

- 似乎

- 选择

- 选

- 集

- 几个

- 严重

- 严重

- 应该

- 显示

- 显示

- 显示

- 如图

- 作品

- 侧

- 信号

- 显著

- 硅

- 类似

- 模拟

- 自

- 尺寸

- 平滑

- So

- 方案,

- 一些

- 采购

- 南部

- 具体的

- 特别是

- 阶段

- 实习

- 标准

- 统计

- 稳步

- 步

- 步骤

- 存储

- 直

- 应力

- 结构体

- 结构

- 研究

- 学习

- 这样

- 足够

- 总结

- 支持

- 磁化面

- 周围

- 怀疑

- 专题研讨会

- 系统

- T

- 表

- 团队

- 技术

- 技术

- 专业技术

- 条款

- test

- 测试

- 测试

- 测试

- 比

- 感谢

- 谢谢

- 这

- 那里。

- 因此

- 热

- 博曼

- Free Introduction

- 三

- 三维

- 通过

- 次

- 至

- 也有

- 最佳

- 追踪

- 交易

- 转让

- 运输

- 趋势

- tv

- 二

- 类型

- 类型

- 普遍

- 下

- 理解

- 单位

- 直到

- 美国

- 使用

- 用例

- 用过的

- 有用

- 运用

- 平时

- 有效

- 折扣值

- 价值观

- 各个

- 汽车

- 车辆

- 与

- 非常

- 查看

- 电压

- W

- 是

- 网页

- 井

- 为

- ,尤其是

- 而

- 这

- WHO

- 广泛

- 中

- 话

- 车间

- 将

- X

- 和风网