تعمیر

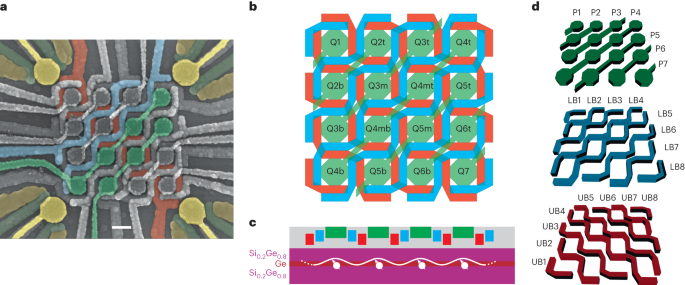

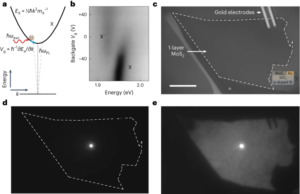

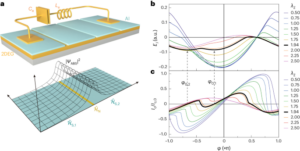

ڈیوائس کو Ge/SiGe heterostructure پر من گھڑت بنایا گیا ہے جہاں 16-nm-موٹا جرمینیم کوانٹم کنواں جس میں زیادہ سے زیادہ سوراخ کی نقل و حرکت 2.5 × 10 ہے۔5 cm2 V1- s1- سیمی کنڈکٹر/آکسائیڈ انٹرفیس کے نیچے 55 nm دفن ہے۔25,40. ہم 100 nm کے قطر کے ساتھ کوانٹم ڈاٹ پلنگر گیٹس ڈیزائن کرتے ہیں، اور 30 nm کی چوڑائی کے ساتھ کوانٹم ڈاٹس کو الگ کرنے والے بیریئر گیٹس۔ ڈیوائس کی فیبریکیشن ان اہم مراحل پر عمل کرتی ہے۔ سب سے پہلے، 30-nm-موٹی Pt اوہمک رابطوں کو الیکٹران-بیم لیتھوگرافی کے ذریعے نمونہ بنایا جاتا ہے، آکسیڈائزڈ Si کیپ پرت کو ہٹانے کے لیے ایک اینچنگ قدم کے بعد ہیٹرو سٹرکچر میں بخارات بن کر پھیل جاتے ہیں۔41,42. اس کے بعد تین پرت والے گیٹ اسٹیک کو ال کی ایٹم پرت کے جمع کو تبدیل کرکے گھڑا جاتا ہے۔2O3 ڈائی الیکٹرک فلم (7، 5 اور 5 nm کی موٹائی کے ساتھ) اور Ti/Pd دھاتی دروازوں کا بخارات (ہر جمع کے لیے بالترتیب 3/17، 3/27 اور 3/27 کی موٹائی کے ساتھ)۔ ڈائس کرنے کے بعد، ایک کراس بار سرنی کی میزبانی کرنے والی ایک چپ کو پھر نصب کیا جاتا ہے اور پرنٹ شدہ سرکٹ بورڈ پر تار باندھ دیا جاتا ہے۔ ڈائلیشن ریفریجریٹر میں ٹھنڈا ہونے سے پہلے، ہم نے اسکریننگ کے طریقہ کار کے مطابق 4 K ہیلیم غسل میں دو برائے نام ایک جیسی کراس بار ڈیوائسز کا تجربہ کیا۔38. دونوں ڈیوائسز نے مکمل گیٹس اور اوہامک رابطوں کی فعالیت کو ظاہر کیا، اور ان میں سے ایک کو ڈیلیشن ریفریجریٹر میں نصب کیا گیا تھا۔

تجرباتی سیٹ اپ

یہ تجربہ 10 mK کے بنیادی درجہ حرارت کے ساتھ Bluefors dilution ریفریجریٹر میں کیا جاتا ہے۔ کولمب چوٹی کے تجزیہ سے، ہم 138 ± 9 mK کا الیکٹران درجہ حرارت نکالتے ہیں، جسے ہم detuning لیور بازو کا اندازہ لگانے کے لیے استعمال کرتے ہیں (ضمیمہ انجیر۔ 12 اور 13)۔ ہم اندرون ملک بیٹری سے چلنے والے SPI ریک کا استعمال کرتے ہیں (https://qtwork.tudelft.nl/~mtiggelman/spi-rack/chassis.html) dc وولٹیجز کو سیٹ کرنے کے لیے، جب کہ ہم ایک Keysight M3202A صوابدیدی ویوفارم جنریٹر (AWG) استعمال کرتے ہیں تاکہ الٹرنیٹنگ کرنٹ راسٹرنگ پلس کو ایکسیل لائنز کے ذریعے لاگو کریں۔ ڈی سی اور الٹرنیٹنگ کرنٹ وولٹیج سگنلز پرنٹ شدہ سرکٹ بورڈ پر بائیس ٹیز کے ساتھ جوڑ کر گیٹس پر لگائے جاتے ہیں۔ ہر چارج سینسر NbTiN انڈکٹر سے جستی طور پر کچھ مائیکرو ہینریز کے انڈکٹنس کے ساتھ جڑا ہوتا ہے، جو ~ 100 میگاہرٹز کی گونج فریکوئنسی کے ساتھ ایک گونجنے والا ٹینک سرکٹ بناتا ہے۔ ہمارے تجربے میں، ہم نے چار میں سے صرف تین گونجیں دیکھی ہیں، غالباً ایک عیب دار انڈکٹر کی وجہ سے۔ مزید یہ کہ، کیونکہ دونوں گونجیں کافی حد تک اوورلیپ ہوتی ہیں، اس لیے ہم زیادہ تر ریفلوکومیٹری استعمال کرنے سے گریز کرتے ہیں (جب تک کہ متن میں واضح طور پر بیان نہ کیا گیا ہو) اور 50 kHz تک کی بینڈوتھ کے ساتھ تیز رفتار dc پیمائش کا استعمال کریں۔ چار ڈی سی سینسر کرنٹ کو وولٹیجز میں تبدیل کیا جاتا ہے، ان کو بڑھایا جاتا ہے اور ایک ساتھ چار چینل کیزائٹ M3102A ڈیجیٹائزر ماڈیول کے ذریعے 500 میگاسمپلز کے ساتھ پڑھا جاتا ہے۔1-. ڈیجیٹائزر ماڈیول اور کئی AWG ماڈیولز ایک Keysight M9019A پیریفرل کمپوننٹ انٹر کنیکٹ ایکسپریس ایکسٹینشن میں انسٹرومینٹیشن چیسس کے لیے مربوط ہیں۔ یہاں چارج استحکام کے خاکے عام طور پر 150 × 150 پکسل اسکین پر مشتمل ہوتے ہیں جس کی پیمائش کا وقت فی پکسل 50 μs ہوتا ہے۔ اس پورے مضمون میں، ہم Δg کا حوالہ دیتے ہیں۔i گیٹ جی کو AWG کی طرف سے فراہم کردہ ریمپ کی شناخت کرنے کے لیےi ایک مقررہ ڈی سی حوالہ وولٹیج کے حوالے سے۔ سگنل ٹو شور کے تناسب کو بڑھانے کے لیے، ہم ایک منٹ کے اندر اعلیٰ معیار کا نقشہ حاصل کرتے ہوئے، ایک ہی نقشے کو 5-50 بار اوسط کرتے ہیں۔

ٹیون اپ تفصیلات

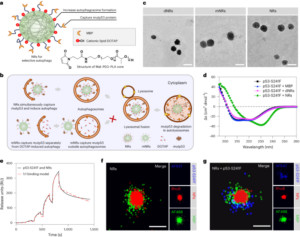

پورے تجربے کے دوران، ہم نے ڈیوائس کے تمام 16 کوانٹم ڈاٹس کو دو بار ٹیون کیا ہے۔ پہلی دوڑ میں، کراس بار کوانٹم ڈاٹس کو بہتر انداز میں دیکھنے اور ان کی خصوصیت کے لیے غیر ارادی کوانٹم ڈاٹس کی تعداد کو کم سے کم کرنے کے لیے گیٹ وولٹیجز کو بہتر بنایا گیا تھا (تصویر XNUMX)۔ 2 اور ضمنی تصویر۔ 14)۔ دوسری دوڑ میں، آوارہ نقطوں کو نظر انداز کر دیا گیا تاکہ کوانٹم ڈاٹ سرنی کو عالمی طاق قبضے کے نظام (تصویر XNUMX) میں ہم آہنگ کیا جا سکے۔ 3)۔ دو ٹیون اپ سائیکلوں کے درمیان، گیٹ وولٹیجز کو تھرمل طور پر ڈیوائس کو سائیکل کیے بغیر صفر پر ری سیٹ کر دیا گیا تھا۔ دو ٹیوننگ طریقہ کار میں پیروی کرنے والا پروٹوکول ایک جیسا تھا، لیکن پہلے سیشن میں حادثاتی کوانٹم ڈاٹس کو خالی کرنے کی ضرورت نے بعض دروازوں کی وولٹیج ونڈو میں کچھ پابندیاں عائد کر دیں۔ ٹیون اپ کے لیے ابتدائی گیٹ وولٹیج کی قدریں رکاوٹوں کے لیے -300 mV اور پلنگرز کے لیے -600 mV ہیں۔ ضمنی شکل میں۔ 15، ہم تصویر XNUMX میں دکھائی گئی پیمائش کے مقابلہ میں ڈی سی گیٹ وولٹیجز دکھاتے ہیں۔ 3، کراس بار سرنی کے ساتھ طاق چارج قبضے میں ٹیون کیا گیا ہے۔ اس نظام میں، ہم −1,660 ± 290 mV حاصل کرتے ہوئے ہر نقطے میں پہلے سوراخ والے وولٹیج کے آغاز میں تغیر کا بھی مطالعہ کرتے ہیں (ضمیمہ تصویر۔ 16)۔ مزید برآں، ہم صف کی یکسانیت کی سطح کے لیے میٹرک کے طور پر ٹرانزیشن لائن اسپیسنگ میں تغیر کو ~ 10–20% قرار دیتے ہیں (ضمیمہ انجیر۔ 17)43. ضمنی نوٹ 4 ان تغیرات کو مزید کم کرنے کی حکمت عملیوں پر تبادلہ خیال کرتا ہے۔

طاق چارج قبضے کو ہر کوانٹم ڈاٹ کو خالی کرکے ظاہر کیا جاتا ہے (ضمنی ویڈیوز 1-12)۔ تمام ڈیٹاسیٹس جو زیرِ نظر تصویر XNUMX۔ 3 اور اضافی ویڈیوز 1-12 اسی دن ایک ہی گیٹ وولٹیج کنفیگریشن میں لیے جاتے ہیں۔ پھر بھی، تمام نقشوں پر، کم سے کم وولٹیج کے فرق ہیں، سب سے بڑا vP6 میں 1 mV کا فرق ہے جو کہ Q1، Q2b اور Q2t قبضوں کو متاثر نہیں کرتا ہے (ضمنی جدول 1)۔ تجربے کے دوران، گیٹ UB8 ٹھیک سے کام نہیں کر رہا تھا، ممکنہ طور پر ٹوٹی ہوئی سیسہ کی وجہ سے۔ اس اثر کی تلافی کرنے اور P3t اور P5t نقطوں میں چارج لوڈنگ کو فعال کرنے کے لیے، ہم نے UB7 کو دوسرے UB گیٹس کے مقابلے کم وولٹیج پر سیٹ کیا۔ مزید برآں، LB1 کو نسبتاً زیادہ وولٹیج پر سیٹ کیا گیا ہے تاکہ کم وولٹیج پر LB1 اور P1 کے فین آؤٹ کے تحت حادثاتی کوانٹم ڈاٹس کی تشکیل کو کم کیا جا سکے۔ اس طرح کے حادثاتی کوانٹم ڈاٹ کی پہلی اضافی لائن ایک کمزور تعامل افقی لکیر کے طور پر نظر آتی ہے (تصویر XNUMX)۔ 3a).

ورچوئل میٹرکس

میٹرکس M کی طرف سے وضاحت (bf{overrightarrow{G}}=M بار bf{overrightarrow{{{{rm{v}}}}G}})ورچوئل گیٹس کے ساتھ (اوور رائٹ ایرو{{rm{v}}bf{G}}) اور اصل دروازے (اوور رائٹ ایرو{bf{G}}) ضمیمہ انجیر میں رنگین نقشے کے طور پر دکھایا گیا ہے۔ 3. تصویر میں پیش کردہ سرنگ کے جوڑے کے تجربات کے لیے۔ 4، ہم اضافی ورچوئل گیٹ سسٹمز کو ڈی ٹیوننگ وولٹیج e67 اور U67 کے آزادانہ کنٹرول حاصل کرنے کے ساتھ ساتھ ورچوئل رکاوٹوں کے ذریعے انٹرڈاٹ تعاملات کو استعمال کرتے ہیں۔6b7، ج6b7، ٹی6t7 اور جے6t7. SE_P کو SE پلنگر گیٹ کے طور پر بیان کرتے ہوئے، ہم لکھتے ہیں۔

$$begin{array}{rcl}left(begin{array}{c},{{mbox{P5}}},{{mbox{P6}}},{{mbox{P7}}},{{mbox{P0.04}}},{ {mbox{SE_P}}}، end{array}دائیں)&=&left(begin{array}{cc}1.2&-0.5 -0.9&0.492 0.9&0.08 -0.26&-67end{array}دائیں) بائیں (شروع{array}{c},{{mbox{e67}}}, {{mbox{U6}}}, end{array}دائیں) بائیں (شروع{array}{c},{{mbox{P7} }}، ,{{mbox{P5}}}،{{mbox{UB7}}}،{{mbox{LB1.28}}}،{{mbox{SE_P}}},end{array}دائیں)& =&بائیں }}}_{0.33{{{rm{t}}}}1.18} {{{rm{j}}}}}}} }_{0.72{{rm{t}}}}1}اختتام{سری}دائیں ) بائیں (begin{array}{c},{{mbox{P0}}},{{mbox{P0}}}, {{mbox{UB1}}}, {{mbox{LB0.15}}}، ,{{mbox{SE_P}}},end{array}دائیں)&=&left(begin{array}{cc}-0.01&-6 -7&-6 7&6 7&4 -7&-2.05end{array}دائیں) بائیں 0.97{{{rm{b}}}}1.18}end{array}دائیں) end{array}.$$

کوانٹم ڈاٹ کی شناخت

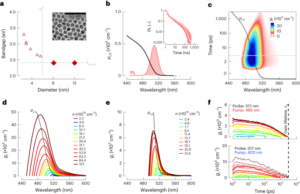

ٹرانزیشن لائنوں کے ایک سیٹ پر تمام رکاوٹی دروازوں کے کیپسیٹو کپلنگ حاصل کرنے کے لیے (تصویر XNUMX)۔ 2b)، ہم 112 چارج استحکام خاکوں کے سیٹ حاصل کرتے اور ان کا تجزیہ کرتے ہیں۔ ایک ہی چارج اسٹیبلٹی ڈایاگرام ہر بیریئر گیٹ کو اس کے موجودہ وولٹیج کے گرد 1 mV کے مراحل میں –3 سے 3 mV (یعنی 7 اسکینز × 16 رکاوٹوں) میں قدم رکھنے کے بعد لیا جاتا ہے۔ تمام کوانٹم ڈاٹ اسکیلز کو ان کی کل تعداد کے ساتھ لکیری طور پر شناخت کرنے کے لیے درکار چارج اسٹیبلٹی ڈایاگرامس کی تعداد۔ نقشوں کی تعداد پلنگرز اور بیریئر گیٹس کی تعداد کی پیداوار سے نکلتی ہے، یہ دونوں اس کی مربع جڑ کے طور پر پیمانہ ہوتے ہیں۔ ہم اس بات پر زور دیتے ہیں کہ انفرادی کنٹرول کے ساتھ ایک صف کو ہر ایک نقطے کا اندازہ لگانے کے لیے ایک لکیری تعداد میں چارج استحکام کے خاکوں کی بھی ضرورت ہوگی۔ تجزیہ میں، ہم سب سے پہلے ڈیٹا میں آہستہ آہستہ مختلف پس منظر کو گھٹاتے ہیں (اوپن سورس SciPy پیکیج ورژن 1.7.1 کے ndimage.gaussian.filter فنکشن کے ساتھ) اور پھر نقشے کے گریڈینٹ کا حساب لگاتے ہیں (ndimage.gaussian_gradient_magnitude فنکشن کے ساتھ) )۔ اس طرح کے دو جہتی نقشوں کے دیے گئے لائن کٹ کے لیے، ہم گاوسی فٹ فنکشن کا استعمال کرتے ہوئے چوٹی کی پوزیشن کو نکالتے ہیں۔ کراس کیپیسیٹینس کی وجہ سے، ٹرانزیشن لائن پوزیشنز 16 رکاوٹوں میں سے ہر ایک پر لکیری انحصار ظاہر کرتی ہیں، جسے ہم لکیری ڈھلوان کو نکال کر مقدار درست کرتے ہیں (ضمیمہ انجیر۔ 4)۔ زیادہ سے زیادہ قدر کو معمول پر لانے کے بعد، ان پیرامیٹرز کو capacitive couplings کا نام دیا جاتا ہے (λ) اور دو رکاوٹی تہوں کے گرڈ ڈھانچے کی وجہ سے، پہلی معلومات حاصل کی جاتی ہے کہ سوراخ کہاں سے شامل کیا گیا ہے/ہٹایا گیا ہے۔ کوانٹم ڈاٹ پوزیشنز کو نکالنے کے لیے، ہم وی یو بی (λوی یو بی) اور وی بی ایل (λوی ایل بی) گیٹس دو آزاد امکانی تقسیم کے طور پر۔ اس نقطہ نظر کے ساتھ، کا انضمام λوی یو بی (λوی ایل بی) vUB کے درمیانi (vLBk) اور وی یو بیj (vLBl) ایک 'امکان' لوٹاتا ہے pیو،(i,j) (pL،(k,l)ان کنٹرول لائنوں کے درمیان ڈاٹ تلاش کرنے کے لیے۔ نتیجے کے طور پر، ان چار رکاوٹوں سے محدود سائٹ میں مشترکہ امکان ان عناصر کی پیداوار سے دیا گیا ہے: w(i,j) ، (k,l) = pیو،(i,j) × pL،(k,l). ہم نوٹ کرتے ہیں کہ 16 احتمالات کا مجموعہ 1 لوٹاتا ہے۔ جیسا کہ پہلے ہی ایک اور کام میں مشاہدہ کیا گیا ہے۔32، ایک جرمینیم کوانٹم میں بیان کردہ ایک مخصوص کوانٹم ڈاٹ سے گیٹس کراس کپلنگ اچھی طرح سے خلا میں ایک سست فال آف کو ظاہر کرتے ہیں (یعنی> 100 nm کے نقطے کے فاصلے کے ساتھ دروازے اب بھی ڈاٹ کے ساتھ کافی حد تک کراس کپلنگ رکھتے ہیں)۔ اس کو گیٹس اور کوانٹم ڈاٹس (>60 nm) کے درمیان عمودی فاصلے سے منسوب کیا جا سکتا ہے، اور یہ سلیکون – میٹل – آکسائیڈ – سیمی کنڈکٹر ڈیوائسز کے تجربات کے برعکس ہے جہاں سخت چارج کی قید کی وجہ سے فال آف فوری طور پر ہوتا ہے۔ یہ پہلو وضاحت کرتا ہے کہ ہمارا امکان کیوں ہے۔ W شناخت شدہ کوانٹم ڈاٹ پر زیادہ سے زیادہ 0.25−0.50 تک پہنچ جاتا ہے۔

ٹنل کپلنگ کی تشخیص

سرنگ کے جوڑے کے نتائج کے تخمینے کے لیے تصویر XNUMX میں پیش کیا گیا ہے۔ 4، ہم نے پیمائش کا ایک خودکار طریقہ کار قائم کیا جو اس ترتیب کی پیروی کرتا ہے: (1) ہم مجازی رکاوٹوں کو دو جہتی نقشے پر عبور کرتے ہیں (t, j); (2) ہر رکاوٹ کی ترتیب پر، ہم ایک دو جہتی (e67, U67) چارج استحکام کا نقشہ لیتے ہیں (تصویر XNUMX)۔ 4b-g); (3) ہم نقشے کے موزوں طریقہ کار کے ذریعے چارج انٹرڈاٹ کی درست پوزیشن کی نشاندہی کرتے ہیں (ضمیمہ انجیر۔ 10)44; (4) ہم e67 اور U67 ورچوئل گیٹس پر (0, 0) dc آفسیٹ پر انٹر ڈاٹ کو سینٹر کرنے کے لیے چھوٹی ایڈجسٹمنٹ کرتے ہیں۔ (5) ہم پولرائزیشن لائن کی پیمائش ~ 0.1 kHz AWG ریمپس (تصویر XNUMX) کا استعمال کرتے ہوئے کرتے ہیں۔ 4c، h)۔ درست تجزیہ کے لیے، ہر پولرائزیشن لائن 150 μs فی پکسل کی پیمائش کے انضمام کا وقت استعمال کرتے ہوئے اوسطاً 50 نشانات کا نتیجہ ہے۔ اس طریقہ سے، چند گھنٹوں میں مکمل 30×30 نقشے لیے جاتے ہیں۔ ہم 138 mK کے الیکٹران کے درجہ حرارت اور ایک ڈیٹوننگ لیور بازو کو مدنظر رکھتے ہوئے نشانات کو فٹ کرتے ہیں۔ ({الفا }_{{epsilon }_{67}}) = 0.012(4) eV V1-، تھرمل طور پر وسیع پولرائزیشن لائن سے نکالا گیا (ضمیمہ انجیر۔ 13)۔ ہم مشاہدہ کرتے ہیں کہ نکالی گئی سرنگ کا جوڑا تقریباً بیریئر گیٹس کے کام کے طور پر ایک تیز رفتار رجحان کی پیروی کرتا ہے۔ ہم تصویر میں پیش کردہ ڈیٹا کو فٹ کرتے ہیں۔ 4e، j کے ساتھ (Atimes {rm{e}}^{-B{V}_{rm{g}}}) فنکشن، کہاں A ایک پیشوا ہے، B مؤثر رکاوٹ لیور بازو ہے اور Vg دروازے کا محور ہے. ہم تلاش کرتے ہیں کہ مؤثر رکاوٹ لیور بازو j6b7 اور t6b7 ہیں 0.007 ± 0.002 اور 0.021 ± 0.003 mV1-بالترتیب اسی طرح، j6t7 اور t6t7 ہیں 0.008 ± 0.001 اور 0.026 ± 0.003 mV1-بالترتیب اس سے ظاہر ہوتا ہے کہ حقیقی رکاوٹ LB7 عمودی اور افقی کپلنگ کو اسی طرح کنٹرول کرتی ہے۔ مجموعی طور پر، یہ نتائج بتاتے ہیں کہ UB گیٹس کی نچلی رکاوٹ LB گیٹس کی اوپری رکاوٹ کی تہہ سے ~ 3 گنا زیادہ موثر ہے۔ یہ اس کے مطابق ہے جو تصویر میں پایا جاتا ہے۔ 2b اور ضمنی تصویر۔ 5. ہم نوٹ کرتے ہیں کہ اس طرح کے کراس بار سرنی میں کوئبٹ آپریشنز کے لیے، یہ درحقیقت تمام 24 قریبی پڑوسیوں کی دو بیریئر ٹیون ایبلٹی کو مکمل طور پر خصوصیت اور کیلیبریٹ کرنا ضروری ہے۔ اس کام کو انجام دینے کے لیے ہمارے ہارڈ ویئر کے نفاذ کو مزید بہتر بنانے کی ضرورت ہے اور یہ اس کام کے دائرہ کار سے باہر ہے۔

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو ڈیٹا ڈاٹ نیٹ ورک ورٹیکل جنریٹو اے آئی۔ اپنے آپ کو بااختیار بنائیں۔ یہاں تک رسائی حاصل کریں۔

- پلیٹوآئ اسٹریم۔ ویب 3 انٹیلی جنس۔ علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- پلیٹو ای ایس جی۔ آٹوموٹو / ای وی، کاربن، کلین ٹیک، توانائی ، ماحولیات، شمسی، ویسٹ مینجمنٹ یہاں تک رسائی حاصل کریں۔

- پلیٹو ہیلتھ۔ بائیوٹیک اینڈ کلینیکل ٹرائلز انٹیلی جنس۔ یہاں تک رسائی حاصل کریں۔

- چارٹ پرائم۔ ChartPrime کے ساتھ اپنے ٹریڈنگ گیم کو بلند کریں۔ یہاں تک رسائی حاصل کریں۔

- بلاک آفسیٹس۔ ماحولیاتی آفسیٹ ملکیت کو جدید بنانا۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://www.nature.com/articles/s41565-023-01491-3

- : ہے

- : نہیں

- :کہاں

- $UP

- 1

- 10

- 100

- 116

- 150

- 16

- 2016

- 2018

- 2019

- 2020

- 2021

- 2023

- 23

- 24

- 25

- 30

- 32

- 40

- 50

- 500

- 60

- 67

- 7

- 9

- a

- درست

- حصول

- حاصل

- کے پار

- اصل

- اصل میں

- اس کے علاوہ

- ایڈیشنل

- اس کے علاوہ

- ایڈجسٹمنٹ

- پر اثر انداز

- کے بعد

- AL

- تمام

- پہلے ہی

- بھی

- ایک ساتھ

- Amplified

- an

- تجزیہ

- تجزیہ

- لنگر

- اور

- ایک اور

- اطلاقی

- کا اطلاق کریں

- نقطہ نظر

- تقریبا

- فن تعمیر

- کیا

- بازو

- ہتھیار

- ارد گرد

- لڑی

- مضمون

- AS

- پہلو

- At

- آٹومیٹڈ

- اوسط

- سے اجتناب

- محور

- پس منظر

- بینڈوڈتھ

- رکاوٹ

- راہ میں حائل رکاوٹیں

- بیس

- BE

- کیونکہ

- اس سے پہلے

- کیا جا رہا ہے

- نیچے

- بہتر

- کے درمیان

- سے پرے

- بورڈ

- دونوں

- ٹوٹ

- تعمیر

- لیکن

- by

- حساب

- کر سکتے ہیں

- ٹوپی

- کیپسیٹیو

- مرکز

- کچھ

- خصوصیات

- چارج

- chassis

- چپ

- کلک کریں

- مل کر

- تقابلی طور پر

- مقابلے میں

- جزو

- ترتیب

- منسلک

- غور کریں

- کافی

- پر غور

- متواتر

- روابط

- اس کے برعکس

- کنٹرول

- کنٹرول

- تبدیل

- ٹھنڈی

- موجودہ

- سائیکل

- ڈی سی

- اعداد و شمار

- ڈیٹاسیٹس

- دن

- کی وضاحت

- demonstrated,en

- کثافت

- انحصار

- ڈیزائن

- آلہ

- کے الات

- ڈایاگرام

- DID

- اختلافات

- تبدیلی

- دکھائیں

- ظاہر

- فاصلے

- تقسیم

- کرتا

- ڈاٹ

- دوگنا

- نیچے

- دو

- کے دوران

- e

- ای اینڈ ٹی

- ہر ایک

- اثر

- موثر

- عناصر

- پر زور

- کو چالو کرنے کے

- بڑھانے کے

- قائم

- تخمینہ

- Ether (ETH)

- EV

- تجربہ

- تجربات

- بیان کرتا ہے

- ظالمانہ

- ایکسپریس

- ملانے

- نکالنے

- فاسٹ

- چند

- انجیر

- اعداد و شمار

- فلم

- فلٹر

- مل

- پہلا

- فٹ

- فٹنگ

- مقرر

- پیچھے پیچھے

- کے بعد

- مندرجہ ذیل ہے

- کے لئے

- قیام

- ملا

- چار

- سے

- مکمل

- مکمل طور پر

- تقریب

- فعالیت

- مزید

- مزید برآں

- فرق

- گیٹس

- جنریٹر

- دی

- گلوبل

- گرڈ

- ہارڈ

- ہارڈ ویئر

- ہے

- ہیلیم

- یہاں

- اعلی معیار کی

- اعلی

- چھید

- سوراخ

- افقی

- ہوسٹنگ

- HOURS

- تاہم

- HTML

- HTTPS

- ہائبرڈ

- i

- ایک جیسے

- کی نشاندہی

- شناخت

- فوری طور پر

- نفاذ

- کو بہتر بنانے کے

- in

- آزاد

- اشارہ کرتے ہیں

- اشارہ کرتا ہے

- انفرادی

- معلومات

- اٹوٹ

- ضم

- انضمام

- بات چیت

- بات چیت

- میں

- IT

- میں

- بڑے

- سب سے بڑا

- پرت

- تہوں

- قیادت

- قیادت

- سطح

- لائن

- لائنوں

- LINK

- لوڈ کر رہا ہے

- لو

- کم

- مین

- انداز

- نقشہ

- نقشہ جات

- مواد

- میٹرکس

- زیادہ سے زیادہ

- پیمائش

- پیمائش

- پیمائش

- طریقہ

- میٹرک۔

- کم سے کم

- منٹ

- تخفیف کریں

- موبلٹی

- ماڈیول

- ماڈیولز

- زیادہ

- اس کے علاوہ

- زیادہ تر

- نامزد

- نےنو

- فطرت، قدرت

- ضروری

- ضرورت ہے

- شور

- تعداد

- مشاہدہ

- مشاہدہ

- حاصل

- حاصل کی

- حاصل کرنا

- قبضے

- قبضے

- of

- آفسیٹ

- on

- ایک

- صرف

- اوپن سورس

- آپریشنز

- اصلاح

- دیگر

- ہمارے

- باہر

- پیکج

- پیرامیٹرز

- چوٹی

- فی

- انجام دینے کے

- کارکردگی

- کارکردگی کا مظاہرہ

- پردیی

- دانہ

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوزیشن

- پوزیشنوں

- ممکنہ طور پر

- پیش

- امکان

- شاید

- طریقہ کار

- طریقہ کار

- پروسیسر

- مصنوعات

- مناسب طریقے سے

- پروٹوکول

- Q1

- کوانٹم

- کوانٹم ڈاٹ

- کوانٹم ڈاٹ

- کوانٹم ٹیکنالوجی

- کیوبیت

- کوئٹہ

- R

- ریمپ

- ریمپ

- رینج

- بلکہ

- تناسب

- پہنچتا ہے

- پڑھیں

- اصلی

- کو کم

- حکومت

- رشتہ دار

- ہٹا

- کی ضرورت

- ضرورت

- کی ضرورت ہے

- گونج

- احترام

- بالترتیب

- پابندی

- نتیجہ

- نتائج کی نمائش

- واپسی

- جڑ

- رن

- اسی

- توسیع پذیر

- پیمانے

- ترازو

- اسکین

- اسکین کرتا ہے

- گنجائش

- اسکریننگ

- دوسری

- سیمکولیٹر

- الگ کرنا

- تسلسل

- اجلاس

- مقرر

- سیٹ

- کئی

- ارے

- مشترکہ

- دکھایا گیا

- سگنل

- سلیکن

- اسی طرح

- اسی طرح

- بیک وقت

- ایک

- سائٹ

- ڈھال

- سست

- آہستہ آہستہ

- چھوٹے

- کچھ

- خلا

- مخصوص

- سپن

- سپن qubits

- چوک میں

- استحکام

- ڈھیر لگانا

- شروع

- نے کہا

- مرحلہ

- قدم رکھنا

- مراحل

- ابھی تک

- حکمت عملیوں

- آوارا

- ساخت

- مطالعہ

- کافی

- اس طرح

- سپر کنڈکٹیویٹی

- فراہم کی

- سسٹمز

- T

- ٹیبل

- لے لو

- لیا

- ٹینک

- ٹاسک

- ٹیکنالوجی

- تجربہ

- سے

- کہ

- ۔

- ان

- ان

- تو

- وہاں.

- یہ

- اس

- تین

- بھر میں

- وقت

- اوقات

- کرنے کے لئے

- کل

- منتقلی

- رجحان

- سرنگ

- دو

- عام طور پر

- کے تحت

- بنیادی

- استعمال کی شرائط

- کا استعمال کرتے ہوئے

- استعمال

- قیمت

- اقدار

- ورژن

- عمودی

- کی طرف سے

- ویڈیوز

- مجازی

- نظر

- وولٹیج

- W

- تھا

- we

- اچھا ہے

- ویلز

- تھے

- کیا

- کیا ہے

- جبکہ

- جس

- کیوں

- ونڈو

- وائر

- ساتھ

- کے اندر

- بغیر

- کام

- گا

- X

- زیفیرنیٹ

- صفر