تانبے کی مزاحمتی صلاحیت اس کے کرسٹل ڈھانچے، باطل حجم، اناج کی حدود اور مادی انٹرفیس کی مماثلت پر منحصر ہے، جو چھوٹے پیمانے پر زیادہ اہم ہو جاتا ہے۔ تانبے (Cu) تاروں کی تشکیل روایتی طور پر خندق اینچ کے عمل کا استعمال کرتے ہوئے کم-k سلکان ڈائی آکسائیڈ میں خندق پیٹرن کو اینچ کرکے، اور بعد میں خندق کو ڈیماسین بہاؤ کے ذریعے Cu سے بھر کر کیا جاتا ہے۔ بدقسمتی سے، یہ طریقہ اہم اناج کی حدود اور voids کے ساتھ کثیر کرسٹل ڈھانچے تیار کرتا ہے، جو کیو تار کی مزاحمت کو بڑھاتا ہے۔ اس عمل میں ایک انتہائی مزاحم TaN لائنر مواد کا بھی استعمال کیا جاتا ہے تاکہ ڈیماسین اینیلنگ کے عمل کے دوران Cu پھیلاؤ کو روکا جا سکے۔

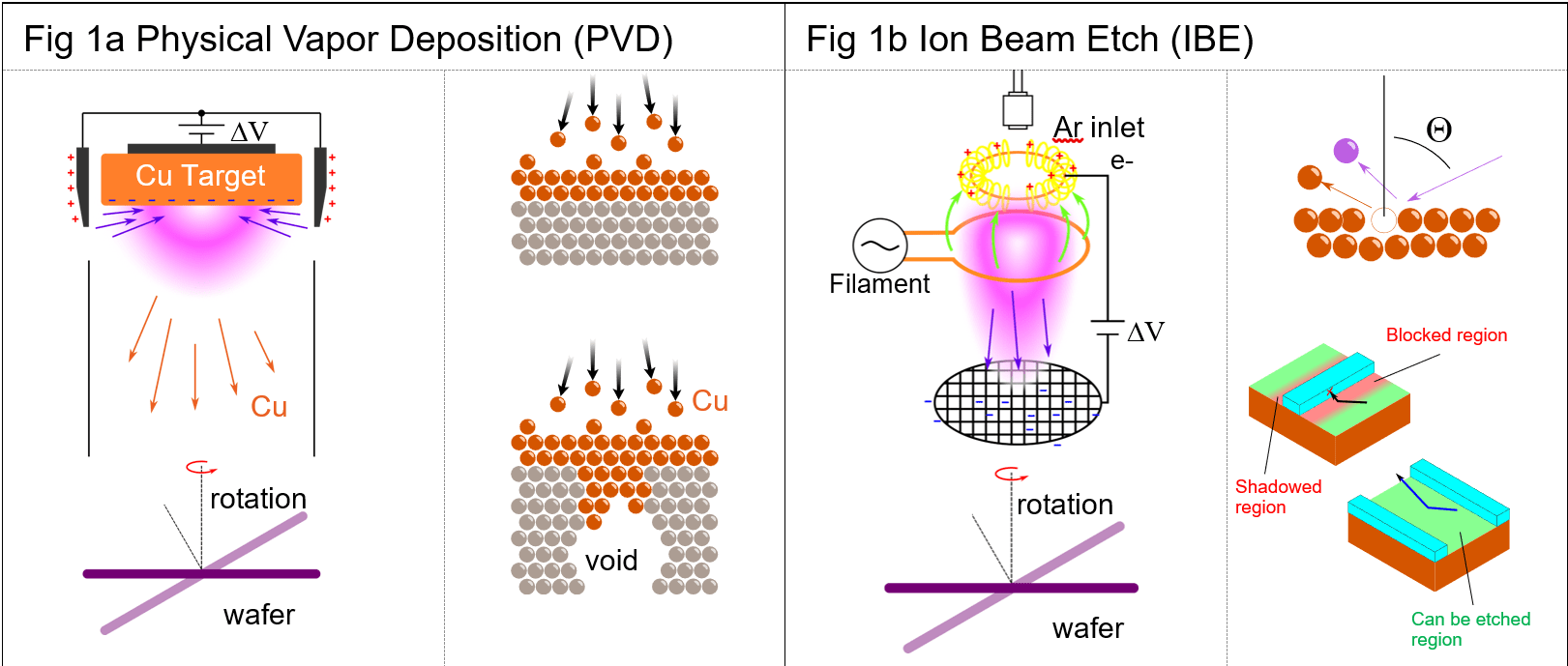

جسمانی بخارات کا ذخیرہ (PVD) تانبے کو اعلی حرکی توانائیوں (10 سے 100 eV کے درمیان) پر جمع کرنے کے لیے استعمال کیا جا سکتا ہے، کم مزاحمت، گھنے واحد کرسٹل ڈھانچے کی تشکیل۔ PVD میں ایک خرابی یہ ہے کہ PVD جمع کرنے میں نظر کے پھیلاؤ کی لکیر ہوتی ہے اور اسے صرف ہموار سطحوں پر یکساں طور پر جمع کیا جا سکتا ہے۔ اسے گہرے سوراخوں یا خندقوں کو بھرنے کے لیے استعمال نہیں کیا جا سکتا (شکل 1a)۔ الگ تھلگ تار کی شکلیں بنانے کے لیے، ایک یکساں Cu تہہ کو ایک چپٹی سطح پر جمع کرنا چاہیے اور پھر اسے جسمانی طور پر آئن بیم کے ذریعے کھینچنا چاہیے۔ Cu رد عمل والی گیسوں کے ساتھ کوئی غیر مستحکم مرکبات نہیں بناتا، لہذا ایک رد عمل آئن ایچ کا عمل استعمال نہیں کیا جا سکتا۔ آئن بیم ایچ (IBE) کے دوران پیدا ہونے والے ایکسلریٹڈ آر آئن Cu کو ہٹا سکتے ہیں اگر واقعہ کا زاویہ بہت زیادہ ہو۔ بدقسمتی سے، نقاشی کے قابل علاقے ماسک شیڈونگ اثرات کی وجہ سے محدود ہوں گے۔ شکل 1b ان خطوں کو دکھاتا ہے (سرخ رنگ میں) جہاں مادّے کو نہیں لگایا جا سکتا جب ماسک آنے والے آئن بیم پر کھڑا ہوتا ہے۔ یہ اینچ کی ناکامی خارج شدہ ایٹم کے راستے کے سایہ یا رکاوٹ کی وجہ سے ہوتی ہے۔ جب ماسک آئن کے راستے کے متوازی ہوتا ہے، تو تمام بے نقاب خطوں کو کھینچا جا سکتا ہے۔ اس طرح، آئن بیم کی اینچنگ من مانی طور پر لمبی لمبائی کے اینچنگ لائن کے سائز کے ماسک تک محدود ہے۔

![]()

تصویر 1: (1a) جسمانی بخارات کا ذخیرہ (PVD)؛ (1b) آئن بیم ایچ (IBE)۔

عمل کے مراحل اور ورچوئل فیبریکیشن کا عمل

لائن ریزسٹنس پر ڈیپوزیشن اور ایچ کے اثر کو سمجھنے کے لیے، اب ہم SEMulator3D ویزیبلٹی ڈیپوزیشن اور ایچ فنکشنز کا استعمال کرتے ہوئے PVD اور IBE ایچ پروسیس کو ماڈل بناتے ہیں۔ PVD کو SEMulator30D میں 3 ڈگری زاویہ پھیلاؤ کی نمائش کے عمل کا استعمال کرتے ہوئے دوبارہ تیار کیا گیا تھا، جو AR آئنوں کے ساتھ بمباری کے دوران نکالے گئے Cu ایٹموں کی بے ترتیب نوعیت کو درست طریقے سے ماڈل کرتا ہے۔ IBE کو ماڈل میں 2 ڈگری زاویہ پھیلاؤ اور 60 ڈگری قطبی زاویہ جھکاؤ کے ساتھ ایک ویزیبلٹی ایچ کا استعمال کرتے ہوئے دوبارہ تیار کیا گیا تھا، تاکہ کم شہتیر کے موڑ کے ساتھ گرڈ ایکسلریٹڈ آئنوں کے رویے کو ظاہر کیا جا سکے۔ فرض کیا جاتا ہے کہ دونوں ویفرز مفت گردش رکھتے ہیں۔ IBE اور PVD کی رکاوٹوں کو ایڈجسٹ کرنے کے لیے ورچوئل فیبریکیشن کے عمل میں عمل کے دیگر مراحل کو ایڈجسٹ کیا گیا ہے۔ شکل 2 وہی ڈھانچہ دکھاتا ہے جو ڈیماسین کیو فل (فگر 2a) اور PVD/IBE عمل (شکل 2b) دونوں کا استعمال کرتے ہوئے بنایا گیا ہے۔ PVD/IBE کی کچھ حدود کو شامل کرنے اور ہمارے مطلوبہ اختتامی ڈھانچے کے لیے مساوی شکل بنانے کے لیے اضافی عمل کے اقدامات شامل کیے گئے تھے۔

![]()

تصویر 2: (2a) Damascene fill Cu وائر فیبریکیشن؛ (2b) PVD/IBE کیو وائر فیبریکیشن۔

اس کے بعد ہم یہ ظاہر کرتے ہیں کہ ان حدود پر عمل کرتے ہوئے مساوی 16nm SRAM سرکٹ سیل PVD/IBE تاروں کے ساتھ گھڑا جا سکتا ہے۔ چونکہ لائن کے درمیانی سرے کے اوپر تمام دھاتی پرتیں ایک چپٹی سطح سے بنائی گئی ہیں، اس لیے یہ اسے PVD/IBE تاروں کے لیے ایک آئیڈیا امیدوار بناتا ہے، جیسا کہ finFET ڈیوائس میں نظر آنے والی پیچیدہ انٹر کنیکٹ ٹوپولاجیز کے برعکس۔ شکل 3 ہر دھاتی تہہ کے الگ تھلگ ڈھانچے کو دکھاتا ہے، اور PVD/IBE کا استعمال کرتے ہوئے تین دھاتی تہوں کے finFET ڈھانچے کو بنانے کے لیے درکار ضروری اقدامات۔

![]()

تصویر 3: (3a) 16nm FinFET MEOL اور 3 دھاتی تہیں؛ (3b) مرحلہ وار پی وی ڈی/آئی بی ای کے ذریعے دھاتی تہہ کی تعمیر۔

مزاحمت کے نتائج اور نتیجہ

اس کے بعد ہم تاروں کی برقی مزاحمت کی پیمائش دھات کی سب سے اونچی تہہ سے نیچے finFET P اور N چینلز کے ویاس تک کرتے ہیں، دونوں کے لیے damascene بہاؤ اور جسمانی بخارات کے جمع ہونے کے لیے۔ شکل 4 P اور N چینلز پر مزاحمتی پیمائش کا نقطہ آغاز اور اختتامی نقطہ دکھاتا ہے (دیگر تمام موصلی مواد شفاف ہیں)۔ TaN لائنر اور تانبے کے تار کے درمیان انٹرفیس کی مزاحمت کی تلافی کرنے کے لیے، TaN انٹرفیس کے قریب ترین فاصلے کے فنکشن کے طور پر 1 nm کے ایکسپونینشل ڈے کنسٹنٹ کا استعمال کرکے تانبے کی مزاحمتی صلاحیت میں اضافہ کیا گیا۔ چونکہ ڈیماسین فل Cu کے جمع ہونے کی توقع نہیں کی جاتی ہے کہ وہ مکمل طور پر کرسٹل لائن ہو، اس لیے Cu کی مزاحمتی صلاحیت میں 50 فیصد اضافہ ہوا ہے۔ PVD/IBE تانبے کا عمل TaN لائنر کا استعمال نہیں کرتا ہے، اس لیے exponential decay function کا اطلاق نہیں کیا گیا تھا، اور اس ماڈل میں تانبے کی بڑی مزاحمتی صلاحیت استعمال کی گئی تھی۔ ڈیماسین فلو بمقابلہ پی وی ڈی کا موازنہ کرنے والی مزاحمت کی میز کو شکل 4 میں شامل کیا گیا ہے۔

![]()

تصویر 4: P اور N چینلز پر مزاحمتی پیمائش کا نقطہ آغاز اور اختتامی نقطہ۔

ہمارے ماڈل سے کی گئی مزاحمتی اقدار بتاتی ہیں کہ ہم روایتی خندق اینچ کے مقابلے میں IBE/PVD فیبریکیشن طریقہ استعمال کرتے ہوئے مزاحمت میں 67 فیصد کمی حاصل کر سکتے ہیں جس کے بعد damascene جمع ہوتا ہے۔ ایسا اس لیے ہوتا ہے کیونکہ IBE/PVD میں کسی TaN لائنر کی ضرورت نہیں ہوتی ہے اور اس عمل کے دوران کم CU مزاحمتی صلاحیت ہوتی ہے۔ ہمارے نتائج بتاتے ہیں کہ زیادہ پیچیدہ من گھڑت عمل کی قیمت پر، دھاتی لائن کی تشکیل کے دوران ڈیماسین فل کے مقابلے IBE/PVD کا استعمال کرکے مزاحمتی بہتری حاصل کی جا سکتی ہے۔

ٹموتھی یانگ

(تمام پوسٹس)

ٹموتھی یانگ لام ریسرچ کمپنی کووینٹر میں سافٹ ویئر ایپلی کیشنز انجینئر ہیں۔ وہ میموری ٹیکنالوجیز میں مہارت کے ساتھ پروسیس ڈویلپمنٹ، انضمام اور پیداوار میں بہتری کی ایپلی کیشنز میں کام کرتا ہے۔ کووینٹر میں اپنے کام سے پہلے، یانگ نے ٹوکیو الیکٹران میں ایچ اسکیم تیار کرنے، پوسٹ لتھوگرافی پیٹرن میں بہتری کی تکنیک، SADP اور SAQP پیٹرننگ ایپلی کیشنز کے لیے پروسیس فلو کنٹرول، اور EUV اور وسرجن لتھوگرافی فوٹو ریزسٹ ٹیکنالوجی میں کام کیا۔ یانگ نے یو سی ایل اے سے فزکس میں بی ایس کی ڈگری حاصل کی، چیبا انسٹی ٹیوٹ آف ٹیکنالوجی سے میٹریل سائنس میں ایم ایس کی ڈگری، اور پی ایچ ڈی کی۔ توہوکو یونیورسٹی سے میٹریل سائنس میں ڈگری۔

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو بلاک چین۔ Web3 Metaverse Intelligence. علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ایڈریین ایشلے کے ساتھ مستقبل کا نقشہ بنانا۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- : ہے

- : ہے

- ][p

- 1

- 10

- 100

- a

- اوپر

- تیز

- ایڈجسٹ کریں

- درست طریقے سے

- حاصل

- حاصل کیا

- ایڈیشنل

- ایڈجسٹ

- تمام

- تمام پوسٹیں

- اور

- کونیی

- ایپلی کیشنز

- اطلاقی

- AR

- کیا

- AS

- فرض کیا

- At

- ایٹم

- BE

- بیم

- ہو جاتا ہے

- رہا

- کے درمیان

- حدود

- by

- حساب

- کر سکتے ہیں

- امیدوار

- نہیں کر سکتے ہیں

- کچھ

- چینل

- کمپنی کے

- مقابلے میں

- موازنہ

- پیچیدہ

- مسلسل

- رکاوٹوں

- کنٹرول

- روایتی

- کاپر

- قیمت

- تخلیق

- بنائی

- کرسٹل

- اعداد و شمار

- کمی

- گہری

- ڈگری

- مظاہرہ

- انحصار کرتا ہے

- ۱۰۰۰۰ ڈالر ڈیپازٹ

- جمع

- مطلوبہ

- ترقی

- ترقی

- آلہ

- براڈ کاسٹننگ

- دکھاتا ہے

- فاصلے

- دریافت

- نیچے

- کے دوران

- ہر ایک

- اثر

- اثرات

- یا تو

- انجینئر

- مساوی

- EV

- توقع

- مہارت

- ظالمانہ

- ناکامی

- اعداد و شمار

- بھرنے

- فلیٹ

- بہاؤ

- پیچھے پیچھے

- کے لئے

- فارم

- قیام

- فارم

- مفت

- سے

- مکمل طور پر

- تقریب

- افعال

- گرڈ

- ہے

- he

- ہائی

- انتہائی

- سوراخ

- HTTPS

- خیال

- وسعت

- بہتری

- بہتری

- in

- واقعہ

- شامل

- موصولہ

- شامل

- اضافہ

- اضافہ

- اشارہ کرتے ہیں

- انسٹی ٹیوٹ

- انضمام

- انٹرفیس

- الگ الگ

- IT

- میں

- فوٹو

- لام

- پرت

- تہوں

- حدود

- لمیٹڈ

- لائن

- لائنوں

- لانگ

- لو

- بناتا ہے

- ماسک

- ماسک

- مواد

- مواد

- زیادہ سے زیادہ چوڑائی

- پیمائش

- یاد داشت

- دھات

- طریقہ

- مشرق

- ماڈل

- ماڈل

- زیادہ

- فطرت، قدرت

- ضروری

- ضرورت

- of

- on

- حکم

- دیگر

- ہمارے

- متوازی

- راستہ

- پاٹرن

- جسمانی

- جسمانی طورپر

- طبعیات

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- پوائنٹ

- قطبی

- پوسٹ

- مراسلات

- کی روک تھام

- پہلے

- عمل

- عمل

- بے ترتیب

- موصول

- ریڈ

- کی عکاسی

- خطوں

- ہٹا

- تحقیق

- مزاحمت

- نتائج کی نمائش

- s

- اسی

- ترازو

- منصوبوں

- سائنس

- سیمکولیٹر

- شکل

- سائز

- سائز

- شوز

- نگاہ

- اہم

- سلیکن

- بعد

- ایک

- چھوٹے

- So

- سافٹ ویئر کی

- پھیلانے

- شروع

- حالت

- مرحلہ

- مراحل

- ساخت

- بعد میں

- سطح

- ٹیبل

- تکنیک

- ٹیکنالوجی

- ٹیکنالوجی

- کہ

- ۔

- یہ

- تین

- تھمب نیل

- کرنے کے لئے

- ٹوکیو

- سب سے اوپر

- روایتی طور پر

- شفاف

- ucla

- سمجھ

- یونیورسٹی

- استعمال کی شرائط

- استعمال کیا جاتا ہے

- استعمال کیا

- اقدار

- کی طرف سے

- مجازی

- کی نمائش

- واٹیٹائل

- حجم

- vs

- جس

- جبکہ

- گے

- وائر

- ساتھ

- کام

- کام کیا

- کام کرتا ہے

- پیداوار

- زیفیرنیٹ