پہلے میں نے بلاگ کیا تھا۔ IC اور ASIC فنکشنل تصدیق، لہذا آج وقت آگیا ہے کہ FPGA فنکشنل تصدیق کی حالت کے ساتھ اس کو ختم کیا جائے۔ ولسن ریسرچ گروپ 2018 سے ہر دو سال بعد ایک FPGA رپورٹ مرتب کر رہا ہے، لہذا یہ تیسری بار ہے جب اس نے ڈیزائن کے اس حصے پر توجہ مرکوز کی ہے۔ FPGA مارکیٹ $5.8 بلین پر قابل قدر ہے، اور 8.1 تک اس کے $2025 بلین تک بڑھنے کی پیشن گوئی کی گئی ہے۔ FPGAs 1984 میں محدود گیٹ کی گنجائش کے ساتھ شروع ہوئے تھے، اور اب اس میں لاکھوں گیٹس، پروسیسرز اور معیاری ڈیٹا پروٹوکولز شامل ہو چکے ہیں۔

کم والیوم ایپلی کیشنز FPGA ڈیوائسز کے NRE سے فائدہ اٹھاتے ہیں، اور انجینئرز تیز رفتاری سے تصدیق اور توثیق کر کے اپنے ڈیزائن کا پروٹو ٹائپ کر سکتے ہیں۔ ایف پی جی اے میں اب پروسیسر شامل ہیں، جیسے: Xilinx Zynq UltraSCALE, انٹیل اسٹریٹکس, مائکروچپ اسمارٹ فیوژن. فنکشنل تصدیقی مطالعہ میں 980 شرکاء میں سے، FPGA اور قابل پروگرام SoC FPGA ڈیزائن اسٹائل سب سے زیادہ مقبول ہیں۔

جیسا کہ حال ہی میں FPGAs کے سائز میں اضافہ ہوا ہے، بگ سے پاک پروڈکشن ریلیز کا امکان صرف 17% رہ گیا ہے، جو کہ درست فرسٹ سلکان کے لیے IC اور ASIC پروجیکٹس کے 30% سے بھی بدتر ہے۔ واضح طور پر، ہمیں پیچیدہ FPGA سسٹمز کے لیے بہتر فنکشنل تصدیق کی ضرورت ہے۔

پیداوار میں پائے جانے والے کیڑے کی اقسام کئی زمروں میں آتی ہیں:

- 53% - منطق یا فنکشنل

- 31% - فرم ویئر

- 29% - کلاکنگ

- 28% - ٹائمنگ، راستہ بہت سست

- 21% - ٹائمنگ، راستہ بہت تیز

- 18% - مخلوط سگنل انٹرفیس

- 9% - حفاظتی خصوصیت

- 8٪ - سیکیورٹی کی خصوصیت

ناکامی، منطق یا فنکشنل کے سب سے بڑے زمرے میں زوم کرتے ہوئے، پانچ بنیادی وجوہات ہیں۔

FGPA پروجیکٹس زیادہ تر وقت پر مکمل نہیں ہوئے، ایک بار پھر سسٹمز کے بڑے سائز، منطق کی پیچیدگی اور یہاں تک کہ تصدیقی طریقوں کے استعمال کی وجہ سے۔

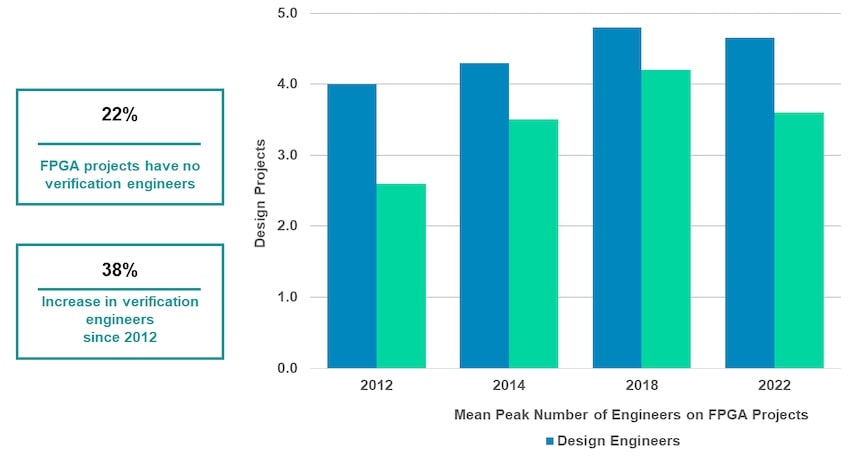

FPGA ٹیم کے انجینئروں کے پاس ڈیزائن انجینئر یا تصدیقی انجینئر جیسے الگ عنوانات ہو سکتے ہیں، پھر بھی 22% پراجیکٹس پر کوئی تصدیقی انجینئر نہیں تھے – یعنی ڈیزائن انجینئرز نے ڈبل ڈیوٹی کی اور اپنے IP کی تصدیق کی۔ پچھلے 10 سالوں میں FPGA پروجیکٹ پر تصدیقی انجینئرز کی تعداد میں 38% اضافہ ہوا ہے، لہذا یہ بگ فری پروڈکشن کی طرف پیشرفت ہے۔

ایف پی جی اے پراجیکٹس پر تصدیقی انجینئرز نے اپنا زیادہ تر وقت ڈیبگ ٹاسک پر 47% پر صرف کیا:

- 47% - ڈیبگ

- 19% - ٹیسٹ بنانا اور نقلی چلانا

- 17٪ - ٹیسٹ بینچ کی ترقی

- 11% - ٹیسٹ پلاننگ

- 6% - دیگر

وقت کے ساتھ ساتھ ایمبیڈڈ پروسیسرز کی تعداد میں مسلسل اضافہ ہوا ہے، اس لیے 65% FPGA ڈیزائنز میں اب ایک یا زیادہ پروسیسر کور ہیں، جس سے ہارڈ ویئر، سافٹ ویئر انٹرفیس کے درمیان تصدیق کی مقدار میں اضافہ ہوتا ہے۔ اور آن چپ نیٹ ورکس کا انتظام کرنا۔

ہمیشہ سے مقبول RISC-V پروسیسر 22% FPGAs میں سرایت کرتا ہے، اور AI ایکسلریٹر 23% پروجیکٹس میں استعمال ہوتے ہیں۔ FPGAs پر 3-4 اوسط تعداد میں کلاک ڈومینز استعمال کیے جاتے ہیں، اور انہیں تصدیق کے لیے گیٹ لیول ٹائمنگ سمولیشنز، نیز تصدیق کے لیے جامد کلاک ڈومین کراسنگ (CDC) ٹولز کے استعمال کی ضرورت ہوتی ہے۔

حساس ڈیٹا رکھنے کے لیے 49% FPGA ڈیزائنز میں سیکیورٹی فیچرز شامل کیے جاتے ہیں، نیز 42% FPGA پروجیکٹس حفاظتی معیارات یا رہنما خطوط پر عمل پیرا ہوتے ہیں۔ SemiWiki پر ہم اکثر بلاگ کرتے رہے ہیں۔ ISO 26262 اور ڈی او 254 معیارات فنکشنل سیفٹی (FuSa) ڈیزائن کی کوششیں پروجیکٹ کے مجموعی وقت کا 25% سے 50% کے درمیان لیتی ہیں۔

سب سے اوپر تین تصدیقی زبانیں ہیں VHDL، SystemVerilog اور Verilog؛ لیکن Python اور C/C++ زبانوں میں حالیہ چھلانگوں کو بھی دیکھیں۔

سب سے مشہور FPGA طریقہ کار اور ٹیسٹ بینچ بیس کیس لائبریریاں ہیں: Accellera UVM، OSVVM اور UVVM۔ ازگر پر مبنی cocotb یہاں تک کہ 2022 کے لیے ایک نئے زمرے کے طور پر شامل کیا گیا۔

دعویٰ کرنے والی زبانیں 45% پر SystemVerilog Assertions (SVA) کی قیادت میں ہیں، اس کے بعد Accellera Open Verification Library (OVL) 13% اور PSL 11% ہے۔ FPGA ڈیزائنز RTL ڈیزائن کے لیے VHDL کو SVA کے ساتھ جوڑ سکتے ہیں۔

باضابطہ جائیداد کی جانچ FPGA منصوبوں کے درمیان بڑھ رہی ہے، خاص طور پر EDA وینڈرز کے ذریعہ زیادہ خودکار رسمی ایپس متعارف کرائی گئی ہیں۔

پچھلے 10 سالوں میں نقلی بنیاد پر توثیق کے طریقوں سے ثابت ہوتا ہے کہ مطابقت کے لحاظ سے درج ہے: کوڈ کوریج، فنکشنل کوریج، دعوے، محدود بے ترتیب۔

خلاصہ

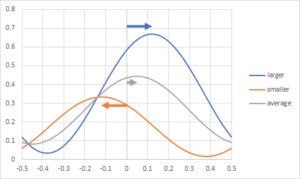

17 میں FPGA پروجیکٹس کے لیے کم 2022% بگ فری نمبر جس نے اسے پروڈکشن میں بدل دیا، میرے لیے سب سے حیران کن نمبر تھا، کیونکہ فیلڈ میں کسی ڈیوائس کو دوبارہ منگوانے یا دوبارہ پروگرام کرنے کی کوشش مہنگا ہے اور درست کرنے میں وقت لگتا ہے۔ ایک زیادہ مضبوط فنکشنل توثیق کا طریقہ پیداوار میں بگ سے بچنے کا باعث بنتا ہے، اور مطالعہ کے شرکاء کو دو گروپوں میں تقسیم کرنے سے فائدہ ظاہر ہوتا ہے۔

مکمل پڑھیں 18 صفحات کا وائٹ پیپر یہاں ہے۔.

متعلقہ بلاگز

اس پوسٹ کو بذریعہ شیئر کریں:

- SEO سے چلنے والا مواد اور PR کی تقسیم۔ آج ہی بڑھا دیں۔

- پلیٹو بلاک چین۔ Web3 Metaverse Intelligence. علم میں اضافہ۔ یہاں تک رسائی حاصل کریں۔

- ماخذ: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- ہمارے بارے میں

- ایکسلریٹر

- شامل کیا

- مان لیا

- منہ بولابیٹا بنانے

- AI

- کے درمیان

- رقم

- اور

- ایپلی کیشنز

- نقطہ نظر

- نقطہ نظر

- ایپس

- asic

- خودکار

- اوسط

- کیا جا رہا ہے

- فائدہ

- بہتر

- کے درمیان

- ارب

- بگ کی اطلاع دیں

- کیڑوں

- اہلیت

- اقسام

- قسم

- کیونکہ

- وجہ

- وجوہات

- سی ڈی سی

- موقع

- جانچ پڑتال

- واضح طور پر

- گھڑی

- کوڈ

- جمع

- مکمل

- پیچیدہ

- پیچیدگی

- کوریج

- تخلیق

- اہم

- اعداد و شمار

- ڈیزائن

- ڈیزائن

- آلہ

- کے الات

- DID

- مختلف

- ڈومین

- ڈومینز

- گرا دیا

- کوشش

- کوششوں

- ایمبیڈڈ

- انجینئر

- انجینئرز

- خاص طور پر

- بھی

- ہر کوئی

- مہنگی

- ناکامی

- گر

- خصوصیات

- میدان

- پہلا

- توجہ مرکوز

- پیچھے پیچھے

- رسمی طور پر

- ملا

- fpga

- سے

- فنکشنل

- گیٹس

- گروپ

- گروپ کا

- بڑھائیں

- بڑھتے ہوئے

- اضافہ ہوا

- ہدایات

- ہارڈ ویئر

- پکڑو

- HTML

- HTTPS

- in

- شامل

- اضافہ

- اضافہ

- اضافہ

- انٹیل

- انٹرفیسز

- متعارف

- IP

- IT

- چھلانگ

- زبانیں

- بڑے

- سب سے بڑا

- قیادت

- قیادت

- لائبریریوں

- لائبریری

- لمیٹڈ

- فہرست

- لو

- بنا

- مینیجنگ

- مارکیٹ

- زیادہ سے زیادہ چوڑائی

- مطلب

- طریقوں

- طریقوں

- لاکھوں

- زیادہ

- سب سے زیادہ

- سب سے زیادہ مقبول

- ضرورت ہے

- نیٹ ورک

- نئی

- تعداد

- ایک

- کھول

- حکم

- مجموعی طور پر

- خود

- کاغذ.

- امیدوار

- گزشتہ

- راستہ

- پلاٹا

- افلاطون ڈیٹا انٹیلی جنس

- پلیٹو ڈیٹا

- علاوہ

- مقبول

- پوسٹ

- پروسیسر

- پروسیسرز

- پیداوار

- پیش رفت

- منصوبے

- منصوبوں

- جائیداد

- پروٹوکول

- پروٹوٹائپ

- ازگر

- جلدی سے

- بے ترتیب

- حال ہی میں

- حال ہی میں

- جاری

- مطابقت

- رپورٹ

- کی ضرورت

- تحقیق

- ریسرچ گروپ

- مضبوط

- جڑ

- منہاج القرآن

- چل رہا ہے

- سیفٹی

- سیکورٹی

- حصے

- حساس

- کئی

- ہونا چاہئے

- دکھائیں

- شوز

- siemens ڈاؤن لوڈ،

- سلیکن

- بعد

- بڑا

- سائز

- So

- سافٹ ویئر کی

- تیزی

- خرچ

- معیار

- شروع

- حالت

- مستحکم

- مطالعہ

- حیرت انگیز

- سسٹمز

- لے لو

- کاموں

- ٹیم

- تکنیک

- ٹیسٹ

- ۔

- ریاست

- ان

- تھرڈ

- تین

- وقت

- وقت

- عنوانات

- کرنے کے لئے

- آج

- بھی

- اوزار

- سب سے اوپر

- کی طرف

- اقسام

- استعمال کی شرائط

- دکانداروں

- توثیق

- تصدیق

- تصدیق کرنا

- کی طرف سے

- حجم

- جس

- سفید

- وائٹ پیپر

- ولسن

- سال

- زیفیرنیٹ