Tasarımcıların RISC-V çözümlerini farklılaştırmak için birçok yolu vardır. Bir yol, spesifikasyona göre çeşitli RISC-V çekirdek özelleştirmelerine ve uzantılarına başlar. Bir diğeri, bir veya daha fazla RISC-V çekirdeği etrafında eksiksiz bir çip üzerinde sistem (SoC) tasarımında IP bloklarının seçilmesine ve birleştirilmesine odaklanır. Üçüncüsü ortaya çıkıyor: RISC-V çekirdeklerini ve diğer IP bloklarını basit bir veri yolu yapısı yerine çip üzerinde ağ (NoC) ile birbirine bağlamak. Ve bu sadece en üst düzeyde değil; RISC-V çekirdeklerini NoC'lerle eşleştirmek, verilerin herhangi bir çip üzerinde protokol kullanılarak herhangi bir iş yükünde verimli bir şekilde akması gereken birçok SoC tasarım zorluğuna yanıt verir.

Gelişmiş ara bağlantı şemalarıyla değişen performans katmanları

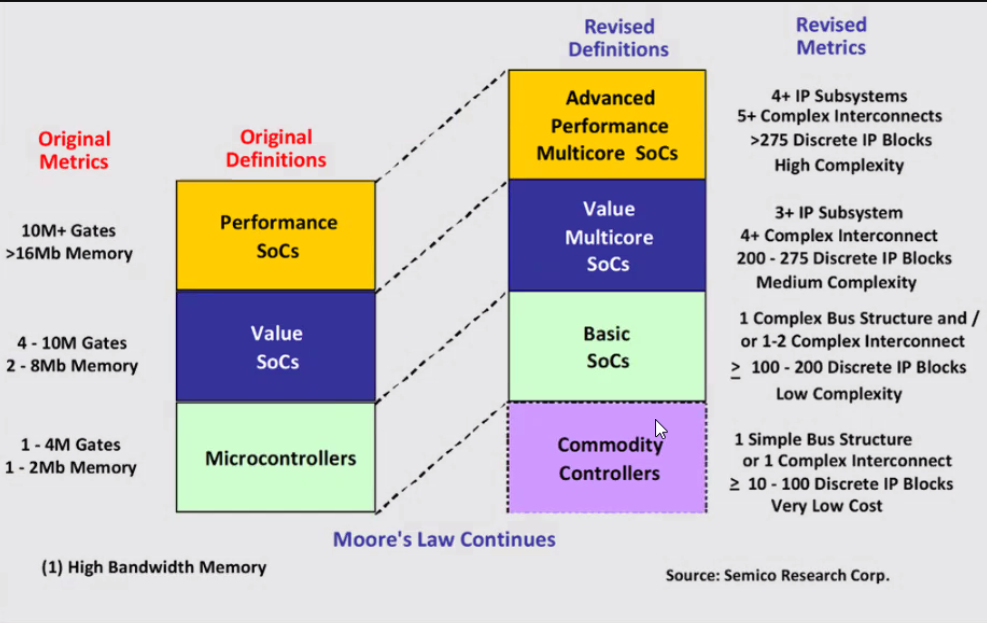

Sadece geçitleri, çekirdekleri ve çevresel blokları saymak artık bir SoC tasarımının performans potansiyelini tanımlamıyor. Semico Research'e göre, ara bağlantı şemaları artık SoC performans katmanları arasındaki çizgiyi tanımlıyor ve ara bağlantıların basit veri yolu yapılarından daha karmaşık şemalara doğru değiştiği yeni bir katman açıldı.

Semico'nun güncellenmiş tanımı, iş başında olan üç gücü kabul ediyor: çok çekirdekli tasarımların yaygınlığı, karmaşık tasarım olarak kabul edilenler için daha yüksek bir çıta ve bunu takip eden "mikrokontrolör" ile "SoC" arasındaki bulanık çizgi. Semico'nun son görüşüne göre, bir metrik olarak geçit sayımı kavramı ortadan kalkıyor çünkü modern bir işlemci çekirdeği birçok kapıyı da beraberinde sürükleyebiliyor. Karmaşıklık, alt sistemlere ve çeşitli IP bloklarına göre değişen ara bağlantıların bir fonksiyonu haline gelir.

SoC performans katmanları, resim Semico Research Corp'un izniyle alınmıştır.

Basit bir veri yolunun (muhtemelen tek işlemci çekirdeğine ve sürekli veri yolu için rekabet etmeyen düşük görev döngülü çevre birimlerine sahip bir parçanın) yapacağı yerde, Semico bir emtia denetleyici katmanı görüyor. Bunun üzerindeki herhangi bir şey, muhtemelen en azından bazı çevre birimlerinin çip üzerindeki bant genişliği ve işlemci çekirdeğinin/çekirdeklerinin dikkatini çekmek için mücadele ettiği bir SoC haline gelir. Daha yüksek SoC katmanları, her biri ayarlanmış ara bağlantı teknolojisine sahip birden çok çekirdeğe ve birden çok IP alt sistemine sahiptir.

NoC'ler daha fazla protokol ve alt sistem alıyor

RISC-V, daha güçlü çekirdekler ortaya çıktıkça bu performans katmanlarını hızlı bir şekilde yükseltti ve Semico ölçeğinin alt ucunda daha az uygulanabilirlik olmadı. Ancak RISC-V tasarımcıları daha yüksek katmanlarda görülen karmaşık ara bağlantı şemalarında daha az deneyime sahip olabilir. Arteris Çözümler ve İş Geliştirmeden Sorumlu Başkan Yardımcısı Frank Schirrmeister, "RISC-V ara bağlantısı için ilk düşünce TileLink olabilir, ancak daha karmaşık senaryolarda kullanılması zor olabilir" diyor.

Bir NoC'nin süper gücü, farklı protokoller kullanarak alt sistemleri birbirine bağlama yeteneğidir ve SoC tasarımcılarının orta düzeyde karmaşıklıkta bile çeşitli protokollerle karşılaşması muhtemeldir. AXI, basit IP blok bağlantıları için oyun alanını eşitledi. Birlikte işleme bloklarına sahip çok çekirdekli çözümler, önbellek tutarlılığı gerektirir ve bu da CHI protokolünün ortaya çıkmasına neden olur. G/Ç bellek paylaşımı, daha hızlı CXL ara bağlantısının şekillendirilmesine yardımcı oldu. Schirrmeister şöyle devam ediyor: "Çeşitli alt sistemler ve protokollerle bilgi işlem ve aktarımı birlikte optimize etme zamanı geldiğinde, NoC daha iyi bir çözümdür."

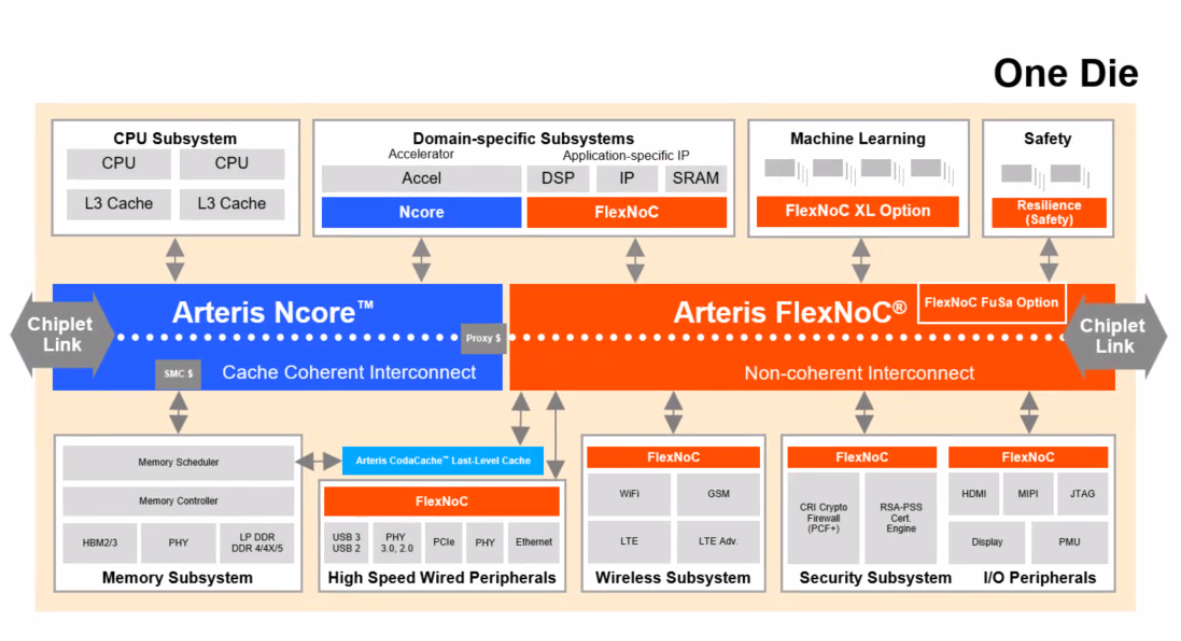

RISC-V çekirdeklerini NoC'lerle eşleştirmek nasıl görünebilir? Arteris müşterisi Tenstorrent, olanaklara kısa bir bakış sağlıyor. Son zamanlardaki odak noktaları, RISC-V çekirdeklerini, makine öğrenimi hızlandırma IP'sini ve birçok uç yapay zeka uygulamasında bulunan standart çevre birimlerini birleştiren yeniden kullanılabilir bir yonga oluşturmaktır. Büyük ölçekte, Arteris Ncore önbellek uyumlu ara bağlantısını ve Arteris FlexNoC tutarlı olmayan ara bağlantısının birkaç bölümünü kullanan tek kalıplı bir uygulama aşağıdaki şemaya benzeyebilir.

Resim Arteris'in izniyle

Akıllı Bellek Denetleyicisi (SMC), yoğun bellek kullanan uygulamalarda yüksek performanslı, sunucu düzeyinde bellek bağlantısı sağlar. İsimsiz "yonga bağlantısı", daha sıkı yonga entegrasyonu için optimize edilmiş nispeten yeni bir spesifikasyon olan UCIe olabilir. Yeni alt sistem ara bağlantıları ortaya çıktığında, NoC'nin bir bölümünü uyarlamak, çip çapındaki yapının tamamını parçalamaktan daha kolay yönetilebilir.

RISC-V çekirdeklerini NoC'lerle eşleştirmek riski ve pazara sunma süresini azaltır

Bu şema karmaşık görünüyorsa ve kabul edilirse, belki de çoğu RISC-V uygulaması şu anda o kadar da karmaşık değildir, şunu düşünün: chiplet'ler zaten entegrasyonu çok daha yüksek seviyelere taşıyor. Günümüzün gelişmiş RISC-V çok çekirdekli kısmı, inovasyon hızlandıkça gelecek yılın değerli SoC'si olacak.

Arteris Ncore ve Arteris FlexNoC geliştirme araçları, uygulama için RTL çıktısı vererek çeşitli avantajlar sağlar. EDA iş akışında fiziksel NoC tahmini basittir. Boru hattı aşamalarının sayısı gibi NoC parametre ayarlamaları da EDA araçlarında birkaç tıklama uzaktadır. Bir alt sistem protokolünün eklenmesi için yukarıda bahsedilen modifikasyonlar da kolaylıkla gerçekleştirilebilir. Schirrmeister, "En üst düzeyde kullanıcılar NoC uzmanlığımıza anında erişim kazanıyor" diyor. "Sonuçta, araçlarımızın kullanımı ilk geçişte başarı için kolaydır ve karmaşık ara bağlantılara sahip daha iddialı gelecek projeleri için bir büyüme yolu sağlar."

RISC-V çekirdeklerini NoC'lerle eşleştirmek, bir IP bloğunun daha bir tasarıma girme ve çip boyunca bir ara bağlantı yeniden tasarımı dalgalanmasını tetikleme riskini azaltır. Ayrıca karmaşık SoC tasarımlarının pazara çıkış süresini, kendin yap ara bağlantı yapılarına kıyasla azaltır. NoC'lerin bant genişliği ve güç yönetimi gibi diğer faydalarını burada tartışmadık, ancak RISC-V tasarımlarındaki NoC'lerin durumu, yalnızca çeşitli protokol karışımı göz önüne alındığında güçlüdür.

Arteris'nin web sitesini ziyaret edin NoC'ler hakkında daha fazla bilgi için ve diğer ürünler.

Bu gönderiyi şu yolla paylaş:

- SEO Destekli İçerik ve Halkla İlişkiler Dağıtımı. Bugün Gücünüzü Artırın.

- PlatoData.Network Dikey Üretken Yapay Zeka. Kendine güç ver. Buradan Erişin.

- PlatoAiStream. Web3 Zekası. Bilgi Genişletildi. Buradan Erişin.

- PlatoESG. karbon, temiz teknoloji, Enerji, Çevre, Güneş, Atık Yönetimi. Buradan Erişin.

- PlatoSağlık. Biyoteknoloji ve Klinik Araştırmalar Zekası. Buradan Erişin.

- Kaynak: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :vardır

- :dır-dir

- :olumsuzluk

- :Neresi

- $UP

- a

- kabiliyet

- yukarıdaki

- hızlanma

- erişim

- başarılı

- Göre

- karşısında

- ekleme

- ayarlamaları

- ileri

- avantajları

- AI

- zaten

- Ayrıca

- hırslı

- an

- ve

- Başka

- cevaplar

- herhangi

- bir şey

- görünmek

- uygulamaları

- ARE

- etrafında

- AS

- At

- Dikkat

- uzakta

- Bant genişliği

- bar

- BE

- olur

- faydaları

- Daha iyi

- arasında

- Engellemek

- Blokları

- otobüs

- iş

- iş geliştirme

- fakat

- CAN

- dava

- zorluklar

- değişiklik

- değiştirme

- yonga

- birleştirme

- emtia

- karşılaştırıldığında

- tamamlamak

- karmaşık

- karmaşıklık

- hesaplamak

- Sosyal medya

- bağ

- Bağlantılar

- Düşünmek

- kabul

- düşünen

- devam ediyor

- devamlı olarak

- kontrolör

- çekirdek

- Corp

- olabilir

- sayma

- Oluşturma

- müşteri

- veri

- tanımlamak

- tanım

- Talep

- Dizayn

- tasarımcıları

- tasarımlar

- gelişme

- Geliştirme araçları

- farklı

- zor

- tartışılan

- çeşitli

- do

- sürme

- her

- kolay

- kenar

- verimli biçimde

- çıkmak

- ortaya çıkan

- son

- girme

- Tüm

- Hatta

- deneyim

- Uzmanlık

- uzantıları

- Daha hızlı

- az

- alan

- kavga

- Ad

- akış

- odak

- odaklanır

- takip etme

- İçin

- Güçler

- bulundu

- dürüst

- itibaren

- işlev

- gelecek

- Kazanç

- Gates,

- Verilmesi

- belirti

- verilmiş

- Büyüme

- Var

- yardım

- okuyun

- Yüksek

- yüksek performans

- daha yüksek

- Ancak

- HTTPS

- görüntü

- Acil

- uygulama

- in

- bilgi

- Yenilikçilik

- yerine

- bütünleşme

- birbirine bağlı

- ara bağlantılar

- içine

- IP

- IT

- ONUN

- sadece

- son

- başlattı

- en az

- az

- sevmek

- Muhtemelen

- çizgi

- hatları

- uzun

- Bakın

- gibi görünmek

- GÖRÜNÜYOR

- Düşük

- alt

- yönetim

- çok

- maksimum genişlik

- Mayıs..

- olabilir

- Bellek

- adı geçen

- metrik

- karıştırmak

- orta

- Modern

- Değişiklikler

- Daha

- çoğu

- taşındı

- çok

- çoklu

- şart

- yeni

- sonraki

- yok hayır

- kavram

- şimdi

- numara

- of

- on

- ONE

- açıldı

- optimize

- or

- Diğer

- bizim

- çıktı

- Barış

- eşleştirme

- parametre

- Bölüm

- yol

- başına

- performans

- periferik

- çevre

- fiziksel

- seçmek

- Seçtikleri

- boru hattı

- Platon

- Plato Veri Zekası

- PlatoVeri

- OYNA

- oynama

- olanakları

- Çivi

- potansiyel

- güç kelimesini seçerim

- güçlü

- İşlemci

- Ürünler

- Projeler

- protokol

- protokolleri

- sağlamak

- sağlar

- sağlama

- hızla

- kolayca

- son

- tanır

- yeniden tasarlamak

- azaltır

- Nispeten

- araştırma

- yeniden kullanılabilir

- krallar gibi yaşamaya

- Ripple

- Yükselmek

- Risk

- koşmak

- s

- diyor

- ölçek

- senaryolar

- şemaları

- Bölüm

- görüldü

- Gördükleri

- segmentler

- seçme

- birkaç

- Shape

- paylaşımı

- Basit

- beri

- tek

- akıllı

- çözüm

- Çözümler

- biraz

- sofistike

- şartname

- aşamaları

- standart

- basit

- güçlü

- yapı

- yapılar

- sonraki

- başarı

- böyle

- süper güç

- Teknoloji

- göre

- o

- The

- ve bazı Asya

- Bunlar

- Üçüncü

- Re-Tweet

- düşünce

- üç

- aşama

- Kravatlar

- sıkı

- zaman

- için

- bugünkü

- birlikte

- araçlar

- taşıma

- tetikleme

- İSİMSİZ

- güncellenmiş

- kullanım

- kullanıcılar

- kullanma

- değer

- çeşitli

- değişen

- üzerinden

- Görüntüle

- vp

- we

- Web sitesi

- Ne

- Nedir

- ne zaman

- irade

- ile

- İş

- iş akışı

- zefirnet