Yıllar boyunca DRC araçları, IC tasarım boyutunun muazzam büyümesine ayak uydurmak için takdire şayan bir iş çıkardı. Yine de, DRC, dökümhane kural destelerini kullanarak tam tasarımın imzalanması için koşar, tamamlanması saatler sürer. Bu uzun çalışma süreleri, son onay için kabul edilebilir, ancak geç aşama sorunlarını gidermek için tasarımda küçük değişiklikler yapıldığında, DRC sonuçlarının hızlı bir şekilde gerekli olduğu birçok durum vardır. Siemens EDA, MaxLinear ile birlikte Calibre RealTime Digital tasarım içi DRC'nin tasarımda küçük değişiklikler yapıldığında DRC sonuçlarını nasıl hızlı bir şekilde sağlayabileceğini gösteren bir teknik inceleme yazdı. Yerelleştirilmiş değişiklikler için daha hızlı DRC geri dönüşü, bant çıkışına ulaşmak için sıklıkla ihtiyaç duyulan yinelemeli hata düzeltmeyi hızlandırabilir.

"MaxLinear ve Calibre RealTime Digital: Faster Signoff DRC convergence artı üretilebilirlik için tasarım optimizasyonu" başlıklı teknik incelemede MaxLinear ve Siemens, DRC'yi bir tasarımın küçük bir bölgesinde tam dökümhane kural güvertesi ile çalıştırma yeteneğinin, saatlerce ve acı verici yavaş yinelemelerden tasarruf edin.

Modern P&R araçları, DRC'nin doğru düzenini üretmek için mükemmel bir iş çıkarır. Ancak, ihlal kaynaklarının daha karmaşık olduğu ve P&R sırasında gözden kaçırıldığı durumlar her zaman vardır. Bunlar genellikle karmaşık tasarım kurallarını dikkate alarak manuel bir düzeltme gerektirir. Bu manuel düzeltmeler sırasında yeni hataların ortaya çıkma olasılığı da vardır. Siemens, Calibre RealTime Digital'in P&R araçlarıyla nasıl arayüz oluşturduğunu vurgulayan teknik incelemede MaxLinear'dan bilgiler sunar ve manuel düzeltmeleri hızlı bir şekilde uygulamalarını ve doğrulamalarını sağlar. Alternatif, sadece küçük bir alandaki değişikliklerin doğru olup olmadığını görmek için tam bir DRC çalışması gerçekleştirmektir.

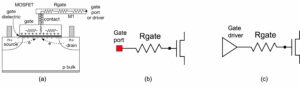

MaxLinear, analog ve dijital bloklarla cips yapar. Analog bloklar daha az metal katman gerektirir, bu nedenle üretim maliyetini azaltmak için tam tasarımda yönlendirme katmanlarını azaltmaya çalışırlar. Bu, genellikle yüksek bir DFM sıralamasını korumakla çelişen yönlendirme yoğunluğu sorunları yaratır. Tek kesimli yollar en az alanı kullanır ancak düşük bir DFM sıralamasına katkıda bulunur. Zorlama söz konusu olduğunda MaxLinear tasarımcıları, DFM takaslarına karşı yönlendirilebilirlik ile başa çıkmak için türler arasında manuel olarak geçiş yapabilir. Ancak bunların, çoklu model ihlalleri gibi şeyleri kontrol etmek için kapsamlı bir DRC ile takip edilmesi gerekir. Calibre RealTime Digital, tasarımcıların türler arasında geçiş yapmalarına ve ardından herhangi bir DRC hatasının olup olmadığını hızlı bir şekilde görmelerine olanak tanır.

Çözümü zaman ve çaba gerektiren DRC sorunlarına yol açabilecek tek sorun Via'lar değildir. Teknik inceleme, manuel çalışmanın gerekli olduğu birkaç durumu açıklar ve bu sorunları nihai olarak çözmenin tek yolu temiz bir DRC çalıştırması elde etmektir. Sürecin sonlarında meydana gelen bu durumlardan biri, ECO'ların mevcut maskelerle uyumlu olduğundan emin olmak için yeniden bantlama (RTO) kontrollerine ihtiyaç duyulmasıdır. RTO kuralları, doğası gereği orijinal DRC kurallarından daha kısıtlayıcıdır.

Teknik inceleme ayrıca, uygun olmayan yolların kullanılmasından kaynaklanabilecek elektrogöç sorunlarına da değinmektedir. Burada yine Calibre ReatTime Digital, MaxLinear için değiştirme yoluyla DRC düzeltmesini uygulamada etkili oldu. Hep birlikte ele alındığında, bir tasarımdaki işlevsel veya üretilebilirlik sorunlarını düzeltmek için küçük değişiklikler yapıldıktan sonra DRC kontrollerini gerektiren birçok durum vardır. Tam DRC çalışmasında bir gün veya daha uzun bir geri dönüş beklemek yerine anında sonuç alma yeteneğine sahip olmak, bir projeden günler veya haftalar çıkarabilir. Büyük bir DRC koşusundan sonra sürprizler bulmak iyi değil. P&R araçlarına yönelik Siemens Calibre RealTime Digital arayüzü bunun için ideal görünüyor. Bu Siemens teknik incelemesi Siemens EDA web sitesinde bulunabilir.

Bu gönderiyi şu yolla paylaş:

Kaynak: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/

- Türkiye

- ALAN

- mal

- neden

- Çekler

- cips

- fikir ayrılığı

- içerik

- gün

- anlaşma

- Dizayn

- dijital

- Nihayet

- uygun

- sabit

- Dökümhane

- tam

- Tercih Etmenizin

- Büyüme

- okuyun

- Yüksek

- Ne kadar

- HTTPS

- Kocaman

- bilgi

- sorunlar

- İş

- koruma

- öncülük etmek

- Uzun

- üretim

- Maskeler

- metal

- kâğıt

- proje

- azaltmak

- Sonuçlar

- kurallar

- koşmak

- iletkenlik birimi

- beden

- küçük

- So

- uzay

- hız

- Aşama

- anahtar

- thumbnail

- zaman

- Karşı

- Web sitesi

- Beyaz kağıt

- İş

- yıl