นักออกแบบวงจรรวมแบบอะนาล็อกสามารถใช้เวลาและความพยายามมากเกินไปในการนำวิธีการวนซ้ำแบบเดิมที่คุ้นเคยและเป็นแบบแมนนวลกลับมาใช้ใหม่ในการออกแบบวงจร เพียงเพราะนั่นคือวิธีที่มันทำกันมาตลอด การปรับวงจรให้เหมาะสมเป็นแนวทาง EDA ที่สามารถปรับขนาดทรานซิสเตอร์ทั้งหมดในเซลล์ได้โดยอัตโนมัติ โดยการเรียกใช้การจำลอง SPICE ในมุม PVT และรูปแบบกระบวนการต่างๆ เพื่อตอบสนองข้อกำหนดการออกแบบสัญญาณอะนาล็อกและสัญญาณผสม ฟังดูมีแนวโน้มใช่ไหม?

ฉันควรพิจารณาใช้เครื่องมือเพิ่มประสิทธิภาพวงจรใด

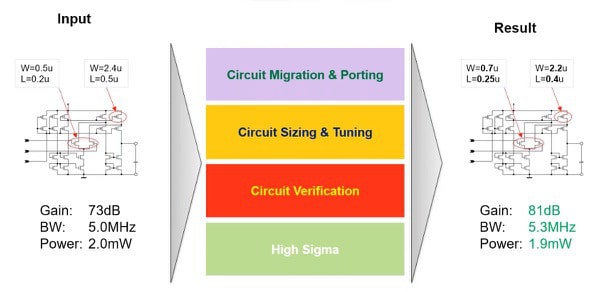

เพื่อตอบคำถามนั้น จะมีการสัมมนาผ่านเว็บที่กำลังจะเกิดขึ้น ซึ่งจัดโดย มุนเอดาบริษัท EDA เริ่มต้นในปี 2001 และทั้งหมดนี้ล้วนเป็นชื่อเครื่องมือเพิ่มประสิทธิภาพวงจรของบริษัท วิคเคดี. อินพุตเป็นรายการสุทธิของ SPICE พร้อมด้วยข้อกำหนดการออกแบบ เช่น อัตราขยาย แบนด์วิดท์ และการใช้พลังงาน เอาต์พุตเป็นรายการขนาดสุทธิที่ตรงตามหรือเกินกว่าข้อกำหนดการออกแบบ

สูตรลับของ WiCkeD คือการสร้างโมเดล Machine Learning (ML) เพื่อรัน Design Of Experiments (DOE) เพื่อคำนวณมุม PVT ที่แย่ที่สุด ค้นหาความไวของเรขาคณิตของทรานซิสเตอร์ และแม้แต่คำนวณ On Chip Variation (OCV) ) ความไว วิธีการนี้จะสร้างและอัปเดตโมเดล ML มิติสูงที่ไม่ใช่เชิงเส้นจากข้อมูลจำลอง

การมีโมเดล ML ช่วยให้เครื่องมือสามารถแก้ปัญหาความท้าทายในการเพิ่มประสิทธิภาพ จากนั้นทำการตรวจสอบขั้นสุดท้ายด้วยการรันการจำลอง SPICE มีการวนซ้ำอัตโนมัติจนกว่าจะเป็นไปตามข้อกำหนดทั้งหมด ตอนนี้ฟังดูเร็วกว่าวิธีการวนซ้ำแบบแมนนวลแบบเก่ามาก การฝึกโมเดล ML นั้นเป็นไปโดยอัตโนมัติและค่อนข้างมีประสิทธิภาพ

นักออกแบบวงจรจะได้เรียนรู้:

- จะใช้การเพิ่มประสิทธิภาพวงจรได้ที่ไหน

- วงจรประเภทใดที่เหมาะกับการปรับให้เหมาะสม

- การปรับวงจรให้เหมาะสมที่สุดจะส่งผลต่อโฟลว์การออกแบบมากน้อยเพียงใด

วิศวกรที่ STMicroelectronics ได้ใช้การเพิ่มประสิทธิภาพวงจรใน WiCkeD และ MunEDA พูดถึงผลลัพธ์เฉพาะของพวกเขาในการประหยัดเวลาและการปรับปรุงข้อกำหนดในการตอบสนอง บริษัทเพาเวอร์แอมป์ Inplay Technologies แสดงผลการปรับวงจรให้เหมาะสมจากการประชุม DAC 2018

รายละเอียดการสัมมนาผ่านเว็บ

ดูการสัมมนาผ่านเว็บในวันที่ 11 เมษายน เวลา 10 น. PDT ภายใน ลงทะเบียนออนไลน์.

บล็อกที่เกี่ยวข้อง

แชร์โพสต์นี้ผ่าน:- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/eda/326047-webinar-enhance-productivity-with-machine-learning-in-the-analog-front-end-design-flow/

- :เป็น

- $ ขึ้น

- 2001

- 2018

- a

- เกี่ยวกับเรา

- ข้าม

- ทั้งหมด

- เสมอ

- และ

- คำตอบ

- เข้าใกล้

- เมษายน

- เป็น

- At

- อัตโนมัติ

- อัตโนมัติ

- อัตโนมัติ

- กลับ

- แบนด์วิดธ์

- เพราะ

- นำ

- สร้าง

- by

- คำนวณ

- CAN

- ท้าทาย

- ชิป

- มา

- บริษัท

- การประชุม

- พิจารณา

- การบริโภค

- มุม

- มุม

- สร้าง

- ข้อมูล

- ออกแบบ

- นักออกแบบ

- DOE

- ที่มีประสิทธิภาพ

- ความพยายาม

- ช่วยให้

- แม้

- เกินกว่า

- คุ้นเคย

- เร็วขึ้น

- สุดท้าย

- หา

- ไหล

- สำหรับ

- ราคาเริ่มต้นที่

- ได้รับ

- เรขาคณิต

- ดี

- มี

- เป็นเจ้าภาพ

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- i

- การปรับปรุง

- in

- IT

- การย้ำ

- ซ้ำ

- jpg

- เรียนรู้

- การเรียนรู้

- กดไลก์

- เครื่อง

- เรียนรู้เครื่อง

- คู่มือ

- ความกว้างสูงสุด

- พบ

- ที่ประชุม

- มีคุณสมบัติตรงตาม

- วิธีการ

- ML

- แบบ

- ที่มีชื่อ

- of

- เก่า

- on

- การเพิ่มประสิทธิภาพ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- โพสต์

- อำนาจ

- กระบวนการ

- ผลผลิต

- แวว

- คำถาม

- ความต้องการ

- ผลสอบ

- วิ่ง

- วิ่ง

- เงินออม

- ลับ

- น่า

- จำลอง

- ขนาด

- โดยเฉพาะ

- ใช้จ่าย

- เครื่องเทศ

- ข้อความที่เริ่ม

- พูดคุย

- เทคโนโลยี

- ที่

- พื้นที่

- ของพวกเขา

- เวลา

- ไปยัง

- เกินไป

- เครื่องมือ

- การฝึกอบรม

- ชนิด

- การปรับปรุง

- ใช้

- ความคุ้มค่า

- การตรวจสอบ

- ผ่านทาง

- ทาง..

- webinar

- ที่

- จะ

- กับ

- ลมทะเล