นักออกแบบมีหลายเส้นทางในการสร้างความแตกต่างให้กับโซลูชัน RISC-V เส้นทางหนึ่งเปิดตัวในการปรับแต่งและส่วนขยายหลัก RISC-V ต่างๆ ตามข้อกำหนด อีกประการหนึ่งมุ่งเน้นไปที่การเลือกและการประกอบบล็อก IP ในการออกแบบระบบบนชิป (SoC) ที่สมบูรณ์รอบคอร์ RISC-V หนึ่งคอร์หรือมากกว่า ประการที่สามกำลังเกิดขึ้น: การเชื่อมต่อแกน RISC-V และบล็อก IP อื่น ๆ ด้วยเครือข่ายบนชิป (NoC) แทนที่จะเป็นโครงสร้างบัสธรรมดา และไม่ใช่เพียงระดับไฮเอนด์เท่านั้น การจับคู่คอร์ RISC-V กับ NoC จะช่วยตอบความท้าทายในการออกแบบ SoC หลายประการ ซึ่งข้อมูลจะต้องไหลอย่างมีประสิทธิภาพในปริมาณงานใดๆ โดยใช้โปรโตคอลบนชิปใดๆ

ระดับประสิทธิภาพเปลี่ยนแปลงไปตามแผนการเชื่อมต่อขั้นสูง

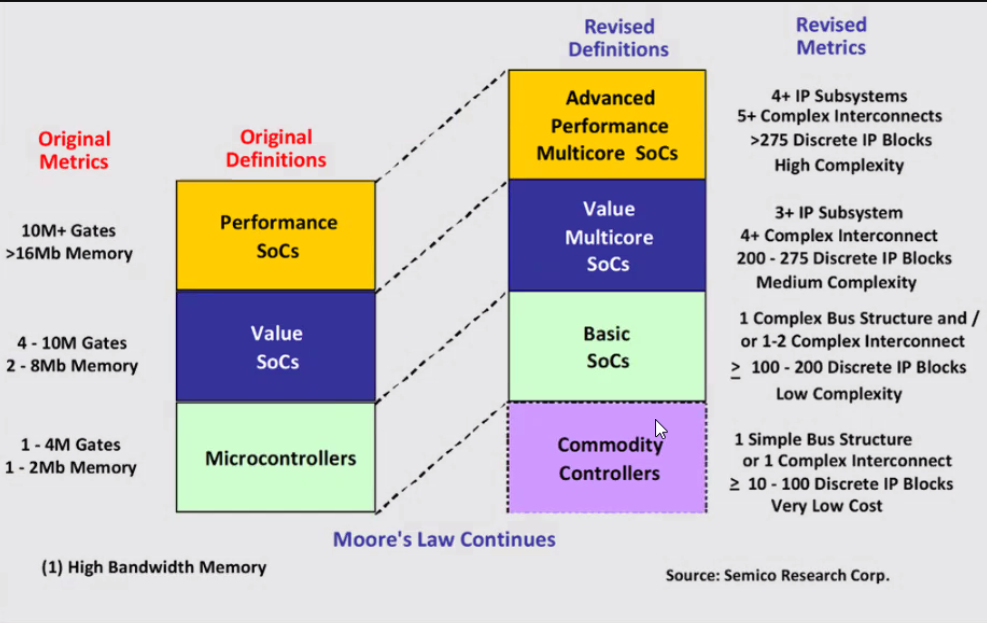

การนับเกท คอร์ และบล็อกอุปกรณ์ต่อพ่วงเพียงอย่างเดียวไม่ได้อธิบายถึงศักยภาพด้านประสิทธิภาพของการออกแบบ SoC อีกต่อไป แผนการเชื่อมต่อระหว่างกันในขณะนี้กำหนดเส้นแบ่งระหว่างระดับประสิทธิภาพของ SoC ตามการวิจัยของ Semico และระดับใหม่ได้เปิดขึ้นโดยที่การเชื่อมต่อระหว่างกันเปลี่ยนจากโครงสร้างบัสธรรมดาไปเป็นรูปแบบที่ซับซ้อนมากขึ้น

คำจำกัดความที่อัปเดตของ Semico ตระหนักถึงแรงผลักดันสามประการในการทำงาน: ความแพร่หลายของการออกแบบมัลติคอร์ แถบที่สูงขึ้นสำหรับสิ่งที่ถือว่าเป็นการออกแบบที่ซับซ้อน และเส้นเบลอที่ตามมาระหว่าง "ไมโครคอนโทรลเลอร์" และ "SoC" ในมุมมองล่าสุดของ Semico แนวคิดเรื่องเกทจะนับเป็นหน่วยเมตริกหายไป เนื่องจากคอร์โปรเซสเซอร์สมัยใหม่ตัวเดียวสามารถลากเกทจำนวนมากไปด้วยได้ ความซับซ้อนกลายเป็นหน้าที่ของการเชื่อมต่อระหว่างกัน ซึ่งแตกต่างกันไปตามระบบย่อยและบล็อก IP ที่หลากหลาย

ระดับประสิทธิภาพของ SoC, รูปภาพได้รับความอนุเคราะห์จาก Semico Research Corp.

ในกรณีที่บัสธรรมดาจะทำได้ ซึ่งน่าจะเป็นส่วนหนึ่งที่มีแกนประมวลผลตัวเดียวและอุปกรณ์ต่อพ่วงรอบการทำงานต่ำซึ่งไม่ได้แย่งชิงบัสอย่างต่อเนื่อง Semico มองเห็นระดับตัวควบคุมสินค้าโภคภัณฑ์ สิ่งใดก็ตามข้างต้นที่กลายเป็น SoC อาจมีอุปกรณ์ต่อพ่วงบางตัวที่ต่อสู้เพื่อแบนด์วิธบนชิปและความสนใจจากแกนประมวลผล ระดับ SoC ที่สูงกว่านั้นมีหลายคอร์และระบบย่อย IP หลายระบบ โดยแต่ละคอร์มีเทคโนโลยีการเชื่อมต่อที่ได้รับการปรับแต่ง

NoC จะรับโปรโตคอลและระบบย่อยมากขึ้น

RISC-V ได้ย้ายระดับประสิทธิภาพเหล่านี้ขึ้นอย่างรวดเร็วเมื่อมีแกนประมวลผลที่ทรงพลังมากขึ้นปรากฏขึ้น โดยไม่มีการนำไปใช้ที่ระดับล่างสุดของระดับ Semico อย่างไรก็ตาม นักออกแบบ RISC-V อาจมีประสบการณ์น้อยกว่าในโครงการเชื่อมต่อระหว่างกันที่ซับซ้อนซึ่งเห็นได้ในระดับที่สูงกว่า “TileLink อาจเป็นความคิดแรกสำหรับการเชื่อมต่อระหว่าง RISC-V แต่อาจเป็นเรื่องยากที่จะใช้ในสถานการณ์ที่ซับซ้อนมากขึ้น” Frank Schirrmeister รองประธานฝ่ายโซลูชันและการพัฒนาธุรกิจของ Arteris กล่าว

พลังพิเศษของ NoC คือความสามารถในการเชื่อมต่อระบบย่อยโดยใช้โปรโตคอลที่แตกต่างกัน และผู้ออกแบบ SoC มีแนวโน้มที่จะใช้งานโปรโตคอลหลายตัวแม้จะมีความซับซ้อนปานกลางก็ตาม AXI ยกระดับสนามแข่งขันสำหรับการเชื่อมต่อบล็อก IP อย่างง่าย โซลูชันมัลติคอร์ที่มีบล็อกการประมวลผลร่วมต้องการการเชื่อมโยงกันของแคช ทำให้เกิดโปรโตคอล CHI การแชร์หน่วยความจำ I/O ช่วยให้การเชื่อมต่อ CXL เร็วขึ้น “เมื่อถึงเวลาที่ต้องเพิ่มประสิทธิภาพการประมวลผลและการขนส่งร่วมกับระบบย่อยและโปรโตคอลต่างๆ NoC จะเป็นทางออกที่ดีกว่า” Schirrmeister กล่าวต่อ

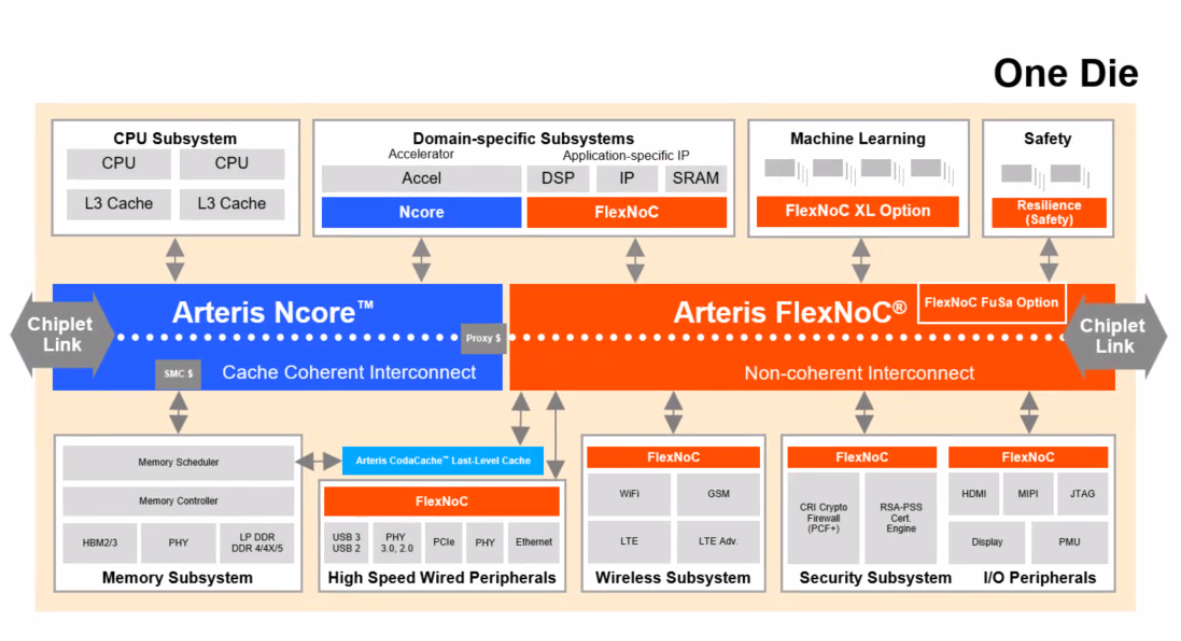

การจับคู่คอร์ RISC-V กับ NoC จะเป็นอย่างไร Tenstorrent ซึ่งเป็นลูกค้าของ Arteris ให้ข้อมูลคร่าวๆ เกี่ยวกับความเป็นไปได้ต่างๆ จุดมุ่งหมายล่าสุดของพวกเขาคือการสร้างชิปเล็ตที่นำกลับมาใช้ใหม่ได้ โดยผสมผสานคอร์ RISC-V, IP การเร่งความเร็วของแมชชีนเลิร์นนิง และอุปกรณ์ต่อพ่วงมาตรฐานที่พบในแอปพลิเคชัน Edge AI จำนวนมาก ในระดับขนาดใหญ่ การใช้งานแบบ single-die อาจมีลักษณะเหมือนแผนภาพต่อไปนี้ โดยใช้การเชื่อมต่อระหว่างกันแบบแคช Arteris Ncore และหลายส่วนของการเชื่อมต่อระหว่างกันที่ไม่สอดคล้องกัน Arteris FlexNoC

ขอบคุณภาพจาก Arteris

Smart Memory Controller (SMC) ให้การเชื่อมต่อหน่วยความจำระดับเซิร์ฟเวอร์ประสิทธิภาพสูงในแอปพลิเคชันที่ใช้หน่วยความจำมาก “ลิงก์ชิปเล็ต” ที่ไม่มีชื่ออาจเป็น UCIe ซึ่งเป็นข้อกำหนดที่ค่อนข้างใหม่ที่ได้รับการปรับให้เหมาะกับการรวมชิปเล็ตที่เข้มงวดยิ่งขึ้น เมื่อมีการเชื่อมต่อระบบย่อยใหม่เกิดขึ้น การปรับเปลี่ยนส่วนของ NoC จะสามารถจัดการได้ดีกว่าการแยกโครงสร้างทั้งชิปทั้งหมด

การจับคู่คอร์ RISC-V กับ NoC ช่วยลดความเสี่ยงและเวลาในการนำออกสู่ตลาด

หากไดอะแกรมนั้นดูซับซ้อนและเป็นไปได้ บางทีแอปพลิเคชัน RISC-V ส่วนใหญ่อาจไม่ซับซ้อนขนาดนั้นในตอนนี้ ให้พิจารณาสิ่งนี้: ชิปเล็ตกำลังผลักดันการบูรณาการให้สูงขึ้นมากอยู่แล้ว ส่วนมัลติคอร์ RISC-V ขั้นสูงของวันนี้จะเป็น SoC อันทรงคุณค่าในปีหน้า เนื่องจากนวัตกรรมก้าวไปข้างหน้า

เครื่องมือพัฒนา Arteris Ncore และ Arteris FlexNoC จะส่งสัญญาณ RTL สำหรับการนำไปใช้งาน โดยมีข้อดีหลายประการ การประมาณค่า NoC ทางกายภาพนั้นตรงไปตรงมาในเวิร์กโฟลว์ EDA การปรับพารามิเตอร์ NoC เช่น จำนวนขั้นตอนไปป์ไลน์ ก็ทำได้ด้วยการคลิกเพียงไม่กี่ครั้งในเครื่องมือ EDA การแก้ไขที่กล่าวถึงข้างต้นสำหรับการเพิ่มโปรโตคอลระบบย่อยก็สามารถทำได้ทันทีเช่นกัน “ในระดับสูง ผู้ใช้จะสามารถเข้าถึงความเชี่ยวชาญด้าน NoC ของเราได้ทันที” Schirrmeister กล่าว “ในระดับต่ำสุด เครื่องมือของเราใช้งานง่ายสำหรับความสำเร็จในการผ่านครั้งแรก และมอบเส้นทางการเติบโตสำหรับโครงการในอนาคตที่มีความทะเยอทะยานมากขึ้นด้วยการเชื่อมต่อระหว่างกันที่ซับซ้อน”

การจับคู่แกน RISC-V กับ NoC ช่วยลดความเสี่ยงที่บล็อก IP อีกหนึ่งบล็อกจะเข้าสู่การออกแบบและกระตุ้นให้เกิดการออกแบบการเชื่อมต่อระหว่างกันใหม่ทั่วทั้งชิป นอกจากนี้ยังช่วยลดเวลาในการนำออกสู่ตลาดสำหรับการออกแบบ SoC ที่ซับซ้อน เมื่อเทียบกับโครงสร้างการเชื่อมต่อที่ต้องทำด้วยตัวเอง เราไม่ได้พูดถึงประโยชน์อื่นๆ ของ NoC ที่นี่ เช่น แบนด์วิดท์และการจัดการพลังงาน แต่กรณีของ NoC ในการออกแบบ RISC-V นั้นแข็งแกร่งเพียงพิจารณาจากการผสมผสานโปรโตคอลที่หลากหลาย

เยี่ยมชมเว็บไซต์ของ Arteris สำหรับข้อมูลเพิ่มเติมเกี่ยวกับ NoC และผลิตภัณฑ์อื่น ๆ

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- a

- ความสามารถ

- ข้างบน

- การเร่งความเร็ว

- เข้า

- คล่องแคล่ว

- ตาม

- ข้าม

- เพิ่ม

- การปรับเปลี่ยน

- สูง

- ข้อได้เปรียบ

- AI

- แล้ว

- ด้วย

- ทะเยอทะยาน

- an

- และ

- อื่น

- คำตอบ

- ใด

- สิ่งใด

- ปรากฏ

- การใช้งาน

- เป็น

- รอบ

- AS

- At

- ความสนใจ

- ไป

- แบนด์วิดธ์

- บาร์

- BE

- จะกลายเป็น

- ประโยชน์ที่ได้รับ

- ดีกว่า

- ระหว่าง

- ปิดกั้น

- Blocks

- รถบัส

- ธุรกิจ

- การพัฒนาธุรกิจ

- แต่

- CAN

- กรณี

- ความท้าทาย

- เปลี่ยนแปลง

- เปลี่ยนแปลง

- ชิป

- การรวมกัน

- สินค้า

- เมื่อเทียบกับ

- สมบูรณ์

- ซับซ้อน

- ความซับซ้อน

- คำนวณ

- เชื่อมต่อ

- การเชื่อมต่อ

- การเชื่อมต่อ

- พิจารณา

- ถือว่า

- พิจารณา

- อย่างต่อเนื่อง

- อย่างต่อเนื่อง

- ตัวควบคุม

- แกน

- คอร์ป

- ได้

- การนับ

- การสร้าง

- ลูกค้า

- ข้อมูล

- กำหนด

- คำนิยาม

- ความต้องการ

- ออกแบบ

- นักออกแบบ

- การออกแบบ

- พัฒนาการ

- เครื่องมือในการพัฒนา

- ต่าง

- ยาก

- กล่าวถึง

- หลาย

- do

- การขับขี่

- แต่ละ

- ง่าย

- ขอบ

- อย่างมีประสิทธิภาพ

- ออกมา

- กากกะรุน

- ปลาย

- การป้อน

- ทั้งหมด

- แม้

- ประสบการณ์

- ความชำนาญ

- ส่วนขยาย

- เร็วขึ้น

- สองสาม

- สนาม

- ศึก

- ชื่อจริง

- ไหล

- โฟกัส

- มุ่งเน้นไปที่

- ดังต่อไปนี้

- สำหรับ

- กองกำลัง

- พบ

- ตรงไปตรงมา

- ราคาเริ่มต้นที่

- ฟังก์ชัน

- อนาคต

- ได้รับ

- เกตส์

- ให้

- เหลือบ

- รับ

- การเจริญเติบโต

- มี

- ช่วย

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- จุดสูง

- ประสิทธิภาพสูง

- สูงกว่า

- อย่างไรก็ตาม

- HTTPS

- ภาพ

- ทันที

- การดำเนินงาน

- in

- ข้อมูล

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- แทน

- บูรณาการ

- เชื่อมต่อกัน

- การเชื่อมต่อระหว่างกัน

- เข้าไป

- IP

- IT

- ITS

- เพียงแค่

- ล่าสุด

- การเปิดตัว

- น้อยที่สุด

- น้อยลง

- กดไลก์

- น่าจะ

- Line

- เส้น

- อีกต่อไป

- ดู

- ดูเหมือน

- LOOKS

- ต่ำ

- ลด

- การจัดการ

- หลาย

- ความกว้างสูงสุด

- อาจ..

- อาจจะ

- หน่วยความจำ

- กล่าวถึง

- เมตริก

- ผสม

- ปานกลาง

- ทันสมัย

- การปรับเปลี่ยน

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ย้าย

- มาก

- หลาย

- ต้อง

- ใหม่

- ถัดไป

- ไม่

- ความคิด

- ตอนนี้

- จำนวน

- of

- on

- ONE

- เปิด

- การปรับให้เหมาะสม

- or

- อื่นๆ

- ของเรา

- เอาท์พุต

- ก้าว

- การจับคู่

- พารามิเตอร์

- ส่วนหนึ่ง

- เส้นทาง

- ต่อ

- การปฏิบัติ

- อุปกรณ์ต่อพ่วง

- อุปกรณ์ต่อพ่วง

- กายภาพ

- เลือก

- คัดสรร

- ท่อ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- เล่น

- เล่น

- ความเป็นไปได้

- โพสต์

- ที่มีศักยภาพ

- อำนาจ

- ที่มีประสิทธิภาพ

- หน่วยประมวลผล

- ผลิตภัณฑ์

- โครงการ

- โปรโตคอล

- โปรโตคอล

- ให้

- ให้

- การให้

- อย่างรวดเร็ว

- อย่างง่ายดาย

- เมื่อเร็ว ๆ นี้

- ตระหนักถึงความ

- การออกแบบ

- ลด

- สัมพัทธ์

- การวิจัย

- นำมาใช้ใหม่

- ขวา

- Ripple

- ขึ้น

- ความเสี่ยง

- วิ่ง

- s

- พูดว่า

- ขนาด

- สถานการณ์

- รูปแบบ

- Section

- เห็น

- เห็น

- กลุ่ม

- การเลือก

- หลาย

- รูปร่าง

- ใช้งานร่วมกัน

- ง่าย

- ตั้งแต่

- เดียว

- สมาร์ท

- ทางออก

- โซลูชัน

- บาง

- ซับซ้อน

- สเปค

- ขั้นตอน

- มาตรฐาน

- ซื่อตรง

- แข็งแรง

- โครงสร้าง

- โครงสร้าง

- ภายหลัง

- ความสำเร็จ

- อย่างเช่น

- มหาอำนาจ

- เทคโนโลยี

- กว่า

- ที่

- พื้นที่

- ของพวกเขา

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- ที่สาม

- นี้

- คิดว่า

- สาม

- ชั้น

- ความสัมพันธ์

- ที่เข้มงวดมากขึ้น

- เวลา

- ไปยัง

- วันนี้

- ร่วมกัน

- เครื่องมือ

- การขนส่ง

- วิกฤติ

- ไม่มีชื่อ

- ให้กับคุณ

- ใช้

- ผู้ใช้

- การใช้

- ความคุ้มค่า

- ต่างๆ

- แตกต่างกัน

- ผ่านทาง

- รายละเอียด

- vp

- we

- Website

- อะไร

- ความหมายของ

- เมื่อ

- จะ

- กับ

- งาน

- เวิร์กโฟลว์

- ลมทะเล