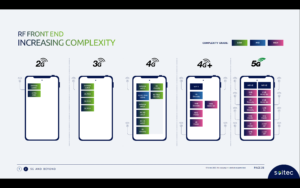

ในการเดินขบวนไปสู่ระบบพลังงานที่มีความสามารถมากขึ้น เร็วขึ้น เล็กลง และต่ำกว่า กฎของมัวร์ทำให้ซอฟต์แวร์ใช้งานได้ฟรีมานานกว่า 30 ปีหรือประมาณนั้นเกี่ยวกับวิวัฒนาการกระบวนการเซมิคอนดักเตอร์เพียงอย่างเดียว ฮาร์ดแวร์ประมวลผลส่งมอบประสิทธิภาพ/พื้นที่/พลังงานที่ดีขึ้นทุกปี ช่วยให้ซอฟต์แวร์ขยายความซับซ้อนและมอบความสามารถได้มากขึ้นโดยไม่มีข้อเสีย จากนั้นการชนะแบบง่าย ๆ ก็กลายเป็นเรื่องง่ายน้อยลง กระบวนการขั้นสูงเพิ่มเติมยังคงให้จำนวนเกตที่สูงขึ้นต่อหน่วยพื้นที่ แต่ประสิทธิภาพและกำลังที่เพิ่มขึ้นเริ่มลดลง เนื่องจากความคาดหวังด้านนวัตกรรมของเราไม่ได้หยุดลง ความก้าวหน้าทางสถาปัตยกรรมฮาร์ดแวร์จึงมีความสำคัญมากขึ้นในการรับมือกับจุดอ่อน

ไดรเวอร์สำหรับการเพิ่มจำนวนคอร์

ขั้นตอนแรกในทิศทางนี้ใช้ CPU แบบมัลติคอร์เพื่อเร่งความเร็วปริมาณงานทั้งหมดโดยเธรดหรือการจำลองเสมือนของงานที่เกิดขึ้นพร้อมกันข้ามคอร์ ลดพลังงานตามต้องการโดยการไม่ทำงานหรือปิดคอร์ที่ไม่ได้ใช้งาน มัลติคอร์ถือเป็นมาตรฐานในปัจจุบัน และแนวโน้มของมัลติคอร์ (แม้กระทั่ง CPU บนชิปที่เพิ่มมากขึ้น) ก็ปรากฏชัดอยู่แล้วในตัวเลือกอินสแตนซ์เซิร์ฟเวอร์ที่มีอยู่ในแพลตฟอร์มคลาวด์จาก AWS, Azure, Alibaba และอื่นๆ

สถาปัตยกรรมแบบมัลติคอร์/หลายคอร์เป็นก้าวไปข้างหน้า แต่การทำงานแบบขนานผ่านคลัสเตอร์ CPU นั้นมีความหยาบและมีประสิทธิภาพและขีดจำกัดพลังงานของตัวเอง ต้องขอบคุณกฎของอัมดาห์ล สถาปัตยกรรมมีความหลากหลายมากขึ้น โดยเพิ่มตัวเร่งสำหรับรูปภาพ เสียง และความต้องการเฉพาะอื่นๆ ตัวเร่งความเร็ว AI ยังผลักดันความเท่าเทียมแบบละเอียด โดยย้ายไปยังอาร์เรย์ซิสโตลิกและเทคนิคเฉพาะโดเมนอื่นๆ ซึ่งทำงานได้ค่อนข้างดีจนกระทั่ง ChatGPT ปรากฏขึ้นพร้อมกับพารามิเตอร์ 175 พันล้านพารามิเตอร์ โดย GPT-3 พัฒนาเป็น GPT-4 ด้วยพารามิเตอร์ 100 ล้านล้านพารามิเตอร์ ซึ่งเป็นลำดับขนาดที่ซับซ้อนกว่าระบบ AI ในปัจจุบัน ทำให้ยังมีฟีเจอร์การเร่งความเร็วพิเศษเพิ่มเติมภายในตัวเร่งความเร็ว AI

ในด้านอื่น ระบบเซ็นเซอร์หลายตัวในการใช้งานด้านยานยนต์กำลังรวมเข้ากับ SoC เดี่ยวเพื่อปรับปรุงการรับรู้สภาพแวดล้อมและ PPA ที่ได้รับการปรับปรุง ในที่นี้ ระดับใหม่ของความเป็นอิสระในยานยนต์ขึ้นอยู่กับการหลอมรวมอินพุตจากเซ็นเซอร์หลายประเภทภายในอุปกรณ์เดียว ในระบบย่อยที่จำลองแบบ 2X, 4X หรือ 8X

จากข้อมูลของ Michał Siwinski (CMO ของ Arteris) การสุ่มตัวอย่างการสนทนาเป็นเวลาหนึ่งเดือนกับทีมออกแบบหลายทีมในแอปพลิเคชันที่หลากหลาย แสดงให้เห็นว่าทีมเหล่านั้นกำลังหันมาใช้จำนวนคอร์ที่สูงขึ้นอย่างแข็งขันเพื่อให้บรรลุเป้าหมายด้านความสามารถ ประสิทธิภาพ และพลังงาน เขาบอกฉันว่าพวกเขาเห็นแนวโน้มนี้กำลังเร่งตัวขึ้นเช่นกัน ความก้าวหน้าของกระบวนการยังคงช่วยในการนับประตู SoC แต่ความรับผิดชอบในการบรรลุประสิทธิภาพและเป้าหมายด้านพลังงานขณะนี้อยู่ในมือของสถาปนิกอย่างมั่นคง

แกนประมวลผลมากขึ้น การเชื่อมต่อระหว่างกันมากขึ้น

จำนวนแกนประมวลผลที่มากขึ้นบนชิปหมายถึงการเชื่อมต่อข้อมูลที่มากขึ้นระหว่างแกนประมวลผลเหล่านั้น ภายในตัวเร่งความเร็วระหว่างองค์ประกอบการประมวลผลที่อยู่ใกล้เคียง ไปยังแคชในเครื่อง ไปยังตัวเร่งความเร็วสำหรับเมทริกซ์กระจัดกระจาย และการจัดการพิเศษอื่นๆ เพิ่มการเชื่อมต่อแบบลำดับชั้นระหว่างไทล์คันเร่งและบัสระดับระบบ เพิ่มการเชื่อมต่อสำหรับการจัดเก็บน้ำหนักบนชิป การบีบอัด การออกอากาศ การรวบรวม และการบีบอัดซ้ำ เพิ่มการเชื่อมต่อ HBM สำหรับแคชการทำงาน เพิ่มเครื่องยนต์ฟิวชันหากจำเป็น

คลัสเตอร์ควบคุมที่ใช้ CPU จะต้องเชื่อมต่อกับแต่ละระบบย่อยที่จำลองแบบเหล่านั้นและกับฟังก์ชันปกติทั้งหมด เช่น โคเดก การจัดการหน่วยความจำ เกาะปลอดภัย และรูทของความไว้วางใจ หากเหมาะสม UCIe หากใช้งานหลายชิปเล็ต PCIe สำหรับ I/O แบนด์วิธสูง และอีเธอร์เน็ตหรือไฟเบอร์สำหรับเครือข่าย

นั่นเป็นการเชื่อมโยงถึงกันอย่างมาก โดยมีผลกระทบโดยตรงต่อความสามารถทางการตลาดของผลิตภัณฑ์ ในกระบวนการที่ต่ำกว่า 16 นาโนเมตร ขณะนี้โครงสร้างพื้นฐาน NoC มีส่วนช่วยในพื้นที่ 10-12% ที่สำคัญยิ่งกว่านั้น เนื่องจากเป็นทางหลวงการสื่อสารระหว่างคอร์ จึงสามารถส่งผลกระทบอย่างมีนัยสำคัญต่อประสิทธิภาพและพลังงาน มีอันตรายอย่างแท้จริงที่การใช้งานที่ไม่เหมาะสมจะสิ้นเปลืองประสิทธิภาพของสถาปัตยกรรมที่คาดหวังและพลังงานที่เพิ่มขึ้น หรือที่แย่กว่านั้นคือส่งผลให้มีการออกแบบลูปใหม่จำนวนมากมาบรรจบกัน แต่การค้นหาการใช้งานที่ดีในแผนผังชั้น SoC ที่ซับซ้อนยังคงขึ้นอยู่กับการปรับให้เหมาะสมแบบลองผิดลองถูกที่ช้าในตารางการออกแบบที่แน่นอยู่แล้ว เราจำเป็นต้องก้าวกระโดดไปสู่การออกแบบ NoC ที่รับรู้ทางกายภาพ เพื่อรับประกันประสิทธิภาพเต็มรูปแบบและการสนับสนุนด้านพลังงานจากลำดับชั้น NoC ที่ซับซ้อน และเราจำเป็นต้องทำให้การปรับให้เหมาะสมเหล่านี้เร็วขึ้น

การออกแบบ NoC ที่รับรู้ทางกายภาพช่วยให้กฎของมัวร์เป็นไปตามแผน

กฎของมัวร์อาจไม่ตายตัว แต่ความก้าวหน้าในด้านประสิทธิภาพและพลังงานในปัจจุบันมาจากสถาปัตยกรรมและการเชื่อมต่อระหว่าง NoC มากกว่าจากกระบวนการ สถาปัตยกรรมกำลังผลักดันคอร์ตัวเร่งความเร็วมากขึ้น ตัวเร่งความเร็วภายในตัวเร่งความเร็วมากขึ้น และการจำลองระบบย่อยบนชิปมากขึ้น ทั้งหมดนี้เพิ่มความซับซ้อนของการเชื่อมต่อระหว่างกันบนชิป เนื่องจากการออกแบบเพิ่มจำนวนคอร์และย้ายไปยังรูปทรงเรขาคณิตของการประมวลผลที่ 16 นาโนเมตรและต่ำกว่า การเชื่อมต่อระหว่างกัน NoC จำนวนมากซึ่งครอบคลุม SoC และระบบย่อยจะสามารถรองรับศักยภาพสูงสุดของการออกแบบที่ซับซ้อนเหล่านี้ได้เท่านั้น หากนำไปใช้อย่างเหมาะสมที่สุดกับข้อจำกัดทางกายภาพและเวลา - ผ่านเครือข่ายที่รับรู้ทางกายภาพ ในการออกแบบชิป

หากคุณกังวลเกี่ยวกับแนวโน้มเหล่านี้ คุณอาจต้องการเรียนรู้เพิ่มเติมเกี่ยวกับเทคโนโลยี Arteris FlexNoC 5 IP ที่นี่.

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :เป็น

- $ ขึ้น

- 100

- a

- เกี่ยวกับเรา

- เร่งความเร็ว

- เร่ง

- การเร่งความเร็ว

- คันเร่ง

- เร่ง

- ข้าม

- อย่างกระตือรือร้น

- สูง

- ความก้าวหน้า

- กับ

- AI

- ระบบ AI

- อาลีบาบา

- ทั้งหมด

- การอนุญาต

- แล้ว

- และ

- ปรากฏ

- การใช้งาน

- เหมาะสม

- สถาปัตยกรรม

- เป็น

- AREA

- AS

- At

- เสียง

- ยานยนต์

- ใช้ได้

- ความตระหนัก

- AWS

- สีฟ้า

- แบนด์วิดธ์

- BE

- กลายเป็น

- ด้านล่าง

- ระหว่าง

- พันล้าน

- ออกอากาศ

- รถบัส

- by

- แคช

- CAN

- สามารถ

- ChatGPT

- ชิป

- เมฆ

- Cluster

- CMO

- อย่างไร

- การสื่อสาร

- ซับซ้อน

- ความซับซ้อน

- คำนวณ

- พร้อมกัน

- เชื่อมต่อ

- การเชื่อมต่อ

- การเชื่อมต่อ

- ผลที่ตามมา

- ข้อ จำกัด

- อย่างต่อเนื่อง

- ควบคุม

- ลู่

- แกน

- ซีพียู

- อันตราย

- ข้อมูล

- ตาย

- ส่งมอบ

- ส่ง

- ขึ้นอยู่กับ

- ออกแบบ

- การออกแบบ

- เครื่อง

- ต่าง

- โดยตรง

- ทิศทาง

- การอภิปราย

- ลง

- ข้อเสีย

- แต่ละ

- ก่อน

- องค์ประกอบ

- เครื่องยนต์

- สิ่งแวดล้อม

- แม้

- ทุกๆ

- วิวัฒนาการ

- การพัฒนา

- แสดง

- ความคาดหวัง

- ที่คาดหวัง

- เร็วขึ้น

- คุณสมบัติ

- หา

- แน่นหนา

- สำหรับ

- ข้างหน้า

- ฟรี

- ราคาเริ่มต้นที่

- ด้านหน้า

- เต็ม

- ฟังก์ชั่น

- การผสม

- กําไร

- เป้าหมาย

- ดี

- รับประกัน

- การจัดการ

- มือ

- ฮาร์ดแวร์

- มี

- ช่วย

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- จุดสูง

- สูงกว่า

- ทางหลวง

- HTTPS

- ภาพ

- ส่งผลกระทบ

- การดำเนินงาน

- การดำเนินการ

- สำคัญ

- การปรับปรุง

- in

- ไม่ได้ใช้งาน

- เพิ่ม

- ที่เพิ่มขึ้น

- โครงสร้างพื้นฐาน

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- ตัวอย่าง

- การบูรณาการ

- IP

- เกาะ

- IT

- ITS

- กระโดด

- กฏหมาย

- เรียนรู้

- ชั้น

- ระดับ

- ขีด จำกัด

- ในประเทศ

- Lot

- ทำ

- การจัดการ

- มีนาคม

- มดลูก

- ความกว้างสูงสุด

- พบ

- ที่ประชุม

- หน่วยความจำ

- ตัวชี้วัด

- อาจ

- เดือน

- ข้อมูลเพิ่มเติม

- ย้าย

- การย้าย

- หลาย

- จำเป็นต้อง

- จำเป็น

- ความต้องการ

- เครือข่าย

- เครือข่าย

- ใหม่

- มากมาย

- of

- on

- Options

- คำสั่งซื้อ

- อื่นๆ

- ผลิตภัณฑ์อื่นๆ

- ของตนเอง

- พารามิเตอร์

- การปฏิบัติ

- กายภาพ

- ทางร่างกาย

- แพลตฟอร์ม

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- โพสต์

- ที่มีศักยภาพ

- อำนาจ

- powering

- สวย

- กระบวนการ

- กระบวนการ

- การประมวลผล

- ผลิตภัณฑ์

- หมดจด

- ผลักดัน

- ใจเร่งเร้า

- พิสัย

- ค่อนข้าง

- จริง

- ลด

- การจำลองแบบ

- การทำซ้ำ

- ความรับผิดชอบ

- ผล

- ขี่

- ราก

- ความปลอดภัย

- สารกึ่งตัวนำ

- สำคัญ

- ตั้งแต่

- เดียว

- หย่อน

- ช้า

- มีขนาดเล็กกว่า

- So

- ซอฟต์แวร์

- เมทริกซ์กระจัดกระจาย

- เฉพาะ

- ไฟฉายสว่างจ้า

- มาตรฐาน

- ข้อความที่เริ่ม

- ขั้นตอน

- ยังคง

- หยุด

- การเก็บรักษา

- ชี้ให้เห็นถึง

- สนับสนุน

- ระบบ

- ระบบ

- งาน

- ทีม

- เทคนิค

- เทคโนโลยี

- บอก

- ที่

- พื้นที่

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- ตลอด

- ปริมาณงาน

- ระยะเวลา

- ไปยัง

- ในวันนี้

- วันนี้

- รวม

- เทรนด์

- แนวโน้ม

- ล้านล้าน

- วางใจ

- การหมุน

- ชนิด

- ภายใต้

- หน่วย

- ผ่านทาง

- น้ำหนัก

- ดี

- ที่

- กว้าง

- ช่วงกว้าง

- จะ

- ชนะ

- กับ

- ภายใน

- การทำงาน

- ปี

- ปี

- ลมทะเล