ในช่วงทศวรรษปี 2010 ประโยชน์ของกฎของมัวร์เริ่มที่จะขาดหายไป กฎของมัวร์ระบุว่าความหนาแน่นของทรานซิสเตอร์เพิ่มขึ้นสองเท่าทุก ๆ สองปี ค่าใช้จ่ายในการประมวลผลจะลดลง 50% ที่สอดคล้องกัน การเปลี่ยนแปลงกฎของมัวร์เกิดจากการเพิ่มความซับซ้อนในการออกแบบวิวัฒนาการของโครงสร้างทรานซิสเตอร์จากอุปกรณ์ระนาบไปสู่ Finfets Finfet จำเป็นต้องมีรูปแบบหลายรูปแบบสำหรับการพิมพ์หินเพื่อให้ได้ขนาดอุปกรณ์ที่ต่ำกว่าโหนด 20 นาโนเมตร

ในช่วงต้นทศวรรษนี้ ความต้องการด้านคอมพิวเตอร์ได้เพิ่มสูงขึ้น ส่วนใหญ่เนื่องมาจากการขยายตัวของศูนย์ข้อมูล และเนื่องจากปริมาณของข้อมูลที่ถูกสร้างขึ้นและประมวลผล ในความเป็นจริง การนำปัญญาประดิษฐ์ (AI) มาใช้และเทคนิคต่างๆ เช่น การเรียนรู้ของเครื่อง (ML) ถูกนำมาใช้ในการประมวลผลข้อมูลที่เพิ่มมากขึ้นเรื่อยๆ และทำให้เซิร์ฟเวอร์เพิ่มความสามารถในการประมวลผลอย่างมีนัยสำคัญ

เซิร์ฟเวอร์ได้เพิ่มคอร์ CPU มากขึ้น ได้รวม GPU ขนาดใหญ่ที่ใช้สำหรับ ML โดยเฉพาะ ไม่ได้ใช้สำหรับกราฟิกอีกต่อไป และได้ฝังตัวเร่งความเร็ว ASIC AI แบบกำหนดเองหรือตัวประมวลผล AI เสริมที่ใช้ FPGA การออกแบบชิป AI ในยุคแรกๆ ถูกนำมาใช้โดยใช้ SoC แบบเสาหินที่มีขนาดใหญ่กว่า ซึ่งบางอันมีขนาดถึงขีดจำกัดที่กำหนดโดยเรติเคิลประมาณ 700 มม.2.

ณ จุดนี้ การแยกออกเป็น SoC ที่เล็กลงบวกกับการประมวลผลและชิปเล็ต IO ต่างๆ ดูเหมือนจะเป็นวิธีแก้ปัญหาที่ถูกต้อง ผู้ผลิตชิปหลายราย เช่น Intel, AMD หรือ Xilinx ได้เลือกตัวเลือกนี้สำหรับผลิตภัณฑ์ที่เข้าสู่การผลิต ในเอกสารไวท์เปเปอร์ที่ยอดเยี่ยมจาก The Linley Group เรื่อง “Chiplets ได้รับการนำไปใช้อย่างรวดเร็ว: ทำไมชิปขนาดใหญ่ถึงมีขนาดเล็ก” แสดงให้เห็นว่าตัวเลือกนี้นำไปสู่ต้นทุนที่ดีกว่าเมื่อเปรียบเทียบกับ SoC แบบเสาหิน เนื่องจากมีผลกระทบต่อผลผลิตที่ใหญ่กว่า

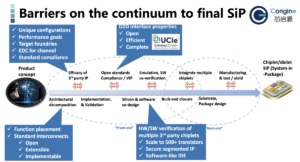

ผลกระทบที่สำคัญของแนวโน้มนี้ต่อผู้จำหน่าย IP ส่วนใหญ่อยู่ที่ฟังก์ชันการเชื่อมต่อระหว่างกันที่ใช้เพื่อเชื่อมโยง SoC และชิปเล็ต ณ จุดนี้ (ไตรมาสที่ 3 ปี 2021) มีการใช้โปรโตคอลหลายรายการ โดยอุตสาหกรรมพยายามสร้างมาตรฐานที่เป็นทางการสำหรับหลายโปรโตคอล

มาตรฐาน D2D ชั้นนำในปัจจุบันประกอบด้วย i) Advanced Interface Bus (AIB, AIB2) ที่ Intel กำหนดในตอนแรก และตอนนี้ได้เสนอการใช้งานแบบปลอดค่าลิขสิทธิ์ ii) หน่วยความจำแบนด์วิธสูง (HBM) โดยที่ DRAM ตายจะซ้อนกันที่ด้านบนของซิลิคอนอินเตอร์โพเซอร์ และเชื่อมต่อกันโดยใช้ TSV, iii) กลุ่มย่อย Open Domain-Specific Architecture (ODSA) ซึ่งเป็นกลุ่มอุตสาหกรรม ได้กำหนดอินเทอร์เฟซอื่นอีกสองอินเทอร์เฟซ ได้แก่ Bunch of Wires (BoW) และ OpenHBI

การออกแบบชิปเล็ตที่แตกต่างกันช่วยให้เราสามารถกำหนดเป้าหมายการใช้งานหรือกลุ่มตลาดที่แตกต่างกันโดยการปรับเปลี่ยนหรือเพิ่มเฉพาะชิปเล็ตที่เกี่ยวข้อง ขณะเดียวกันก็รักษาส่วนที่เหลือของระบบไว้ไม่เปลี่ยนแปลง การพัฒนาใหม่ๆ สามารถออกสู่ตลาดได้รวดเร็วยิ่งขึ้นด้วยการลงทุนที่ลดลงอย่างมาก เนื่องจากการออกแบบใหม่จะส่งผลกระทบต่อพื้นผิวบรรจุภัณฑ์ที่ใช้กักชิปเล็ตเท่านั้น

ตัวอย่างเช่น ชิปประมวลผลสามารถออกแบบใหม่จาก TSMC 5nm เป็น TSMC 3nm เพื่อรวมแคช L1 ที่ใหญ่ขึ้นหรือคอร์ CPU ที่มีประสิทธิภาพสูงกว่า ในขณะที่ยังคงรักษาส่วนที่เหลือของระบบไว้ไม่เปลี่ยนแปลง ที่ฝั่งตรงข้ามของสเปกตรัม มีเพียงชิปเล็ตที่รวม SerDes เท่านั้นที่สามารถออกแบบใหม่เพื่อให้ได้อัตราที่เร็วขึ้นบนโหนดกระบวนการใหม่ที่นำเสนอแบนด์วิดท์ IO ที่มากขึ้นเพื่อการวางตำแหน่งทางการตลาดที่ดีขึ้น

Intel PVC เป็นตัวอย่างที่สมบูรณ์แบบของการบูรณาการแบบต่างกัน (ชิปเล็ตฟังก์ชันต่างๆ, CPU, สวิตช์ ฯลฯ) ที่เราเรียกได้ว่าบูรณาการในแนวตั้ง เมื่อผู้ผลิตชิปรายเดียวกันเป็นเจ้าของส่วนประกอบของชิปเล็ตต่างๆ (ยกเว้นอุปกรณ์หน่วยความจำ)

ผู้ผลิตชิปที่พัฒนา SoC สำหรับแอปพลิเคชันระดับไฮเอนด์ เช่น HPC, ศูนย์ข้อมูล, AI หรือระบบเครือข่าย มีแนวโน้มว่าจะนำสถาปัตยกรรมชิปเล็ตมาใช้ในช่วงแรกๆ ฟังก์ชันเฉพาะ เช่น SRAM สำหรับแคช L3 ที่ใหญ่กว่า หรือตัวเร่งความเร็ว AI มาตรฐานอีเธอร์เน็ต, PCIe หรือ CXL ควรเป็นตัวเลือกอินเทอร์เฟซแรกสำหรับการออกแบบชิปเล็ต

เมื่อผู้ใช้งานกลุ่มแรกเหล่านี้ได้แสดงให้เห็นถึงความถูกต้องของชิปเล็ตที่ต่างกันโดยใช้ประโยชน์จากโมเดลธุรกิจที่แตกต่างกันหลายแบบ และเห็นได้ชัดว่ามีความเป็นไปได้ในการผลิตสำหรับการทดสอบและบรรจุภัณฑ์ มันจะสร้างระบบนิเวศที่มีความสำคัญต่อการสนับสนุนเทคโนโลยีใหม่นี้ ณ จุดนี้ เราคาดหวังได้ว่าจะมีการนำไปใช้ในตลาดในวงกว้าง ไม่เพียงแต่สำหรับแอปพลิเคชันที่มีประสิทธิภาพสูงเท่านั้น

เราจินตนาการได้ว่าผลิตภัณฑ์ที่ต่างกันสามารถไปได้ไกลกว่านี้ หากผู้ผลิตชิปจะเปิดตัวระบบที่ทำจากชิปเล็ตต่างๆ ที่กำหนดเป้าหมายการทำงานด้านการประมวลผลและ IO ในตลาด แนวทางนี้ทำให้ต้องมีการรวมโปรโตคอล D2D เนื่องจากผู้จำหน่าย IP ที่นำเสนอชิปเล็ตที่มีโปรโตคอล D2D ภายในองค์กรไม่น่าสนใจสำหรับอุตสาหกรรม

สิ่งที่คล้ายคลึงกันคือการสร้าง SoC ในปี 2000 ซึ่งบริษัทเซมิคอนดักเตอร์เปลี่ยนไปสู่การบูรณาการ IP การออกแบบต่างๆ ที่มาจากแหล่งที่มาที่แตกต่างกัน ผู้จำหน่าย IP ในยุค 2000 จะกลายเป็นผู้จำหน่าย Chiplet ในยุค 2020 อย่างหลีกเลี่ยงไม่ได้ สำหรับฟังก์ชันบางอย่าง เช่น SerDes ขั้นสูงหรือโปรโตคอลที่ซับซ้อน เช่น PCIe, Ethernet หรือ CXL ผู้จำหน่าย IP มีความรู้ที่ดีที่สุดในการใช้งานบนซิลิคอน

สำหรับ IP การออกแบบที่ซับซ้อน แม้ว่าจะมีการดำเนินการตรวจสอบการจำลองก่อนจัดส่งให้กับลูกค้า ผู้จำหน่ายจะต้องตรวจสอบ IP บนซิลิคอนเพื่อรับประกันประสิทธิภาพ สำหรับ IP ดิจิทัล ฟังก์ชันนี้สามารถนำไปใช้ใน FPGA ได้ เนื่องจากเร็วกว่าและราคาถูกกว่าการสร้างชิปทดสอบมาก สำหรับ IP แบบสัญญาณผสม เช่น PHY ที่ใช้ SerDes ผู้จำหน่ายจะเลือกตัวเลือกทดสอบชิป (TC) ซึ่งอนุญาตให้ซิลิคอนกำหนดลักษณะเฉพาะของ IP ในซิลิคอนก่อนจัดส่งให้กับลูกค้า

แม้ว่าชิปเล็ตจะไม่ได้เป็นเพียง TC เนื่องจากจะต้องได้รับการทดสอบและรับรองอย่างครอบคลุมก่อนนำไปใช้ในภาคสนาม แต่ผู้ขายจะต้องดำเนินการเพิ่มเติมเพื่อพัฒนาชิปเล็ตที่ใช้งานจริงในปริมาณที่น้อยกว่ามาก กล่าวอีกนัยหนึ่ง ผู้จำหน่าย IP อยู่ในตำแหน่งที่ดีที่สุดในการเปิดตัวชิปเล็ตที่สร้างจาก IP ของเขาเองอย่างรวดเร็ว และเสนอ TTM ที่ดีที่สุดที่เป็นไปได้และลดความเสี่ยงให้เหลือน้อยที่สุด

โมเดลธุรกิจสำหรับการบูรณาการแบบต่างกันนั้นสนับสนุนชิปเล็ตต่างๆ ที่ผลิตโดยผู้จำหน่าย IP ที่เกี่ยวข้อง (เช่น ARM สำหรับชิปเล็ต CPU ที่ใช้ ARM, Si-Five สำหรับชิปเล็ตประมวลผลที่ใช้ Risc-V และ Alphawave สำหรับชิปเล็ต SerDes ความเร็วสูง) เนื่องจาก พวกเขาเป็นเจ้าของ Design IP

สิ่งเหล่านี้ไม่ได้ขัดขวางผู้ผลิตชิปในการออกแบบชิปเล็ตของตนเองและแหล่งที่มาของ IP การออกแบบที่ซับซ้อนเพื่อปกป้องสถาปัตยกรรมที่เป็นเอกลักษณ์ของตนหรือใช้การเชื่อมต่อระหว่างกันที่ทำเอง เช่นเดียวกับ SoC Design IP ในปี 2000 การซื้อหรือการตัดสินใจซื้อชิปเล็ตจะถูกถ่วงน้ำหนักระหว่างการปกป้องความสามารถหลักและการจัดหาฟังก์ชันที่ไม่สร้างความแตกต่าง

เราได้เห็นแล้วว่าการเติบโตของธุรกิจ Design IP ในอดีตและสมัยใหม่นับตั้งแต่ช่วงปี 2000 ได้รับการสนับสนุนโดยการนำแหล่งภายนอกมาใช้อย่างต่อเนื่อง ทั้งสองรุ่นจะอยู่ร่วมกัน (ชิปเล็ตที่ออกแบบภายในบริษัทหรือโดยผู้จำหน่าย IP) แต่ประวัติศาสตร์ได้แสดงให้เห็นว่าในที่สุดการตัดสินใจซื้อก็เข้ามาแทนที่

ขณะนี้มีความเห็นเป็นเอกฉันท์ในอุตสาหกรรมว่าการมุ่งเน้นอย่างบ้าคลั่งในการบรรลุกฎของมัวร์นั้นใช้ไม่ได้อีกต่อไปสำหรับโหนดเทคโนโลยีขั้นสูง เช่น 7 นาโนเมตรและต่ำกว่า การรวมชิปยังคงเกิดขึ้น โดยมีการเพิ่มทรานซิสเตอร์มากขึ้นต่อตารางมม. ที่โหนดเทคโนโลยีใหม่ทุกอัน อย่างไรก็ตาม ต้นทุนต่อทรานซิสเตอร์ก็เพิ่มขึ้นสูงขึ้นทุกโหนดใหม่เช่นกัน

เทคโนโลยี Chiplet เป็นความคิดริเริ่มหลักในการขับเคลื่อนการบูรณาการที่เพิ่มขึ้นสำหรับ SoC หลัก ในขณะที่ใช้โหนดเก่าสำหรับฟังก์ชันอื่นๆ กลยุทธ์แบบไฮบริดนี้ลดทั้งต้นทุนและความเสี่ยงด้านการออกแบบที่เกี่ยวข้องกับการบูรณาการ Design IP อื่นๆ เข้ากับ SoC หลักโดยตรง

IPnest เชื่อว่าแนวโน้มนี้จะมีผลกระทบหลักสองประการต่อธุรกิจอินเทอร์เฟซ IP ประการหนึ่งคือการเติบโตที่แข็งแกร่งของรายได้ D2D IP ในไม่ช้า (2021-2025) และอีกอย่างคือการสร้างตลาดชิปเล็ตที่แตกต่างกันเพื่อเพิ่มซิลิคอนระดับไฮเอนด์ ตลาดไอพี.

ตลาดนี้คาดว่าจะประกอบด้วยฟังก์ชันโปรโตคอลที่ซับซ้อน เช่น PCIe, CXL หรือ Ethernet ผู้จำหน่าย IP ที่ให้บริการ IP อินเทอร์เฟซที่รวมอยู่ใน I/O SoC (USB, HDMI, DP, MIPI ฯลฯ) อาจตัดสินใจส่งมอบชิปเล็ต I/O แทน

หมวดหมู่ IP อื่นๆ ที่ได้รับผลกระทบจากการปฏิวัติครั้งนี้คือผู้จำหน่าย IP คอมไพเลอร์หน่วยความจำ SRAM สำหรับแคช L3 โดยธรรมชาติแล้ว ขนาดแคชคาดว่าจะแตกต่างกันไปขึ้นอยู่กับโปรเซสเซอร์ อย่างไรก็ตาม การออกแบบชิปเล็ตแคช L3 อาจเป็นหนทางสำหรับผู้จำหน่าย IP ในการเพิ่มรายได้จากการออกแบบ IP โดยการนำเสนอผลิตภัณฑ์ประเภทใหม่

เช่นกัน หมวดหมู่ NVM IP อาจได้รับผลกระทบเชิงบวก เนื่องจาก NVM IP ไม่ได้รวมอยู่ใน SoC ที่ออกแบบบนโหนดกระบวนการขั้นสูงอีกต่อไป มันจะเป็นวิธีสำหรับผู้จำหน่าย NVM IP ในการสร้างธุรกิจใหม่โดยการนำเสนอชิปเล็ต

เราคิดว่าชิปเล็ตเร่ง FPGA และ AI จะเป็นแหล่งรายได้ใหม่สำหรับผู้ผลิตชิป ASSP แต่เราไม่คิดว่าพวกเขาสามารถได้รับการจัดอันดับให้เป็นผู้จำหน่าย IP อย่างเคร่งครัด

หากผู้จำหน่าย Interface IP จะเป็นผู้มีบทบาทสำคัญในการปฏิวัติซิลิคอนนี้ โรงหล่อซิลิคอนที่จัดการกับโหนดที่ทันสมัยที่สุด เช่น TSMC และ Samsung ก็จะมีบทบาทสำคัญเช่นกัน เราไม่คิดว่าโรงหล่อจะออกแบบชิปเล็ต แต่พวกเขาสามารถตัดสินใจสนับสนุนผู้จำหน่าย IP และผลักดันให้พวกเขาออกแบบชิปเล็ตเพื่อใช้กับ SoC ในรูปแบบ 3 นาโนเมตร เช่นเดียวกับที่พวกเขาทำในปัจจุบันเมื่อสนับสนุนผู้จำหน่าย IP ขั้นสูงเพื่อทำการตลาด SerDes ระดับไฮเอนด์ของพวกเขา ฮาร์ด IP ใน 7 นาโนเมตรและ 5 นาโนเมตร

การเปลี่ยนแปลงล่าสุดของ Intel เป็น 3rd โรงหล่อของบริษัทต่างๆ คาดว่าจะใช้ประโยชน์จาก IP ของบริษัทอื่น เช่นเดียวกับการใช้ชิปเล็ตที่ต่างกันโดยกลุ่มเซมิคอนดักเตอร์รุ่นใหญ่ ในกรณีนี้ ไม่ต้องสงสัยเลยว่า Hyperscalars เช่น Microsoft, Amazon และ Google จะนำสถาปัตยกรรมชิปเล็ตมาใช้เช่นกัน… หากพวกเขาไม่ได้นำหน้า Intel ในการใช้ชิปเล็ต

By เอริค เอสตีฟ (ปริญญาเอก) นักวิเคราะห์ เจ้าของ IPnest

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- คันเร่ง

- เร่ง

- การนำมาใช้

- เทคโนโลยีขั้นสูง

- AI

- การอนุญาต

- อเมซอน

- เอเอ็มดี

- นักวิเคราะห์

- การใช้งาน

- สถาปัตยกรรม

- ARM

- ปัญญาประดิษฐ์

- ปัญญาประดิษฐ์ (AI)

- ASIC

- ที่ดีที่สุด

- สร้าง

- การก่อสร้าง

- พวง

- รถบัส

- ธุรกิจ

- รูปแบบธุรกิจ

- ซื้อ

- โทรศัพท์

- ความจุ

- เปลี่ยนแปลง

- ชิป

- ชิป

- มา

- บริษัท

- คำนวณ

- การคำนวณ

- เอกฉันท์

- ค่าใช้จ่าย

- ลูกค้า

- ข้อมูล

- การส่งมอบ

- ออกแบบ

- พัฒนา

- อุปกรณ์

- ดิจิตอล

- ก่อน

- ในช่วงเริ่มต้น

- ระบบนิเวศ

- ฯลฯ

- วิวัฒนาการ

- ชื่อจริง

- โฟกัส

- FPGA

- ฟรี

- ฟังก์ชัน

- GPUs

- บัญชีกลุ่ม

- การเจริญเติบโต

- การเจริญเติบโต

- จุดสูง

- ประวัติ

- บ้าน

- HTTPS

- เป็นลูกผสม

- ส่งผลกระทบ

- เพิ่ม

- อุตสาหกรรม

- Initiative

- บูรณาการ

- อินเทล

- Intelligence

- การลงทุน

- IP

- IT

- การเก็บรักษา

- คีย์

- เปิดตัว

- กฏหมาย

- ชั้นนำ

- การเรียนรู้

- นำ

- เลฟเวอเรจ

- LINK

- เรียนรู้เครื่อง

- สำคัญ

- เครื่องชง

- การทำ

- การผลิต

- ตลาด

- ไมโครซอฟท์

- ML

- แบบ

- เครือข่าย

- ผลิตภัณฑ์ใหม่

- โหนด

- เสนอ

- การเสนอ

- เปิด

- ตัวเลือกเสริม (Option)

- อื่นๆ

- เจ้าของ

- บรรจุภัณฑ์

- กระดาษ

- การปฏิบัติ

- ผลิตภัณฑ์

- การผลิต

- ผลิตภัณฑ์

- ป้องกัน

- การป้องกัน

- ราคา

- การออกแบบ

- REST

- ความเสี่ยง

- วิ่ง

- ซัมซุง

- สารกึ่งตัวนำ

- การส่งสินค้า

- จำลอง

- ขนาด

- มาตรฐาน

- กลยุทธ์

- สนับสนุน

- สวิตซ์

- ระบบ

- เป้า

- เทคนิค

- เทคโนโลยี

- ทดสอบ

- ด้านบน

- us

- USB

- ผู้ขาย

- การตรวจสอบ

- กระดาษสีขาว

- คำ

- งาน

- ปี

- ผล