Fuzzing คือการตรวจสอบซอฟต์แวร์ การสุ่มคือการตรวจสอบฮาร์ดแวร์ วิธีการคลุมเครือสามารถปรับปรุงการทดสอบความปลอดภัยของฮาร์ดแวร์ได้หรือไม่ Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, ผู้ประกอบการ, อดีต Synopsys CTO) และฉันดำเนินซีรีส์เกี่ยวกับแนวคิดการวิจัยต่อไป เช่นเคยยินดีรับข้อเสนอแนะ

นวัตกรรม

เลือกเดือนนี้ HyperFuzzing สำหรับการตรวจสอบความปลอดภัยของ SoC. ผู้เขียนนำเสนอบทความนี้ที่ ICCAD 2020 โดยมาจาก IIT Kanpur

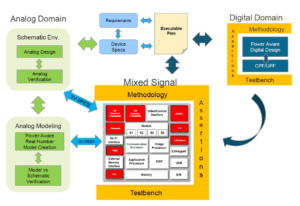

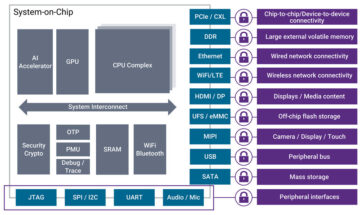

นี่เป็นวิธีการที่น่าสนใจในการคลุมเครือ ซึ่งปรับให้เข้ากับการออกแบบ SoC สมัยใหม่โดยเฉพาะ มันต่อยอด ทรัพย์สินมากเกินไป การตรวจสอบในการจำลองแบบไดนามิก คุณสมบัติไฮเปอร์เหล่านี้มีเหตุผลเกี่ยวกับพฤติกรรมมากกว่า ชุดของร่องรอยซึ่งเป็นแนวทางที่เหมาะสมกับการตรวจสอบความปลอดภัยอย่างยิ่ง ผู้เขียนเสนอตัวอย่างการตรวจสอบการไหลของข้อมูล (ข้อมูลที่มีสิทธิพิเศษไม่สามารถรั่วไหลจาก A ถึง B พูดได้) และการตรวจสอบการไม่รบกวน (การกระทำของฝ่ายตรงข้ามจะต้องไม่รบกวนการไหลของการคำนวณ) จากนั้นจะมีการตรวจสอบความปลอดภัยโดยการเปรียบเทียบกลุ่มร่องรอยการจำลองที่มีและไม่มีการแก้ไขดัดแปลง

การแทรกแซงในแนวทางนี้สามารถจำลองช่องโหว่ประเภทต่างๆ ไปยังแหล่งที่มาที่ไม่น่าเชื่อถือได้ โดยการสุ่มคำสั่งเฟิร์มแวร์ เขียนคำสั่งจากส่วนประกอบไปยัง NoC หรือบิตพลิกในหน่วยความจำ ผู้เขียนยังเสนอตัวชี้วัดความครอบคลุมใหม่ๆ หลายประการ สิ่งเหล่านี้ได้รับการออกแบบมาเพื่อเป็นแนวทางในการวนซ้ำเพื่อแก้ไขกรณีต่างๆ ที่ได้รับอิทธิพลมากที่สุดจากการดำเนินการแก้ไขครั้งก่อนๆ

กรณีทดสอบของพวกเขามีขนาดเล็กแต่เป็นตัวแทน SoC (รายละเอียดใน GitHub) ดำเนินการทดสอบเฟิร์มแวร์กับบล็อกการเข้ารหัส ตรวจสอบการไม่รบกวนและช่องโหว่อื่นๆ พวกเขายังเรียกใช้การบูตอย่างปลอดภัยด้วยการตรวจสอบบล็อกข้อมูล พวกเขาพบการละเมิดความปลอดภัยหลายครั้งในบล็อก crypto ยกเว้นในกรณีที่บล็อกมีการป้องกัน ECC

มุมมองของพอล

การตรวจสอบความปลอดภัยเป็นหัวข้อที่สำคัญ และมีงานมากมายที่ดำเนินอยู่ทั้งในด้านวิชาการและในอุตสาหกรรม เอกสารนี้รวบรวมการครอบคลุมตามการกลายพันธุ์แบบสุ่มเข้ากับ "คุณสมบัติขั้นสูง" เหนือชุดการติดตามการจำลองเพื่อสร้างโซลูชันที่เป็นนวัตกรรมใหม่ที่ทั้งปรับขนาดได้และมีประสิทธิภาพในการแสดงให้เห็นถึงข้อบกพร่องด้านความปลอดภัย

คุณสมบัติความปลอดภัยบางอย่างสามารถกำหนดได้อย่างเป็นทางการบนชุดการติดตามการจำลองเท่านั้น ตัวอย่างเช่น “การไม่รบกวน” หมายความว่าผู้โจมตีไม่สามารถรบกวนการคำนวณที่ได้รับการป้องกันในการออกแบบได้ ในการสาธิตการรบกวน คุณต้องเปรียบเทียบสองร่องรอย ซึ่งเหมือนกันในการกระตุ้นอินพุต ยกเว้นการมีอยู่ของการกระทำของผู้โจมตีในร่องรอยเดียว หากการคำนวณที่ได้รับการป้องกันในการติดตามที่ถูกโจมตีแตกต่างจากการคำนวณในการติดตามสีทอง แสดงว่ามีการรบกวน

ผู้เขียนสร้างภาษาพิเศษของตนเองเพื่อยืนยันร่องรอยต่างๆ และใช้มันเพื่อกำหนดคุณสมบัติด้านความปลอดภัยสำหรับการไม่รบกวนและการรักษาความลับ พวกเขาสร้างโฟลว์แบบกำหนดเองเพื่อสุ่มแก้ไขการจำลอง และตรวจสอบคุณสมบัติด้านความปลอดภัยระหว่างการจำลองแบบดัดแปลงและแบบไม่ดัดแปลง อัลกอริธึมการปลอมแปลงแบบสุ่มของพวกเขายังมีการเรียนรู้แบบฮิวริสติกแบบครอบคลุมที่สวยงามเพื่อเป็นแนวทางในการค้นหาข้อบกพร่องด้านความปลอดภัยได้อย่างมีประสิทธิภาพมากขึ้น

แนวคิดในการยืนยันเหนือการจำลองหลายครั้งนั้นทรงพลังมาก ฉันสงสัยว่าจะเป็นไปได้หรือไม่ที่จะขยาย SystemVerilog เพื่อรองรับการยืนยันประเภทนี้ สิ่งนี้สามารถเปิดประตูสู่ส่วนขยายดั้งเดิมที่น่าสนใจสำหรับการจำลองเชิงพาณิชย์และเครื่องมือที่เป็นทางการ ความเป็นไปได้อีกอย่างหนึ่งอาจเป็นการขยาย Portable Stimulus Standard (PSS) ใหม่ให้รวมการยืนยันที่ครอบคลุมการทดสอบที่สร้างขึ้นหลายรายการ

บทความนี้อ่านง่ายและสนุกสนาน แม้ว่าฉันต้องการรายละเอียดเพิ่มเติมเกี่ยวกับผลลัพธ์ก็ตาม ผู้เขียนอ้างว่าโซลูชันของพวกเขาพบช่องโหว่ด้านความปลอดภัยในกรณีทดสอบ SoC แบบโอเพ่นซอร์ส แต่ไม่มีรายละเอียดว่าช่องโหว่เหล่านี้คืออะไร หรือวิธีการของพวกเขาเปรียบเทียบกับวิธีอื่นๆ ในงานวิจัยที่สามารถนำไปใช้กับการค้นหาช่องโหว่เดียวกันได้

มุมมองของราอูล

ฉันจะดูสิ่งนี้ก่อนจากมุมวุฒิภาวะทางเทคโนโลยี ฉันชอบแนวคิดนี้โดยทั่วไป ซึ่งเป็นแนวทางที่น่าสนใจมากในการจัดระดับความปลอดภัยในการออกแบบ อย่างไรก็ตาม การออกแบบแต่ละแบบกำหนดให้นักออกแบบต้องทำการทดสอบเมล็ดพันธุ์ การงัดแงะ และข้อกำหนดด้านความปลอดภัยด้วยภาษาที่ใช้ในการยืนยันแบบใหม่ สำหรับฉัน สิ่งนี้ผูกมัดแนวทางอย่างมั่นคงกับโดเมนทางวิชาการในตอนนี้ เหมาะสำหรับวิทยานิพนธ์และเอกสารต่างๆ ที่ยังไม่ใกล้เคียงกับสิ่งที่สามารถก้าวไปสู่การใช้งานเชิงพาณิชย์ได้

ฉันจะสวมหมวกนักลงทุนสำหรับการท้าทายครั้งที่สอง ความปลอดภัยเป็นหัวข้อสำคัญ ไม่ต้องสงสัยเลย แต่นอกเหนือจากขอบเขตบางส่วนที่เราทราบอยู่แล้ว เช่น การบินและอวกาศ การป้องกัน ระบบการชำระเงิน และผู้ประมวลผล/เซิร์ฟเวอร์ เป็นต้น ยังคงไม่ใช่ปัญหาที่มีอยู่สำหรับ OEM และผู้ผลิตส่วนประกอบส่วนใหญ่ พวกเขายินดีที่จะทำเครื่องหมายในช่องหากคาดหวังโดยทั่วไป แต่เฉพาะในกรณีที่ผลกระทบต่อต้นทุนหรือเวลาในการทำตลาดมีน้อย เพราะโดยทั่วไปแล้วลูกค้าของพวกเขาจะไม่จ่ายเงินเพื่อความปลอดภัยมากขึ้น ซึ่งทำให้การรักษาความปลอดภัยสำหรับตลาดส่วนใหญ่ยังคงขึ้นอยู่กับ IP แบบครบวงจร เช่น รากฐานของฮาร์ดแวร์ที่น่าเชื่อถือ และแอปที่ใช้งานง่าย โซลูชั่นที่บรรจุด้วยวิธีใดวิธีหนึ่งเหล่านี้จะสามารถลงทุนได้ ไม่เช่นนั้นก็ไม่มากนัก

มุมมองของฉัน

พอลและราอุลพูดถึงสิ่งที่ฉันอาจแนะนำเป็นส่วนใหญ่ ฉันชอบแนวคิดของ Paul ในการขยาย SVA อย่างน้อยก็เพื่อสนับสนุนการทดลองกับคุณสมบัติที่มากเกินไป สิ่งนี้จะต้องเปิดคลาสใหม่ของการทดสอบที่น่าสนใจ ซึ่งในที่สุดจะนำไปสู่วิธีการตรวจสอบแบบรวมกลุ่มแบบใหม่

แชร์โพสต์นี้ผ่าน: ที่มา: https://semiwiki.com/eda/299391-fuzzing-to-validate-soc-security-innovation-in-verification/

- 100

- 2020

- 2021

- การบินและอวกาศ

- ขั้นตอนวิธี

- การใช้งาน

- ปพลิเคชัน

- รอบ

- ผู้เขียน

- บิต

- กล่อง

- สร้าง

- จังหวะ

- กรณี

- ท้าทาย

- การตรวจสอบ

- การตรวจสอบ

- เชิงพาณิชย์

- ส่วนประกอบ

- ต่อ

- การเข้ารหัสลับ

- CTO

- ลูกค้า

- ข้อมูล

- ป้องกัน

- ออกแบบ

- โดเมน

- มีประสิทธิภาพ

- ผู้ประกอบการ

- ส่วนขยาย

- พบ

- ชื่อจริง

- ข้อบกพร่อง

- ไหล

- General

- GM

- ยิ่งใหญ่

- ให้คำแนะนำ

- ฮาร์ดแวร์

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- ความคิด

- อีอีอี

- ภาพ

- ส่งผลกระทบ

- อุตสาหกรรม

- ข้อมูล

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- นักลงทุน

- IP

- IT

- กระโดด

- ภาษา

- ชั้นนำ

- รั่วไหล

- การเรียนรู้

- วรรณคดี

- ตลาด

- ตลาด

- ตัวชี้วัด

- แบบ

- เสนอ

- เปิด

- อื่นๆ

- กระดาษ

- ชำระ

- การชำระเงิน

- ระบบการชำระเงิน

- เสนอ

- การป้องกัน

- สุ่ม

- การวิจัย

- ผลสอบ

- วิ่ง

- วิ่ง

- ความปลอดภัย

- การทดสอบความปลอดภัย

- เมล็ดพันธุ์

- ชุด

- ชุด

- จำลอง

- เล็ก

- So

- ซอฟต์แวร์

- โซลูชัน

- แรงบันดาลใจ

- สนับสนุน

- ระบบ

- เทคโนโลยี

- การทดสอบ

- การทดสอบ

- เวลา

- วางใจ

- การตรวจสอบ

- ช่องโหว่

- งาน