Chiplets (die stacking) ไม่ใช่เรื่องใหม่ ต้นกำเนิดหยั่งรากลึกในอุตสาหกรรมเซมิคอนดักเตอร์ และเป็นตัวแทนของแนวทางโมดูลาร์ในการออกแบบและผลิตวงจรรวม แนวคิดของชิปเล็ตได้รับการเสริมกำลังเพื่อตอบสนองต่อความท้าทายล่าสุดที่เกิดจากความซับซ้อนที่เพิ่มขึ้นของการออกแบบเซมิคอนดักเตอร์ ต่อไปนี้เป็นประเด็นที่บันทึกไว้อย่างดีเกี่ยวกับความต้องการชิปเล็ต:

ความซับซ้อนของวงจรรวม (ICs): เมื่อเทคโนโลยีเซมิคอนดักเตอร์ก้าวหน้าไป ความซับซ้อนในการออกแบบและการผลิตไอซีเสาหินขนาดใหญ่ก็เพิ่มขึ้น สิ่งนี้นำไปสู่ความท้าทายในแง่ของผลผลิต ต้นทุน ทรัพยากรที่มีทักษะ และเวลาในการออกสู่ตลาด

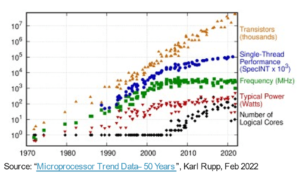

กฎของมัวร์: อุตสาหกรรมเซมิคอนดักเตอร์ปฏิบัติตามกฎของมัวร์ ซึ่งระบุว่าจำนวนทรานซิสเตอร์บนไมโครชิปเพิ่มขึ้นสองเท่าทุกๆ สองปีโดยประมาณ การปรับขนาดความหนาแน่นของทรานซิสเตอร์อย่างไม่หยุดยั้งนี้ก่อให้เกิดความท้าทายสำหรับการออกแบบเสาหินแบบดั้งเดิม

การใช้งานที่หลากหลาย: การใช้งานที่แตกต่างกันต้องใช้ส่วนประกอบและคุณสมบัติพิเศษ แทนที่จะสร้างชิปขนาดใหญ่ที่พยายามตอบสนองทุกความต้องการ ชิปเล็ตช่วยให้สามารถสร้างส่วนประกอบพิเศษที่สามารถนำมารวมกันในลักษณะมิกซ์แอนด์แมตช์ได้

ข้อควรพิจารณาด้านต้นทุนและเวลาในการออกสู่ตลาด: การพัฒนาเทคโนโลยีกระบวนการเซมิคอนดักเตอร์ใหม่เป็นความพยายามที่มีราคาแพงและใช้เวลานาน Chiplets มอบวิธีการใช้ประโยชน์จากกระบวนการที่มีอยู่แล้วสำหรับส่วนประกอบบางอย่าง ในขณะเดียวกันก็มุ่งเน้นไปที่นวัตกรรมสำหรับฟังก์ชันเฉพาะ ชิปเล็ตยังช่วยในการเพิ่มเทคโนโลยีกระบวนการใหม่ๆ อีกด้วย เนื่องจากขนาดแม่พิมพ์และความซับซ้อนเป็นเพียงเศษเสี้ยวของชิปขนาดใหญ่ จึงทำให้การผลิตและผลผลิตง่ายขึ้น

ความท้าทายในการเชื่อมต่อระหว่างกัน: การออกแบบเสาหินแบบดั้งเดิมเผชิญกับความท้าทายในแง่ของการเชื่อมต่อระหว่างกันเนื่องจากระยะห่างระหว่างส่วนประกอบต่างๆ เพิ่มขึ้น Chiplets ช่วยให้สามารถปรับปรุงความเป็นโมดูลาร์และเชื่อมต่อระหว่างกันได้ง่าย

บูรณาการที่แตกต่างกัน: Chiplets ช่วยให้สามารถบูรณาการเทคโนโลยี วัสดุ และฟังก์ชันการทำงานต่างๆ ไว้ในแพ็คเกจเดียว แนวทางนี้เรียกว่าการบูรณาการแบบต่างกัน อำนวยความสะดวกในการรวมองค์ประกอบที่หลากหลายเพื่อให้ได้ประสิทธิภาพโดยรวมที่ดีขึ้น

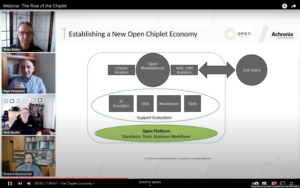

ความร่วมมือในอุตสาหกรรม: การพัฒนาชิปเล็ตมักเกี่ยวข้องกับความร่วมมือระหว่างบริษัทเซมิคอนดักเตอร์ต่างๆ และผู้เล่นในอุตสาหกรรม ความพยายามในการมาตรฐาน เช่น องค์กรที่นำโดยองค์กรต่างๆ เช่น Universal Chiplet Interconnect Express Consortium (UCIe) สำหรับการบูรณาการชิปเล็ต

บรรทัดด้านล่าง: Chiplets กลายเป็นโซลูชันในการจัดการกับความท้าทายที่เกิดจากความซับซ้อน ต้นทุน เวลาออกสู่ตลาด และแรงกดดันด้านพนักงานที่เพิ่มขึ้นในอุตสาหกรรมเซมิคอนดักเตอร์ ลักษณะแบบโมดูลาร์และยืดหยุ่นของการออกแบบที่ใช้ชิปเล็ตช่วยให้สามารถบูรณาการชิปได้อย่างมีประสิทธิภาพและปรับแต่งได้มากขึ้น ซึ่งมีส่วนทำให้เกิดความก้าวหน้าในเทคโนโลยีเซมิคอนดักเตอร์ และยังไม่ต้องพูดถึงความสามารถในการแม่พิมพ์แบบหลายแหล่ง

อินเทล

Intel ใช้ประโยชน์จากชิปเล็ตซึ่งเป็นกุญแจสำคัญของกลยุทธ์ IDM 2.0

มีสองประเด็นสำคัญ:

Intel จะใช้ชิปเล็ตเพื่อส่งมอบโหนดกระบวนการ 5 โหนดใน 4 ปี ซึ่งถือเป็นหลักชัยสำคัญในกลยุทธ์ IEDM 2.0 (Intel 7, 4, 3, 20A, 18A)

Intel พัฒนากระบวนการ Intel 4 สำหรับผลิตภัณฑ์ภายในโดยใช้ชิปเล็ต Intel พัฒนาชิป CPU ขึ้นมาซึ่งทำได้ง่ายกว่าชิป CPU ขนาดใหญ่ในอดีตมาก ชิปเล็ตสามารถใช้เพื่อเร่งกระบวนการได้เร็วขึ้นมาก และ Intel ก็สามารถอ้างความสำเร็จได้โดยไม่ต้องดำเนินการทั้งหมดสำหรับ CPU หรือ GPU ที่ซับซ้อน จากนั้น Intel จะสามารถเปิดตัวโหนดกระบวนการใหม่ (Intel 3) สำหรับลูกค้าโรงหล่อซึ่งสามารถออกแบบชิปแบบเสาหินหรือแบบชิปเล็ตได้ Intel ยังทำสิ่งนี้กับ 20A และ 18A อีกด้วย ซึ่งถือเป็นหลักชัยของ 5 process nodes ใน 4 ปี แน่นอนว่าความสำเร็จนี้เป็นที่ถกเถียงกัน แต่ฉันไม่เห็นเหตุผล

Intel จะใช้ชิปเล็ตเพื่อจ้างบุคคลภายนอกด้านการผลิต (TSMC) เมื่อธุรกิจกำหนด

Intel ลงนามข้อตกลงเอาท์ซอร์สในอดีตกับ TSMC สำหรับชิปเล็ต นี่เป็นข้อพิสูจน์ที่ชัดเจนของแนวคิดที่จะพาเรากลับไปสู่รูปแบบธุรกิจการหล่อแบบหลายแหล่งที่เราชอบจนถึงยุค FinFET ฉันไม่รู้ว่า Intel จะยังคงใช้ TSMC ต่อไปนอกเหนือจากโหนด N3 หรือไม่ แต่ได้สรุปประเด็นแล้ว เราไม่ผูกพันกับแหล่งผลิตชิปแห่งเดียวอีกต่อไป

Intel สามารถใช้การพิสูจน์แนวคิดนี้ (โดยใช้ชิปเล็ตจากโรงหล่อหลายแห่งและบรรจุหีบห่อ) สำหรับโอกาสทางธุรกิจของโรงหล่อที่ลูกค้าต้องการอิสระจากโรงหล่อหลายแห่ง Intel เป็นบริษัทแรกที่ทำเช่นนี้

TSMC

มีสองประเด็นสำคัญ:

ด้วยชิปเล็ต TSMC หลีกเลี่ยงคำว่า M (การผูกขาด)

ลูกค้าที่ใช้ชิปเล็ตสามารถหาแหล่งที่มาของแม่พิมพ์ได้จากหลายแหล่งในทางทฤษฎี ล่าสุดฉันได้ยินมาว่า TSMC จะไม่บรรจุหีบห่อจากโรงหล่ออื่นๆ แต่ถ้าวาฬอย่าง Nvidia ถามพวกเขา ฉันแน่ใจว่าพวกเขาจะทำ

Chiplets จะท้าทาย TSMC และ TSMC พร้อมสำหรับความท้าทายเสมอ เพราะความท้าทายมาพร้อมกับนวัตกรรม

TSMC ตอบสนองต่อชิปเล็ตอย่างรวดเร็วด้วย ผ้า 3D กลุ่มผลิตภัณฑ์ 3D Silicon Stacking และเทคโนโลยีบรรจุภัณฑ์ขั้นสูงที่ครอบคลุม ความท้าทายที่ยิ่งใหญ่ที่สุดสำหรับชิปเล็ตในปัจจุบันคือระบบนิเวศที่สนับสนุน และนั่นคือสิ่งที่ TSMC เป็นเรื่องเกี่ยวกับระบบนิเวศ

กลับมาที่คำถามเดิม “Chiplets จะสร้างความยุ่งยากให้กับ Intel และ TSMC ได้อย่างไร” เป็นอย่างมาก. เราอยู่ในจุดเริ่มต้นของการหยุดชะงักของการผลิตเซมิคอนดักเตอร์ที่เราไม่เคยเห็นมาก่อนนับตั้งแต่ FinFET ตอนนี้โรงหล่อ Pure-Play และ IDM ทั้งหมดมีโอกาสที่จะได้รับชิปที่โลกต้องพึ่งพาอย่างแน่นอน

ยังอ่าน:

Big Race ปี 2024 คือ TSMC N2 และ Intel 18A

IEDM: อะไรจะเกิดขึ้นหลังจากซิลิคอน?

IEDM: TSMC ดำเนินการวิจัยเกี่ยวกับกระบวนการ CFET อย่างต่อเนื่อง

IEDM Buzz – Intel แสดงตัวอย่างนวัตกรรมการปรับขนาดทรานซิสเตอร์แนวตั้งใหม่

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/chiplet/340742-how-disruptive-will-chiplets-be-for-intel-and-tsmc/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- 3d

- 7

- a

- ความสามารถ

- เกี่ยวกับเรา

- อย่างแน่นอน

- บรรลุ

- ที่อยู่

- สูง

- ความก้าวหน้า

- หลังจาก

- ข้อตกลง

- ช่วย

- ทั้งหมด

- อนุญาต

- ช่วยให้

- ด้วย

- เสมอ

- an

- และ

- การใช้งาน

- เข้าใกล้

- ประมาณ

- เป็น

- AS

- กลับ

- ตาม

- BE

- เพราะ

- รับ

- การเริ่มต้น

- ดีกว่า

- ระหว่าง

- เกิน

- ใหญ่

- ขอบเขต

- ธุรกิจ

- รูปแบบธุรกิจ

- แต่

- by

- CAN

- พิมพ์ใหญ่

- ให้ความบันเทิง

- บาง

- ท้าทาย

- ความท้าทาย

- ชิป

- ชิป

- ข้อเรียกร้อง

- ชัดเจน

- การทำงานร่วมกัน

- การผสมผสาน

- รวม

- มา

- บริษัท

- บริษัท

- ซับซ้อน

- ความซับซ้อน

- ส่วนประกอบ

- ครอบคลุม

- แนวคิด

- การพิจารณา

- สมาคม

- ต่อ

- การบริจาค

- ราคา

- หลักสูตร

- ซีพียู

- การสร้าง

- การสร้าง

- วิกฤติ

- ลูกค้า

- ปรับแต่งได้

- ลึก

- ส่งมอบ

- ความต้องการ

- ขึ้นอยู่กับ

- ออกแบบ

- การออกแบบ

- การออกแบบ

- พัฒนา

- ที่กำลังพัฒนา

- พัฒนาการ

- บงการ

- ตาย

- ต่าง

- การหยุดชะงัก

- ซึ่งทำให้ยุ่ง

- ระยะทาง

- หลาย

- do

- เอกสาร

- การทำ

- คู่ผสม

- ความสะดวก

- ง่ายดาย

- การทำให้สบาย

- ระบบนิเวศ

- ที่มีประสิทธิภาพ

- ความพยายาม

- โผล่ออกมา

- ทำให้สามารถ

- มานะ

- ยุค

- ทุกๆ

- ที่มีอยู่

- แพง

- ด่วน

- ต้องเผชิญกับ

- อำนวยความสะดวก

- ครอบครัว

- แฟชั่น

- คุณสมบัติ

- ชื่อจริง

- มีความยืดหยุ่น

- โดยมุ่งเน้น

- ดังต่อไปนี้

- สำหรับ

- โรงหล่อ

- เศษ

- เสรีภาพ

- ราคาเริ่มต้นที่

- เต็ม

- ฟังก์ชันการทำงาน

- ได้รับ

- GPUs

- ใหญ่ที่สุด

- มี

- มี

- ได้ยิน

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- ทางประวัติศาสตร์

- อดีต

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTTPS

- i

- ICS

- if

- การปรับปรุง

- in

- เพิ่มขึ้น

- ที่เพิ่มขึ้น

- อุตสาหกรรม

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- แทน

- แบบบูรณาการ

- บูรณาการ

- อินเทล

- ภายใน

- ที่เกี่ยวข้องกับการ

- jpg

- คีย์

- ทราบ

- ที่รู้จักกัน

- ใหญ่

- ชื่อสกุล

- กฏหมาย

- นำ

- เลฟเวอเรจ

- กดไลก์

- Line

- อีกต่อไป

- ทำ

- สำคัญ

- การผลิต

- วัสดุ

- เป็นผู้ใหญ่

- ความกว้างสูงสุด

- กล่าวถึง

- ขั้น

- แบบ

- โมดูลาร์

- เป็นเสาหิน

- ข้อมูลเพิ่มเติม

- มีประสิทธิภาพมากขึ้น

- มาก

- หลาย

- หลาย

- ธรรมชาติ

- ความต้องการ

- ใหม่

- ไม่

- ปม

- โหนด

- ตอนนี้

- จำนวน

- Nvidia

- of

- มักจะ

- on

- ต่อเนื่อง

- โอกาส

- โอกาส

- or

- ใบสั่ง

- องค์กร

- เป็นต้นฉบับ

- ต้นกำเนิด

- อื่นๆ

- ภายนอก

- เอาท์ซอร์ส

- ทั้งหมด

- แพ็คเกจ

- บรรจุภัณฑ์

- การปฏิบัติ

- ชิ้น

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- ผู้เล่น

- จุด

- จุด

- ถูกวาง

- โพสท่า

- โพสต์

- ตัวอย่าง

- กระบวนการ

- กระบวนการ

- ผลิตภัณฑ์

- โปรโมเตอร์

- พิสูจน์

- พิสูจน์แนวคิด

- ให้

- คำถาม

- ได้เร็วขึ้น

- อย่างรวดเร็ว

- เชื่อชาติ

- ทางลาด

- กระโจน

- อ่าน

- จริงๆ

- เหตุผล

- เมื่อเร็ว ๆ นี้

- ปล่อย

- กระด้าง

- แสดง

- ต้องการ

- การวิจัย

- แหล่งข้อมูล

- คำตอบ

- ซึ่งได้หยั่งราก

- ปรับ

- เห็น

- เห็น

- สารกึ่งตัวนำ

- ลงนาม

- ซิลิคอน

- ตั้งแต่

- เดียว

- ขนาด

- มีฝีมือ

- So

- ทางออก

- บาง

- แหล่ง

- การจัดหา

- เฉพาะ

- โดยเฉพาะ

- การสุม

- พนักงาน

- มาตรฐาน

- กลยุทธ์

- ความสำเร็จ

- อย่างเช่น

- ชี้ให้เห็นถึง

- ที่สนับสนุน

- แน่ใจ

- เทคโนโลยี

- เทคโนโลยี

- เงื่อนไขการใช้บริการ

- กว่า

- ที่

- พื้นที่

- โลก

- ของพวกเขา

- พวกเขา

- แล้วก็

- พวกเขา

- นี้

- เหล่านั้น

- ดังนั้น

- ต้องใช้เวลามาก

- ไปยัง

- ในวันนี้

- แบบดั้งเดิม

- ทีเอสเอ็มซี

- สอง

- สากล

- จนกระทั่ง

- us

- ใช้

- มือสอง

- การใช้

- แนวตั้ง

- มาก

- ผ่านทาง

- ต้องการ

- ทาง..

- we

- ดี

- วาฬ

- อะไร

- เมื่อ

- ที่

- ในขณะที่

- จะ

- กับ

- ไม่มี

- คำ

- โลก

- จะ

- ปี

- ผล

- ลมทะเล