เทคโนโลยีอัลกอริธึมที่ใช้ซอฟต์แวร์ล่าสุดสองเทคโนโลยี ได้แก่ การขับขี่อัตโนมัติ (ADAS/AD) และ AI แบบกำเนิด (GenAI) กำลังทำให้ชุมชนวิศวกรรมเซมิคอนดักเตอร์ตื่นตัวในเวลากลางคืน

ในขณะที่ ADAS ที่ระดับ 2 และระดับ 3 กำลังดำเนินไป AD ที่ระดับ 4 และ 5 นั้นยังห่างไกลจากความเป็นจริง ส่งผลให้ความกระตือรือร้นในการร่วมลงทุนและเงินทองลดลง วันนี้ GenAI ได้รับความสนใจ และ VC ต่างกระตือรือร้นที่จะลงทุนหลายพันล้านดอลลาร์

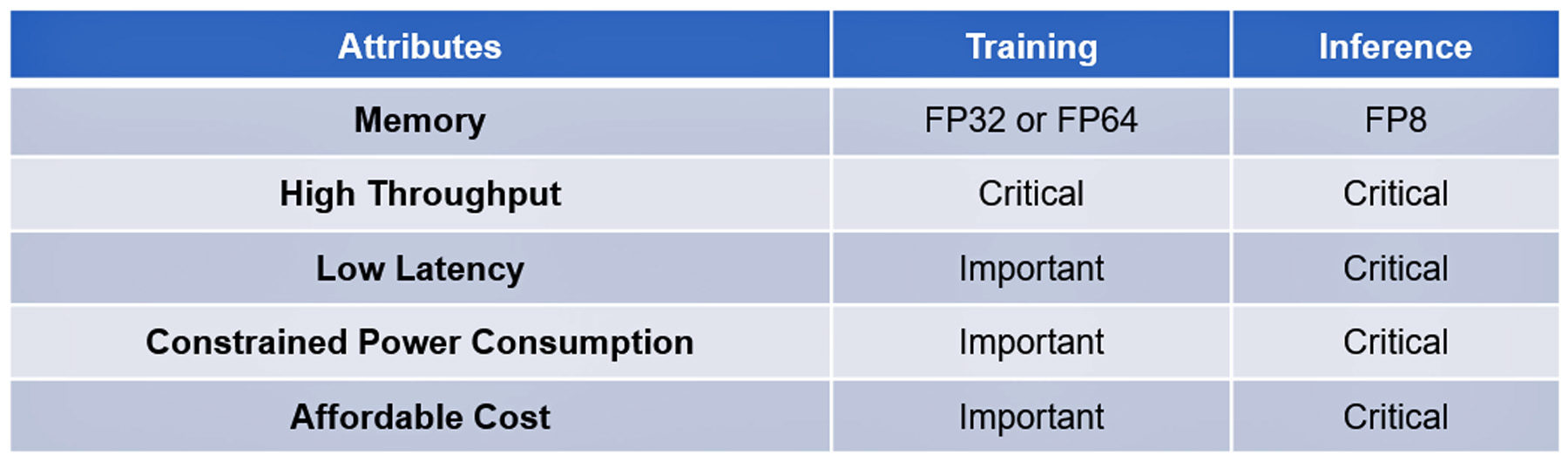

เทคโนโลยีทั้งสองนั้นใช้อัลกอริธึมที่ทันสมัยและซับซ้อน การประมวลผลการฝึกอบรมและการอนุมานมีคุณลักษณะบางประการร่วมกัน บางอย่างสำคัญ บางอย่างสำคัญแต่ไม่จำเป็น: ดูตาราง I

ความก้าวหน้าของซอฟต์แวร์ที่โดดเด่นในเทคโนโลยีเหล่านี้จนถึงขณะนี้ยังไม่ได้รับการจำลองแบบด้วยความก้าวหน้าในฮาร์ดแวร์อัลกอริธึมเพื่อเร่งการดำเนินการ ตัวอย่างเช่น ตัวประมวลผลอัลกอริธึมที่ล้ำสมัยไม่มีประสิทธิภาพในการตอบข้อความค้นหา ChatGPT-4 ภายในหนึ่งหรือสองวินาทีโดยมีค่าใช้จ่าย ¢2 ต่อข้อความค้นหา ซึ่งเป็นเกณฑ์มาตรฐานที่กำหนดโดยการค้นหาของ Google หรือในการประมวลผลข้อมูลขนาดใหญ่ รวบรวมโดยเซ็นเซอร์ AD ในเวลาน้อยกว่า 20 มิลลิวินาที

จนกระทั่งสตาร์ทอัพชาวฝรั่งเศส VSORA ทุ่มพลังสมองเพื่อแก้ไขคอขวดของหน่วยความจำที่เรียกว่ากำแพงหน่วยความจำ

กำแพงแห่งความทรงจำ

ผนังหน่วยความจำของ CPU ได้รับการอธิบายครั้งแรกโดย Wulf และ McKee ในปี 1994 นับตั้งแต่นั้นมา การเข้าถึงหน่วยความจำได้กลายเป็นปัญหาคอขวดของประสิทธิภาพการประมวลผล ความก้าวหน้าในประสิทธิภาพของโปรเซสเซอร์ไม่ได้สะท้อนให้เห็นในความคืบหน้าในการเข้าถึงหน่วยความจำ ทำให้โปรเซสเซอร์ต้องรออีกต่อไปสำหรับข้อมูลที่ส่งผ่านหน่วยความจำ ในตอนท้าย ประสิทธิภาพของโปรเซสเซอร์ลดลงต่ำกว่าการใช้งาน 100%

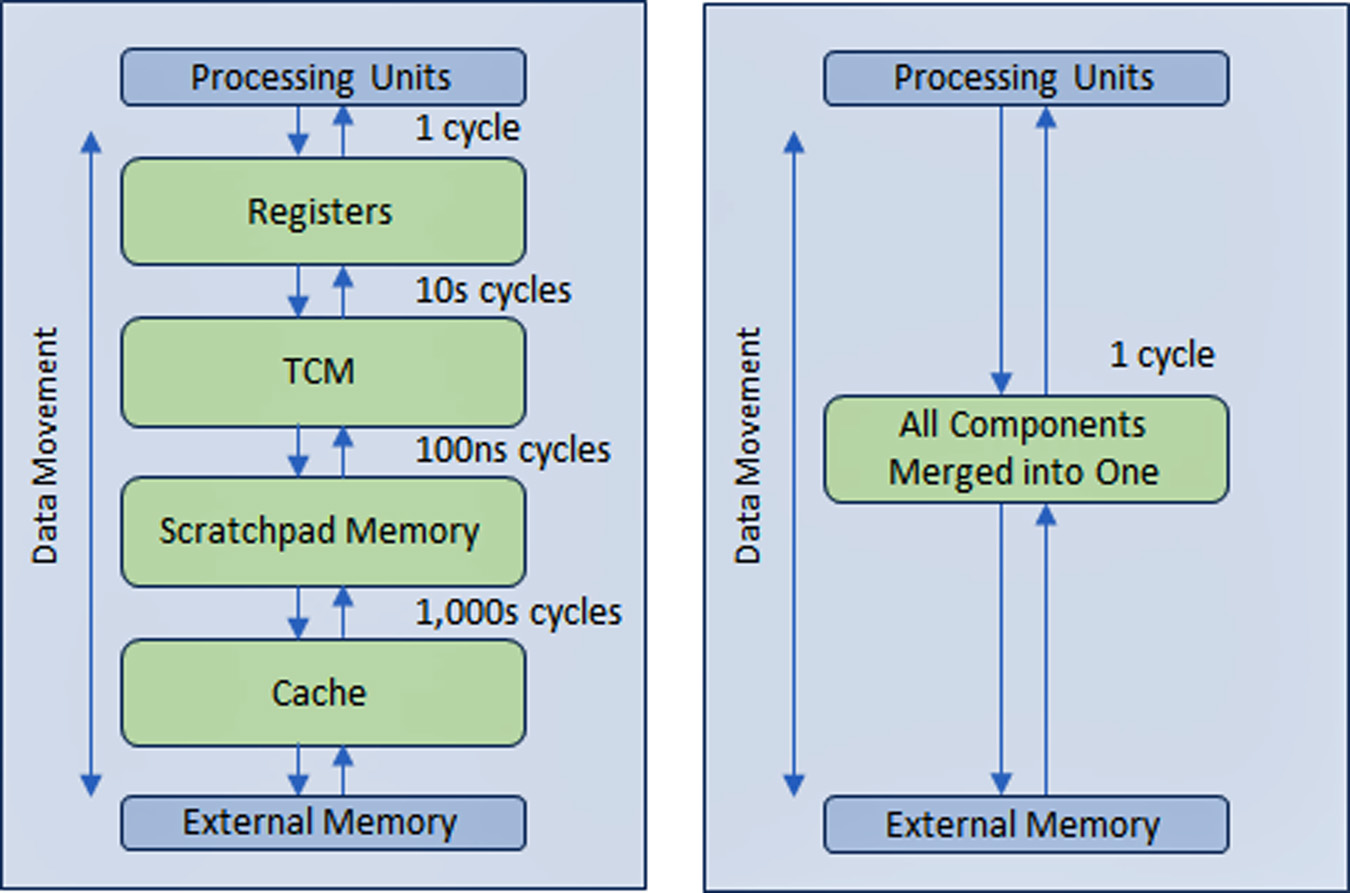

เพื่อแก้ไขปัญหานี้ อุตสาหกรรมเซมิคอนดักเตอร์ได้สร้างโครงสร้างหน่วยความจำแบบลำดับชั้นหลายระดับโดยมีแคชหลายระดับใกล้กับโปรเซสเซอร์ ซึ่งจะช่วยลดปริมาณการรับส่งข้อมูลด้วยหน่วยความจำหลักและหน่วยความจำภายนอกที่ช้าลง

ประสิทธิภาพของโปรเซสเซอร์ AD และ GenAI ขึ้นอยู่กับแบนด์วิธหน่วยความจำที่กว้างมากกว่าอุปกรณ์คอมพิวเตอร์ประเภทอื่นๆ

VSORA ก่อตั้งขึ้นในปี 2015 เพื่อกำหนดเป้าหมายแอปพลิเคชัน 5G ได้คิดค้นสถาปัตยกรรมที่ได้รับการจดสิทธิบัตรซึ่งจะยุบโครงสร้างหน่วยความจำแบบลำดับชั้นให้เป็นแบนด์วิดท์สูงขนาดใหญ่ที่มีหน่วยความจำควบคู่แน่น (TCM) ที่เข้าถึงได้ในรอบสัญญาณนาฬิกาเดียว

จากมุมมองของแกนประมวลผล TCM จะมีลักษณะและทำหน้าที่เหมือนทะเลแห่งการลงทะเบียนในจำนวน MBytes เทียบกับ kBytes ของการลงทะเบียนทางกายภาพจริง ความสามารถในการเข้าถึงเซลล์หน่วยความจำใดๆ ใน TMC ในรอบเดียวทำให้มีความเร็วในการดำเนินการสูง เวลาแฝงต่ำ และใช้พลังงานต่ำ นอกจากนี้ยังใช้พื้นที่ซิลิกอนน้อยกว่า การโหลดข้อมูลใหม่จากหน่วยความจำภายนอกลงใน TCM ในขณะที่ข้อมูลปัจจุบันถูกประมวลผลจะไม่ส่งผลต่อปริมาณงานของระบบ โดยพื้นฐานแล้ว สถาปัตยกรรมช่วยให้สามารถใช้งานหน่วยประมวลผลได้ 80+% ผ่านการออกแบบ ยังคงมีความเป็นไปได้ที่จะเพิ่มแคชและหน่วยความจำ scratchpad หากผู้ออกแบบระบบต้องการ ดูรูปที่ 1

ด้วยโครงสร้างหน่วยความจำแบบรีจิสเตอร์ที่ใช้ในหน่วยความจำเกือบทั้งหมดในทุกแอปพลิเคชัน ข้อดีของการใช้หน่วยความจำ VSORA จึงไม่สามารถกล่าวเกินจริงได้ โดยทั่วไปแล้ว โปรเซสเซอร์ GenAI ที่ล้ำสมัยจะให้ประสิทธิภาพเปอร์เซ็นต์เป็นตัวเลขหลักเดียว ตัวอย่างเช่น โปรเซสเซอร์ GenAI ที่มีทรูพุตปกติหนึ่ง Petaflops ของประสิทธิภาพปกติแต่ประสิทธิภาพน้อยกว่า 5% มอบประสิทธิภาพการใช้งานที่น้อยกว่า 50 เทราฟลอป แต่สถาปัตยกรรม VSORA กลับมีประสิทธิภาพมากกว่าถึง 10 เท่า

ตัวเร่งอัลกอริทึมของ VSORA

VSORA เปิดตัวตัวเร่งความเร็วอัลกอริทึมสองคลาส ได้แก่ ตระกูล Tyr สำหรับแอปพลิเคชัน AD และตระกูล Jotunn สำหรับการเร่งความเร็ว GenAI ทั้งสองรุ่นให้ทรูพุตที่โดดเด่น มีความล่าช้าน้อยที่สุด และใช้พลังงานต่ำโดยใช้ขนาดซิลิคอนเพียงเล็กน้อย

ด้วยประสิทธิภาพที่กำหนดสูงสุดถึงสาม Petaflops จึงมีประสิทธิภาพในการใช้งานทั่วไปที่ 50-80% โดยไม่คำนึงถึงประเภทของอัลกอริทึม และการใช้พลังงานสูงสุดที่ 30 วัตต์/Petaflops สิ่งเหล่านี้เป็นคุณลักษณะที่โดดเด่น ซึ่งยังไม่มีรายงานโดยตัวเร่งความเร็ว AI คู่แข่งใดๆ

Tyr และ Jotunn สามารถตั้งโปรแกรมได้อย่างสมบูรณ์และผสานรวมความสามารถของ AI และ DSP แม้ว่าจะมีจำนวนที่แตกต่างกัน และรองรับการเลือกเลขคณิตได้ทันทีตั้งแต่ 8 บิตไปจนถึง 64 บิต ไม่ว่าจะเป็นจำนวนเต็มหรือจำนวนจุดลอยตัว ความสามารถในการโปรแกรมได้รองรับจักรวาลของอัลกอริธึม ทำให้อัลกอริธึมไม่เชื่อเรื่องพระเจ้า นอกจากนี้ยังรองรับความกระจัดกระจายประเภทต่างๆ หลายประเภทด้วย

คุณลักษณะของโปรเซสเซอร์ VSORA ขับเคลื่อนพวกเขาให้อยู่แถวหน้าของแนวการประมวลผลอัลกอริธึมที่มีการแข่งขันสูง

ซอฟต์แวร์สนับสนุน VSORA

VSORA ได้ออกแบบแพลตฟอร์มการคอมไพล์/การตรวจสอบที่ไม่ซ้ำใครซึ่งปรับให้เหมาะกับสถาปัตยกรรมฮาร์ดแวร์เพื่อให้แน่ใจว่าอุปกรณ์ SoC ประสิทธิภาพสูงที่ซับซ้อนมีการรองรับซอฟต์แวร์มากมาย

มีจุดมุ่งหมายเพื่อให้ผู้ออกแบบอัลกอริทึมในห้องนักบิน ช่วงของระดับการตรวจสอบ/การตรวจสอบตามลำดับชั้น เช่น ESL, ไฮบริด, RTL และเกท จะส่งข้อเสนอแนะแบบกดปุ่มไปยังวิศวกรอัลกอริทึมเพื่อตอบสนองต่อการออกแบบการสำรวจอวกาศ สิ่งนี้ช่วยให้เขาหรือเธอเลือกประนีประนอมที่ดีที่สุดระหว่างประสิทธิภาพ เวลาแฝง พลังงาน และพื้นที่ โค้ดโปรแกรมที่เขียนด้วยนามธรรมระดับสูงสามารถแมปโดยกำหนดเป้าหมายไปที่แกนประมวลผลที่แตกต่างกันอย่างโปร่งใสให้กับผู้ใช้

การเชื่อมต่อระหว่างคอร์สามารถทำได้ภายในซิลิคอนเดียวกัน ระหว่างชิปบน PCB เดียวกัน หรือผ่านการเชื่อมต่อ IP การซิงโครไนซ์ระหว่างคอร์จะได้รับการจัดการโดยอัตโนมัติ ณ เวลาคอมไพล์ และไม่ต้องใช้ซอฟต์แวร์แบบเรียลไทม์

สิ่งกีดขวางบนถนนสู่การขับขี่อัตโนมัติ L4/L5 และการอนุมาน AI เชิงสร้างสรรค์ที่ Edge

โซลูชันที่ประสบความสำเร็จควรรวมถึงความสามารถในการโปรแกรมในภาคสนามด้วย อัลกอริธึมพัฒนาอย่างรวดเร็ว โดยได้รับแรงผลักดันจากแนวคิดใหม่ๆ ที่ล้าสมัยในชั่วข้ามคืนจากความทันสมัยของเมื่อวาน ความสามารถในการอัพเกรดอัลกอริธึมในภาคสนามถือเป็นข้อได้เปรียบที่สำคัญ

ในขณะที่บริษัทระดับไฮเปอร์สเกลได้รวบรวมฟาร์มคอมพิวเตอร์ขนาดใหญ่ที่มีโปรเซสเซอร์ประสิทธิภาพสูงสุดจำนวนมากเพื่อจัดการกับอัลกอริธึมซอฟต์แวร์ขั้นสูง แนวทางนี้ใช้ได้จริงสำหรับการฝึกอบรมเท่านั้น ไม่ใช่สำหรับการอนุมานที่ Edge

โดยทั่วไปการฝึกอบรมจะขึ้นอยู่กับเลขคณิตทศนิยมแบบ 32 บิตหรือ 64 บิตที่สร้างปริมาณข้อมูลขนาดใหญ่ ไม่กำหนดเวลาแฝงที่เข้มงวดและทนทานต่อการใช้พลังงานสูงและค่าใช้จ่ายจำนวนมาก

โดยทั่วไปการอนุมานที่ Edge จะดำเนินการกับเลขคณิตทศนิยม 8 บิตซึ่งสร้างข้อมูลได้ค่อนข้างน้อย แต่ควบคุมเวลาแฝงที่แน่วแน่ ใช้พลังงานต่ำ และต้นทุนต่ำ

ผลกระทบของการใช้พลังงานต่อเวลาแฝงและประสิทธิภาพ

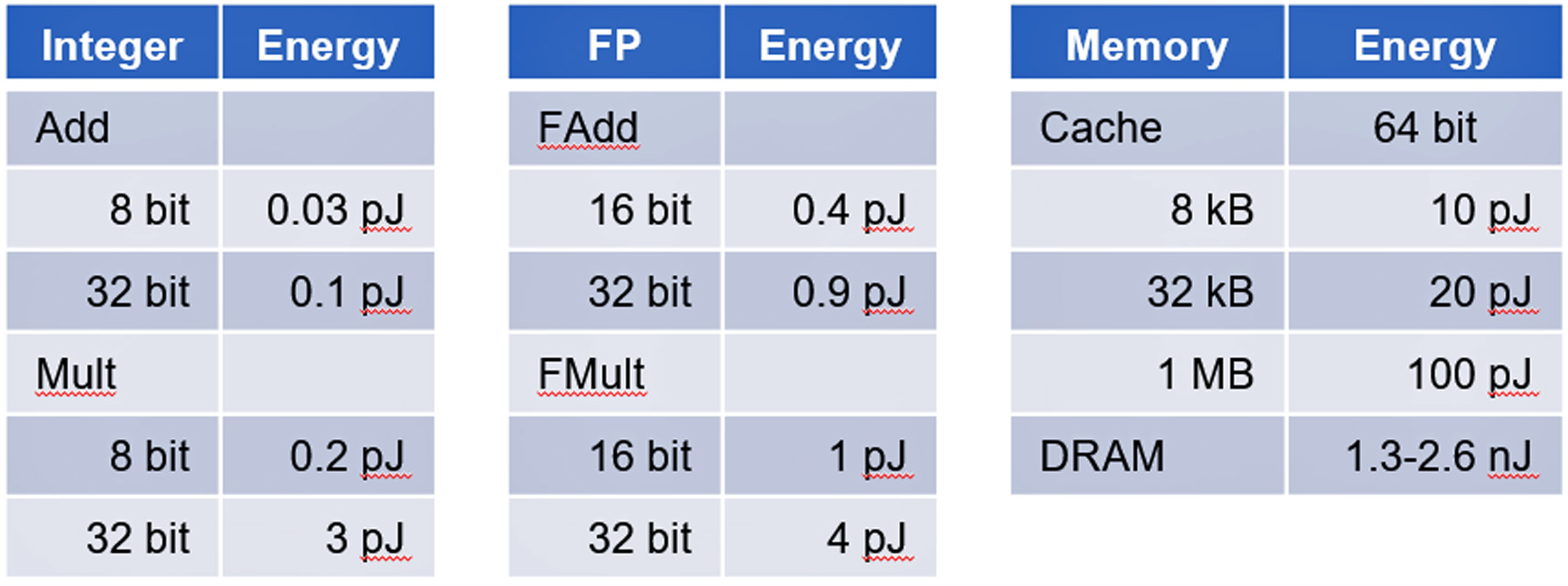

การใช้พลังงานใน CMOS ICs ถูกครอบงำโดยการเคลื่อนที่ของข้อมูล ไม่ใช่การประมวลผลข้อมูล

การศึกษาของมหาวิทยาลัยสแตนฟอร์ดที่นำโดยศาสตราจารย์มาร์ค โฮโรวิทซ์ แสดงให้เห็นว่าการใช้พลังงานในการเข้าถึงหน่วยความจำนั้นใช้พลังงานในระดับที่มากกว่าการคำนวณลอจิกดิจิทัลขั้นพื้นฐาน ดูตารางที่ 2

ตัวเร่งความเร็ว AD และ GenAI เป็นตัวอย่างสำคัญของอุปกรณ์ที่มีการเคลื่อนย้ายข้อมูลซึ่งก่อให้เกิดความท้าทายในการควบคุมการใช้พลังงาน

สรุป

การอนุมาน AD และ GenAI ก่อให้เกิดความท้าทายที่ไม่สำคัญเพื่อให้บรรลุการใช้งานที่ประสบความสำเร็จ VSORA สามารถนำเสนอโซลูชันฮาร์ดแวร์ที่ครอบคลุมและซอฟต์แวร์ที่รองรับเพื่อตอบสนองความต้องการที่สำคัญทั้งหมดในการจัดการ AD L4/L5 และ GenAI เช่นการเร่งความเร็ว GPT-4 ด้วยต้นทุนที่เป็นไปได้ในเชิงพาณิชย์

รายละเอียดเพิ่มเติมเกี่ยวกับ VSORA และ Tyr และ Jotunn สามารถดูได้ที่ www.vsora.com.

เกี่ยวกับ เลาโร ริซัตติ

Lauro Rizzati เป็นที่ปรึกษาทางธุรกิจของ วีโซร่าซึ่งเป็นสตาร์ทอัพเชิงนวัตกรรมที่นำเสนอโซลูชัน IP ซิลิคอนและชิปซิลิคอน และที่ปรึกษาด้านการตรวจสอบที่มีชื่อเสียงและผู้เชี่ยวชาญในอุตสาหกรรมด้านการจำลองฮาร์ดแวร์ ก่อนหน้านี้เขาดำรงตำแหน่งในฝ่ายบริหาร การตลาดผลิตภัณฑ์ การตลาดเชิงเทคนิค และวิศวกรรม

ยังอ่าน:

Soitec คือวิศวกรรมแห่งอนาคตของอุตสาหกรรมเซมิคอนดักเตอร์

ISO 21434 สำหรับการพัฒนา SoC ที่ตระหนักถึงความปลอดภัยทางไซเบอร์

การบำรุงรักษาเชิงคาดการณ์ในบริบทของความปลอดภัยในการใช้งานของยานยนต์

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/automotive/336201-long-standing-roadblock-to-viable-l4-l5-autonomous-driving-and-generative-ai-inference-at-the-edge/

- :มี

- :เป็น

- :ไม่

- $ ขึ้น

- 000

- 1

- 10

- 1800

- 1994

- 20

- 30

- 50

- 5G

- a

- ความสามารถ

- เกี่ยวกับเรา

- สิ่งที่เป็นนามธรรม

- เร่งความเร็ว

- การเร่งความเร็ว

- คันเร่ง

- เร่ง

- เข้า

- Accessed

- การเข้าถึง

- บรรลุ

- ประสบความสำเร็จ

- ข้าม

- การกระทำ

- ที่เกิดขึ้นจริง

- Ad

- AD

- เพิ่ม

- ที่อยู่

- สูง

- ความก้าวหน้า

- ความได้เปรียบ

- กุนซือ

- มีผลต่อ

- AI

- ขั้นตอนวิธี

- อัลกอริทึม

- อัลกอริทึม

- ทั้งหมด

- ช่วยให้

- ด้วย

- จำนวน

- จำนวน

- an

- และ

- คำตอบ

- ใด

- การใช้งาน

- เข้าใกล้

- สถาปัตยกรรม

- เป็น

- AREA

- ศิลปะ

- AS

- At

- ความสนใจ

- แอตทริบิวต์

- อัตโนมัติ

- ยานยนต์

- อิสระ

- แบนด์วิดธ์

- ตาม

- ขั้นพื้นฐาน

- เป็นพื้น

- BE

- กลายเป็น

- รับ

- ด้านล่าง

- มาตรฐาน

- ที่ดีที่สุด

- ระหว่าง

- พันล้าน

- ทั้งสอง

- ธุรกิจ

- แต่

- by

- แคช

- CAN

- ไม่ได้

- ความสามารถในการ

- เมืองหลวง

- การก่อให้เกิด

- เซลล์

- ท้าทาย

- ความท้าทาย

- ชิป

- ชั้นเรียน

- นาฬิกา

- สนามรบ

- รหัส

- พังทลายลงมา

- ในเชิงพาณิชย์

- ชุมชน

- บริษัท

- การแข่งขัน

- ซับซ้อน

- ซับซ้อน

- ครอบคลุม

- การประนีประนอม

- การคำนวณ

- คำนวณ

- การคำนวณ

- การเชื่อมต่อ

- ผู้ให้คำปรึกษา

- การบริโภค

- บรรจุ

- สิ่งแวดล้อม

- ราคา

- ค่าใช้จ่าย

- ควบคู่

- ซีพียู

- ที่สร้างขึ้น

- วิกฤติ

- ปัจจุบัน

- ตัดขอบ

- วงจร

- ข้อมูล

- การประมวลผล

- ส่งมอบ

- ส่ง

- มอบ

- หนาแน่น

- ขึ้นอยู่กับ

- อธิบาย

- ออกแบบ

- ได้รับการออกแบบ

- นักออกแบบ

- รายละเอียด

- อุปกรณ์

- ต่าง

- ดิจิตอล

- ตัวเลข

- do

- ทำ

- ดอลลาร์

- ขับเคลื่อน

- การขับขี่

- หล่น

- หยด

- กระหาย

- ขอบ

- อย่างมีประสิทธิภาพ

- ทั้ง

- ปลาย

- พลังงาน

- การใช้พลังงาน

- วิศวกร

- ชั้นเยี่ยม

- ทำให้มั่นใจ

- ความกระตือรือร้น

- ESL

- จำเป็น

- ที่จัดตั้งขึ้น

- เคย

- คาย

- ตัวอย่าง

- ตัวอย่าง

- การปฏิบัติ

- ชำนาญ

- ภายนอก

- ครอบครัว

- ไกล

- ฟาร์ม

- ข้อเสนอแนะ

- สองสาม

- สนาม

- รูป

- ชื่อจริง

- ที่ลอย

- รอยพระบาท

- สำหรับ

- แถวหน้า

- พบ

- ก่อตั้งขึ้นเมื่อ

- ภาษาฝรั่งเศส

- ราคาเริ่มต้นที่

- อย่างเต็มที่

- การทำงาน

- อนาคต

- สร้าง

- กำเนิด

- กำเนิด AI

- การค้นหาของ Google

- มากขึ้น

- จัดการ

- ฮาร์ดแวร์

- มี

- he

- จัดขึ้น

- จะช่วยให้

- เธอ

- จุดสูง

- ประสิทธิภาพสูง

- ที่สูงที่สุด

- พระองค์

- ฮอ

- ที่ http

- HTTPS

- ใหญ่

- เป็นลูกผสม

- i

- ICS

- ความคิด

- if

- ii

- การดำเนินงาน

- การใช้งาน

- การดำเนินการ

- สำคัญ

- กำหนด

- in

- ประกอบด้วย

- อุตสาหกรรม

- ผู้เชี่ยวชาญในอุตสาหกรรม

- นวัตกรรม

- ตัวอย่าง

- แทน

- รวบรวม

- เข้าไป

- แนะนำ

- การประดิษฐ์คิดค้น

- ลงทุน

- การลงทุน

- IP

- IT

- ITS

- jpg

- กระโดด

- การเก็บรักษา

- ที่รู้จักกัน

- ภูมิประเทศ

- ใหญ่

- ความแอบแฝง

- นำ

- น้อยลง

- ชั้น

- ระดับ

- กดไลก์

- โหลด

- ตรรกะ

- ยาวนาน

- อีกต่อไป

- LOOKS

- ต่ำ

- หลัก

- การบำรุงรักษา

- การทำ

- การจัดการ

- การจัดการ

- เอกสาร

- เครื่องหมาย

- การตลาด

- มาก

- ความกว้างสูงสุด

- พบ

- ความทรงจำ

- หน่วยความจำ

- มิลลิวินาที

- ต่ำสุด

- ทันสมัย

- เงิน

- ข้อมูลเพิ่มเติม

- การเคลื่อนไหว

- หลาย

- จำนวนมาก

- ใหม่

- คืน

- เด่น

- น่าสังเกต

- ตอนนี้

- ล้าสมัย

- of

- การเสนอ

- on

- ONE

- เพียง

- การดำเนินการ

- or

- ใบสั่ง

- คำสั่งซื้อ

- อื่นๆ

- ผลิตภัณฑ์อื่นๆ

- เกิน

- ค้างคืน

- คุยโว

- ได้สิทธิบัตร

- จุดสูงสุด

- ต่อ

- เปอร์เซ็นต์

- การปฏิบัติ

- ดำเนินการ

- มุมมอง

- กายภาพ

- เวที

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- ความอุดมสมบูรณ์

- จุด

- ตำแหน่ง

- ความเป็นไปได้

- โพสต์

- อำนาจ

- ประยุกต์

- ก่อนหน้านี้

- สำคัญ

- ปัญหา

- กระบวนการ

- การประมวลผล

- การประมวลผล

- หน่วยประมวลผล

- โปรเซสเซอร์

- ผลิตภัณฑ์

- ศาสตราจารย์

- โปรแกรมได้

- การเขียนโปรแกรม

- ความคืบหน้า

- ขับเคลื่อน

- ใส่

- คำสั่ง

- พิสัย

- อย่างรวดเร็ว

- อ่าน

- เรียลไทม์

- ความจริง

- เมื่อเร็ว ๆ นี้

- ลด

- ไม่คำนึงถึง

- ลงทะเบียน

- โดดเด่น

- การจำลองแบบ

- รายงาน

- ต้องการ

- ความต้องการ

- ต้อง

- คำตอบ

- เดียวกัน

- เอเชียตะวันออกเฉียงใต้

- ค้นหา

- วินาที

- เห็น

- การเลือก

- สารกึ่งตัวนำ

- เซ็นเซอร์

- หลาย

- Share

- หุ้น

- น่า

- แสดงให้เห็นว่า

- ซิลิคอน

- ตั้งแต่

- เดียว

- เล็ก

- So

- ซอฟต์แวร์

- ทางออก

- โซลูชัน

- แก้

- บาง

- ค่อนข้าง

- แหล่ง

- ช่องว่าง

- ความเร็ว

- การใช้จ่าย

- Stanford

- มหาวิทยาลัยสแตนฟอร์ด

- การเริ่มต้น

- สถานะ

- รัฐของศิลปะ

- เป็นตัวเอก

- ยังคง

- คล่องตัว

- เข้มงวด

- โครงสร้าง

- ศึกษา

- เป็นกอบเป็นกำ

- ที่ประสบความสำเร็จ

- สนับสนุน

- ที่สนับสนุน

- ที่สนับสนุน

- การประสาน

- ระบบ

- ตาราง

- ปรับปรุง

- เป้า

- กำหนดเป้าหมาย

- วิชาการ

- เทคโนโลยี

- กว่า

- ที่

- พื้นที่

- ก้าวสู่อนาคต

- ของพวกเขา

- พวกเขา

- ที่นั่น

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- พวกเขา

- นี้

- สาม

- ตลอด

- ปริมาณงาน

- อย่างแน่นหนา

- เวลา

- ครั้ง

- ไปยัง

- ในวันนี้

- ลู่

- แบบดั้งเดิม

- การจราจร

- การฝึกอบรม

- โปร่งใส

- สอง

- ชนิด

- ชนิด

- ตามแบบฉบับ

- เป็นปกติ

- เป็นเอกลักษณ์

- หน่วย

- จักรวาล

- มหาวิทยาลัย

- จนกระทั่ง

- อัพเกรด

- ใช้ได้

- ผู้ใช้งาน

- การใช้

- VCs

- บริษัท ร่วมทุน

- ร่วมทุน

- การตรวจสอบ

- กับ

- ผ่านทาง

- ทำงานได้

- จวน

- ไดรฟ์

- รอ

- ผนัง

- คือ

- ทาง..

- ดี

- เมื่อ

- ในขณะที่

- กว้าง

- ความปรารถนา

- กับ

- ภายใน

- เขียน

- ยัง

- อัตราผลตอบแทน

- ลมทะเล