เอกสารทางเทคนิคฉบับใหม่ชื่อ “WS2 ทรานซิสเตอร์ที่มีอะตอมซัลเฟอร์ถูกแทนที่ด้วยอินเทอร์เฟซ: การศึกษาควอนตัม-การขนส่งหลักการแรก” ได้รับการตีพิมพ์โดยนักวิจัยจากมหาวิทยาลัยแห่งชาติ Yang Ming Chiao Tung

นามธรรม

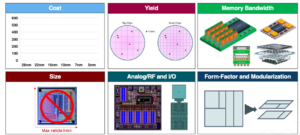

“การลดความต้านทานการสัมผัสถือเป็นหนึ่งในความท้าทายที่สำคัญในการพัฒนาทรานซิสเตอร์โดยใช้วัสดุสองมิติ ในการศึกษานี้ เราทำการคำนวณการขนส่งควอนตัมหลักการแรกโดยการนำโลหะสัมผัสขอบที่ถูกแทนที่กำมะถันบางส่วน/WSX/WS ชนิดใหม่มาใช้2 เพื่อลดความสูงของแผงกั้น Schottky และลดความต้านทานการสัมผัส ในที่นี้ การแทนที่ซัลเฟอร์จะสร้างส่วนของ metamaterial WSX (X = P, As, F และ Cl) โดยใช้กลุ่ม V หรืออะตอมฮาโลเจนเพื่อทดแทนอะตอมซัลเฟอร์ที่ด้านหนึ่งของ WS2 ชั้นเดียว เรายังเปรียบเทียบผลกระทบของการแทนที่ซัลเฟอร์ดังกล่าวต่อการเคลือบโลหะและพันธะของส่วนต่อประสาน หน้าสัมผัสบัฟเฟอร์ WSX ดังกล่าวมีความต้านทานหน้าสัมผัสต่ำเพียง 142 และ 173 Ω·μm สำหรับ p-type Pt/WSP/WS2 และ Ti/WSCl/WS ชนิด n2 หน้าสัมผัสขอบตามลำดับ ยิ่งไปกว่านั้น พลศาสตร์ของโมเลกุลเริ่มต้นยังถูกนำมาใช้เพื่อสังเกตชั้นเดี่ยว WSX แบบสแตนด์อโลนที่เสถียรที่อุณหภูมิห้อง”

ค้นหาเทคนิคการเข้าถึงแบบเปิด กระดาษที่นี่. เผยแพร่เมื่อ มีนาคม 2023

จุง จิฮึง และอื่นๆ “ทรานซิสเตอร์ WS2 ที่มีอะตอมซัลเฟอร์ถูกแทนที่ด้วยอินเทอร์เฟซ: การศึกษาการขนส่งควอนตัมหลักการแรก” เอซีเอส โอเมก้า (2023) https://doi.org/10.1021/acsomega.2c08275.

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/reducing-contact-resistance-in-developing-transistors-based-on-2d-materials/

- :เป็น

- ][หน้า

- 2023

- 2D

- วัสดุ 2 มิติ

- a

- เข้า

- การนำ

- AL

- และ

- AS

- At

- อุปสรรค

- ตาม

- กำลัง

- by

- ความท้าทาย

- เปรียบเทียบ

- ติดต่อเรา

- รายชื่อผู้ติดต่อ

- ที่กำลังพัฒนา

- พลศาสตร์

- ขอบ

- ผลกระทบ

- แสดง

- สำหรับ

- ต่อไป

- บัญชีกลุ่ม

- ความสูง

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- HTTPS

- in

- อินเตอร์เฟซ

- ต่ำ

- สำคัญ

- มีนาคม

- วัสดุ

- โมเลกุล

- ยิ่งไปกว่านั้น

- แห่งชาติ

- ใหม่

- นวนิยาย

- สังเกต

- of

- on

- ONE

- เปิด

- ใบสั่ง

- กระดาษ

- ดำเนินการ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- ก่อ

- การตีพิมพ์

- ลด

- ลด

- แทนที่

- นักวิจัย

- ความต้านทาน

- ตามลำดับ

- ห้อง

- ส่วน

- มั่นคง

- สแตนด์อโลน

- ศึกษา

- อย่างเช่น

- วิชาการ

- พื้นที่

- หัวข้อ

- ไปยัง

- กลับ

- มหาวิทยาลัย

- กับ

- X

- ลมทะเล