มันกลับมาใน 1991 ที่ Cadence ได้ประกาศชื่อผลิตภัณฑ์ Virtuoso เป็นครั้งแรก และนี่ก็ผ่านมา 32 ปีแล้ว และผลิตภัณฑ์ดังกล่าวยังมีชีวิตอยู่และทำได้ค่อนข้างดี Steven Lewis จาก Cadence ให้ข้อมูลอัปเดตเกี่ยวกับสิ่งใหม่ที่พวกเขาเรียกว่า เวอร์ทูโอโซ่ สตูดิโอและทั้งหมดนี้เกี่ยวกับการออกแบบ IC แบบกำหนดเองสำหรับโลกแห่งความเป็นจริง ในช่วง 32 ปีที่ผ่านมา เราได้เห็นกระบวนการเซมิคอนดักเตอร์ดำเนินไปตามกฎของมัวร์ตั้งแต่ 600 นาโนเมตรโดยใช้ planar CMOS และปรับขนาดลงมาจนถึงยุค FinFET ที่ต่ำกว่า 22 นาโนเมตร และไปถึง GAA ที่โหนด 3 นาโนเมตร เห็นได้ชัดว่าความต้องการเครื่องมือ EDA เปลี่ยนไปเนื่องจากโหนดขนาดเล็กทำให้เกิดเอฟเฟกต์ทางกายภาพใหม่ๆ ซึ่งจำเป็นต้องมีการสร้างแบบจำลองและจำลองเพื่อให้แน่ใจว่าซิลิคอนจะประสบความสำเร็จในครั้งแรก

จุดเน้นของ Cadence Virtuoso Studio คือการช่วยให้นักออกแบบ IC รับมือกับความท้าทายในปัจจุบันผ่านหกด้าน:

- เพิ่มความซับซ้อนของกระบวนการ

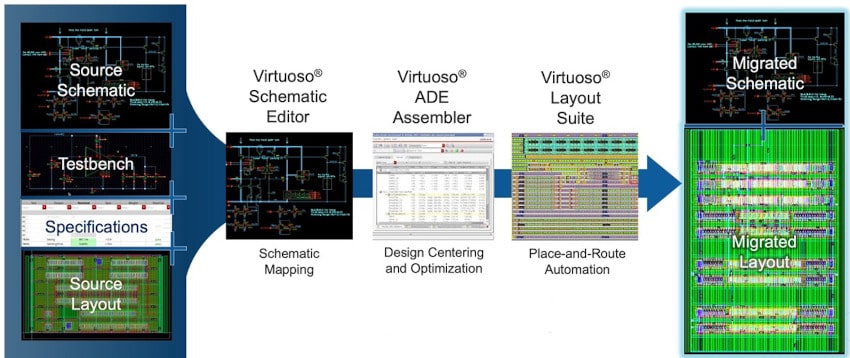

- การจัดการกับการจำลองวงจร 10,000 วินาที

- การออกแบบระบบอัตโนมัติและการย้ายวงจร

- บูรณาการที่แตกต่างกัน

- AI

- การลงนาม การตรวจสอบและการวิเคราะห์ในการออกแบบ

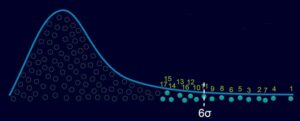

พื้นที่ อัจฉริยะ ADE (สภาพแวดล้อมการออกแบบแอนะล็อก) ช่วยให้วิศวกรวงจรสำรวจการออกแบบแอนะล็อก สัญญาณผสม และ RFIC ผ่านการจับแผนผังและการจำลองวงจร สถาปัตยกรรมของ Virtuoso ADE ได้รับการปรับปรุงใหม่เพื่อการควบคุมงานที่ดีขึ้น ลดการใช้ RAM และเร่งความเร็วการจำลองโดยใช้คลาวด์ ตัวอย่างหนึ่ง RAM ที่ต้องใช้ในการรัน Spectre บนการจำลอง 10,000 ครั้งลดลงจาก 420MB เหลือเพียง 18MB สำหรับการตรวจสอบการจำลอง ในขณะที่การประเมินนิพจน์ลดลงจาก RAM 420MB เหลือเพียง 280MB

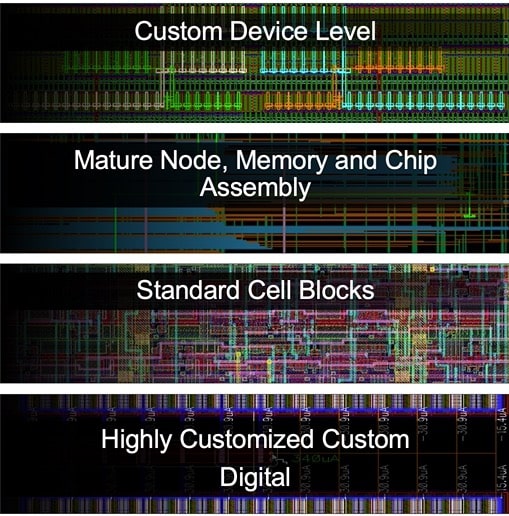

อัพเดท ชุดเค้าโครง Virtuoso ประกอบด้วยเทคโนโลยีสถานที่และเส้นทางสี่ตัวเลือก ซึ่งแต่ละตัวเลือกเหมาะกับงานเฉพาะตัวผ่านสภาพแวดล้อม Virtuoso:

เทคโนโลยี P&R สี่ประการ

การรัน DRC และ LVS เป็นส่วนหนึ่งของการตรวจสอบทางกายภาพ และการรันสิ่งเหล่านี้ในโหมดแบตช์ การแก้ไขและการทำซ้ำ นำไปสู่ตารางการพัฒนาที่ยาวนาน การตรวจสอบยืนยันในการออกแบบช่วยให้สามารถใช้ DRC และ LVS แบบโต้ตอบได้ในขณะที่ทำงานบนโครงร่าง IC ดังนั้นข้อเสนอแนะเกี่ยวกับสิ่งที่ต้องเปลี่ยนแปลงจึงได้รับการเน้นย้ำอย่างรวดเร็ว ซึ่งจะช่วยเร่งประสิทธิภาพการผลิต ผู้ออกแบบโครงร่างที่ใช้ Virtuoso Layout Suite จะได้รับประโยชน์จากการตรวจสอบความถูกต้องในการออกแบบโดยใช้ เพกาซัส เทคโนโลยี DRC และ LVS

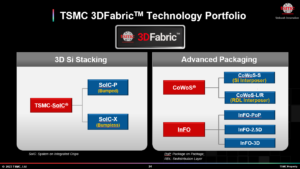

Chiplets, บรรจุภัณฑ์ 2.5D และ 3D ครอบคลุมขอบเขตการออกแบบ PCB, แพ็คเกจ และ IC ที่แยกจากกันแบบดั้งเดิม Virtuoso Studio ช่วยให้สามารถออกแบบร่วมกันและตรวจสอบแพ็คเกจ โมดูล และไอซีได้โดย:

เมื่อมองไปในอนาคตอันใกล้นี้ คุณสามารถคาดหวังที่จะเห็นรายละเอียดเกี่ยวกับวิธีที่ AI ถูกนำมาใช้เพื่อเปลี่ยนจากแผนผังแอนะล็อกไปเป็นเลย์เอาต์โดยอัตโนมัติตามการเรียนรู้ของเครื่องและข้อกำหนด รูปแบบการทดลองใช้ที่สร้างขึ้นอัตโนมัติเหล่านี้จะช่วยเร่งกระบวนการที่ต้องใช้แรงงานมากให้เร็วขึ้น พื้นที่การพัฒนาที่สองสำหรับ AI ที่จะนำไปใช้คือปัญหาในการย้าย IP อนาล็อกที่กำหนดเองไปยังโหนดกระบวนการใหม่ คอยติดตาม.

ลูกค้าในช่วงแรกของ Virtuoso Studio ได้แก่ Analog Devices สำหรับการออกแบบ IC และแพ็คเกจร่วมกัน การออกแบบ IC ระดับแนวหน้าสำหรับผู้บริโภคที่ MediaTek และการโยกย้ายกระบวนการที่ใช้ AI ที่ Renesas

สรุป

Virtuoso Studio ได้เปิดตัวฟีเจอร์ใหม่ที่น่าประทับใจบางอย่างในรีลีส 23.1 ซึ่งทีมออกแบบ IC สามารถเริ่มใช้งานได้เพื่อให้มีประสิทธิผลมากขึ้น โครงสร้างพื้นฐาน Virtuoso มีการเปลี่ยนแปลงเพื่อตอบสนองความท้าทายของกฎของ Moore การจำลองด้วยการจำลองวงจร 10,000 วินาทีนั้นใช้งานได้จริง รองรับการออกแบบร่วม RFIC และโมดูล 2.5D/3D การตรวจสอบ DRC/LVS ในการออกแบบใช้เวลาน้อยลงมาก และ AI ถูกนำไปใช้กับงานแอนะล็อกอัตโนมัติ

บล็อกที่เกี่ยวข้อง

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- เพลโตบล็อคเชน Web3 Metaverse ข่าวกรอง ขยายความรู้. เข้าถึงได้ที่นี่.

- การสร้างอนาคตโดย Adryenn Ashley เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :มี

- :เป็น

- $ ขึ้น

- 1

- 10

- 3d

- a

- เกี่ยวกับเรา

- เร่ง

- AI

- ทั้งหมด

- ช่วยให้

- ตาม

- และ

- ประกาศ

- ประยุกต์

- สถาปัตยกรรม

- เป็น

- AREA

- พื้นที่

- AS

- At

- โดยอัตโนมัติ

- อัตโนมัติ

- อัตโนมัติ

- กลับ

- ตาม

- BE

- รับ

- กำลัง

- ด้านล่าง

- ประโยชน์ที่ได้รับ

- ดีกว่า

- นำ

- by

- จังหวะ

- โทรศัพท์

- CAN

- จับ

- ความท้าทาย

- เปลี่ยนแปลง

- ทางเลือก

- อย่างเห็นได้ชัด

- เมฆ

- ผู้บริโภค

- ควบคุม

- ประเพณี

- ลูกค้า

- วัน

- ความต้องการ

- ออกแบบ

- นักออกแบบ

- นักออกแบบ

- การออกแบบ

- รายละเอียด

- พัฒนาการ

- อุปกรณ์

- การทำ

- โดเมน

- ลง

- แต่ละ

- ผลกระทบ

- ช่วยให้

- วิศวกร

- ทำให้มั่นใจ

- สิ่งแวดล้อม

- ยุค

- การประเมินผล

- ตัวอย่าง

- คาดหวัง

- สำรวจ

- คุณสมบัติ

- ข้อเสนอแนะ

- ชื่อจริง

- โฟกัส

- สำหรับ

- สี่

- ราคาเริ่มต้นที่

- ต่อไป

- อนาคต

- Go

- มือ

- มี

- ช่วย

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- ไฮไลต์

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- HTML

- HTTPS

- ICS

- ประทับใจ

- in

- ประกอบด้วย

- โครงสร้างพื้นฐาน

- การโต้ตอบ

- IP

- การสัมภาษณ์

- jpg

- แรงงาน

- กฏหมาย

- แบบ

- นำไปสู่

- การเรียนรู้

- ลูอิส

- นาน

- เครื่อง

- เรียนรู้เครื่อง

- มีนาคม

- ความกว้างสูงสุด

- พบ

- การโยกย้าย

- โหมด

- โมดูล

- โมดูล

- การตรวจสอบ

- ข้อมูลเพิ่มเติม

- ชื่อ

- ใกล้

- จำเป็น

- ใหม่

- คุณสมบัติใหม่

- ปม

- โหนด

- of

- on

- ONE

- แพ็คเกจ

- แพคเกจ

- บรรจุภัณฑ์

- ส่วนหนึ่ง

- กายภาพ

- สถานที่

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- โพสต์

- ประยุกต์

- นำเสนอ

- ปัญหา

- กระบวนการ

- ผลิตภัณฑ์

- ประสิทธิผล

- ผลผลิต

- ใส่

- อย่างรวดเร็ว

- แรม

- ถึง

- จริง

- โลกแห่งความจริง

- ลดลง

- ลด

- ปล่อย

- จำเป็นต้องใช้

- เส้นทาง

- วิ่ง

- วิ่ง

- ปรับ

- ที่สอง

- ดูรายละเอียด

- สารกึ่งตัวนำ

- แยก

- ซิลิคอน

- จำลอง

- หก

- มีขนาดเล็กกว่า

- So

- บาง

- บางสิ่งบางอย่าง

- ระยะ

- ข้อกำหนด

- สเปกตรัม

- ความเร็ว

- เริ่มต้น

- เข้าพัก

- สตูดิโอ

- ความสำเร็จ

- ชุด

- ที่สนับสนุน

- เอา

- ใช้เวลา

- งาน

- งาน

- ทีม

- เทคโนโลยี

- ที่

- พื้นที่

- ของพวกเขา

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- ตลอด

- เวลา

- ไปยัง

- เครื่องมือ

- ตามธรรมเนียม

- การทดลอง

- เป็นเอกลักษณ์

- บันทึก

- การใช้

- ใช้

- การตรวจสอบ

- ผ่านทาง

- ดี

- อะไร

- ในขณะที่

- จะ

- กับ

- การทำงาน

- โลก

- ปี

- ลมทะเล