ผู้เชี่ยวชาญที่โต๊ะ: วิศวกรรมเซมิคอนดักเตอร์นั่งลงเพื่อพูดคุยเกี่ยวกับเส้นทางข้างหน้าสำหรับหน่วยความจำในระบบที่มีความหลากหลายมากขึ้น โดยแฟรงก์ เฟอร์โร ผู้อำนวยการกลุ่ม ฝ่ายการจัดการผลิตภัณฑ์ของ จังหวะ; Steven Woo เพื่อนและนักประดิษฐ์ผู้มีชื่อเสียงที่ แรมบัส; จงซิน ยุน นักเทคโนโลยีหน่วยความจำที่ ซีเมนส์ EDA; Randy White ผู้จัดการโปรแกรมโซลูชันหน่วยความจำที่ คีย์ไซท์; และ Frank Schirrmeister รองประธานฝ่ายโซลูชั่นและพัฒนาธุรกิจของ หลอดเลือดแดง. สิ่งต่อไปนี้เป็นข้อความที่ตัดตอนมาจากการสนทนานั้น สามารถพบได้ส่วนหนึ่งของการสนทนานี้ โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม.

![[LR]: แฟรงค์ เฟอร์โร, จังหวะ; สตีเว่น วู, แรมบัส; จงซิน หยุน, ซีเมนส์ EDA; แรนดี้ ไวท์, คีย์ไซท์; และแฟรงค์ เชอร์ไมสเตอร์, Arteris](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[LR]: แฟรงค์ เฟอร์โร, จังหวะ; สตีเว่น วู, แรมบัส; จงซิน หยุน, ซีเมนส์ EDA; แรนดี้ ไวท์, คีย์ไซท์; และแฟรงค์ เชอร์ไมสเตอร์, Arteris

SE: ขณะที่เราต่อสู้กับความต้องการด้าน AI/ML และพลังงาน การกำหนดค่าใดบ้างที่ต้องพิจารณาใหม่ เราจะเห็นการเปลี่ยนแปลงไปจากสถาปัตยกรรม Von Neumann หรือไม่?

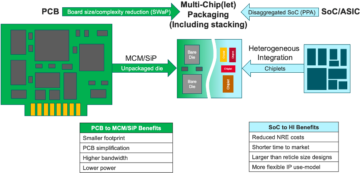

แอ่ว: ในแง่ของสถาปัตยกรรมระบบ มีการแยกไปสองทางที่เกิดขึ้นในอุตสาหกรรม แอปพลิเคชันแบบเดิมที่มีบทบาทสำคัญซึ่งเราใช้งานในระบบคลาวด์บนเซิร์ฟเวอร์ที่ใช้ x86 จะไม่หายไป มีซอฟต์แวร์หลายทศวรรษที่ถูกสร้างขึ้นและพัฒนา และจะต้องอาศัยสถาปัตยกรรมนั้นเพื่อให้ทำงานได้ดี ในทางตรงกันข้าม AI/ML ถือเป็นคลาสใหม่ ผู้คนได้ทบทวนสถาปัตยกรรมและสร้างโปรเซสเซอร์เฉพาะโดเมนขึ้นมาใหม่ เราจะเห็นว่าประมาณสองในสามของพลังงานถูกใช้ไปกับการย้ายข้อมูลระหว่างโปรเซสเซอร์และอุปกรณ์ HBM ในขณะที่มีเพียงประมาณหนึ่งในสามเท่านั้นที่ใช้ไปในการเข้าถึงบิตในแกน DRAM จริงๆ การเคลื่อนย้ายข้อมูลในปัจจุบันมีความท้าทายและมีราคาแพงมากขึ้น เราจะไม่กำจัดความทรงจำ เราต้องการมันเพราะชุดข้อมูลมีขนาดใหญ่ขึ้น ดังนั้นคำถามก็คือ 'อะไรคือแนวทางที่ถูกต้องในการก้าวไปข้างหน้า?' มีการถกเถียงกันมากมายเกี่ยวกับการซ้อน หากเรานำหน่วยความจำนั้นมาวางบนโปรเซสเซอร์โดยตรง มันจะทำหน้าที่สองอย่างให้คุณ ประการแรก แบนด์วิดท์ในปัจจุบันถูกจำกัดโดยแนวชายฝั่งหรือปริมณฑลของชิป นั่นคือสิ่งที่ I/Os ไป แต่ถ้าคุณต้องวางชิปไว้บนโปรเซสเซอร์โดยตรง ตอนนี้คุณสามารถใช้ประโยชน์จากพื้นที่ทั้งหมดของชิปสำหรับการเชื่อมต่อระหว่างกันแบบกระจาย และคุณจะได้รับแบนด์วิธในหน่วยความจำมากขึ้น และสามารถป้อนลงไปโดยตรงในหน่วยความจำได้ โปรเซสเซอร์ ลิงก์จะสั้นลงมาก และประสิทธิภาพการใช้พลังงานอาจเพิ่มขึ้นตามลำดับ 5X ถึง 6X ประการที่สอง จำนวนแบนด์วิธที่คุณจะได้รับเนื่องจากการเชื่อมต่อระหว่างอาเรย์พื้นที่กับหน่วยความจำเพิ่มมากขึ้น เช่นกัน ด้วยปัจจัยจำนวนเต็มหลายตัว การทำสองสิ่งนี้ร่วมกันสามารถให้แบนด์วิธได้มากขึ้นและประหยัดพลังงานมากขึ้น อุตสาหกรรมนี้พัฒนาไปตามความต้องการ และนั่นเป็นวิธีหนึ่งที่เราจะได้เห็นระบบหน่วยความจำเริ่มมีการพัฒนาในอนาคตเพื่อให้มีประสิทธิภาพในการใช้พลังงานมากขึ้นและให้แบนด์วิธมากขึ้น

เหล็ก: เมื่อฉันเริ่มทำงานกับ HBM ครั้งแรกเมื่อประมาณปี 2016 ลูกค้าขั้นสูงบางรายถามว่าสามารถซ้อนกันได้หรือไม่ พวกเขาดูวิธีการซ้อน DRAM ไว้ด้านบนมาระยะหนึ่งแล้วเนื่องจากมีข้อดีที่ชัดเจน จากชั้นกายภาพ โดยพื้นฐานแล้ว PHY จะไม่มีนัยสำคัญใดๆ ซึ่งช่วยประหยัดพลังงานและประสิทธิภาพได้มาก แต่ตอนนี้คุณมีโปรเซสเซอร์ 100W หลายตัวที่มีหน่วยความจำอยู่ด้านบน ความจำก็รับความร้อนไม่ได้ อาจเป็นจุดอ่อนที่สุดในห่วงโซ่ความร้อน ซึ่งสร้างความท้าทายอีกอย่างหนึ่ง มีประโยชน์มากมาย แต่ก็ยังต้องหาวิธีจัดการกับความร้อน ขณะนี้มีแรงจูงใจมากขึ้นในการขับเคลื่อนสถาปัตยกรรมประเภทนั้นไปข้างหน้า เพราะมันช่วยคุณประหยัดโดยรวมในแง่ของประสิทธิภาพและพลังงาน และจะช่วยปรับปรุงประสิทธิภาพการประมวลผลของคุณ แต่มีความท้าทายในการออกแบบทางกายภาพบางประการที่ต้องจัดการ อย่างที่สตีฟพูด เราเห็นสถาปัตยกรรมทุกประเภทที่กำลังจะเปิดตัว ฉันเห็นด้วยอย่างยิ่งว่าสถาปัตยกรรม GPU/CPU จะไม่ไปไหนทั้งนั้น แต่ยังคงมีความโดดเด่นอยู่ ในเวลาเดียวกัน ทุกบริษัทในโลกต่างก็พยายามสร้างกับดักหนูที่ดีกว่าสำหรับใช้ AI ของตน เราเห็น SRAM บนชิปและการรวมกันของหน่วยความจำแบนด์วิธสูง LPDDR ได้รับความสนใจไม่น้อยในปัจจุบันในแง่ของวิธีการใช้ประโยชน์จาก LPDDR ในศูนย์ข้อมูลเนื่องจากพลังงาน เรายังเห็นมีการใช้ GDDR ในแอปพลิเคชันการอนุมาน AI บางตัว รวมถึงระบบหน่วยความจำเก่าทั้งหมดด้วยซ้ำ ตอนนี้พวกเขากำลังพยายามบีบ DDR5 ให้มากที่สุดเท่าที่จะเป็นไปได้ ฉันได้เห็นสถาปัตยกรรมทั้งหมดที่คุณนึกถึง ไม่ว่าจะเป็น DDR, HBM, GDDR หรืออื่นๆ ขึ้นอยู่กับคอร์โปรเซสเซอร์ของคุณในแง่ของมูลค่าเพิ่มโดยรวมของคุณ และจากนั้นคุณจะเจาะลึกสถาปัตยกรรมเฉพาะของคุณได้อย่างไร ระบบหน่วยความจำที่เข้ากันได้ คุณจึงสามารถออกแบบ CPU และสถาปัตยกรรมหน่วยความจำของคุณได้ ขึ้นอยู่กับสิ่งที่มีอยู่

หยุน: อีกประเด็นหนึ่งคือความไม่ผันผวน ตัวอย่างเช่น หาก AI ต้องจัดการกับช่วงเวลาพลังงานระหว่างการใช้งาน AI ที่ใช้ IoT เราก็จำเป็นต้องปิดและเปิดพลังงานจำนวนมาก และข้อมูลทั้งหมดนี้สำหรับการฝึกอบรม AI จะต้องหมุนเวียนครั้งแล้วครั้งเล่า หากเรามีโซลูชันบางประเภทที่สามารถเก็บน้ำหนักเหล่านั้นไว้ในชิป เพื่อที่เราจะได้ไม่ต้องเลื่อนไปมาด้วยน้ำหนักเท่าเดิมเสมอไป ก็จะเป็นการประหยัดพลังงานได้มาก โดยเฉพาะอย่างยิ่งสำหรับ AI ที่ใช้ IoT จะมีวิธีแก้ปัญหาอื่นที่จะช่วยความต้องการพลังงานเหล่านั้น

เชอร์ไมสเตอร์: สิ่งที่ฉันพบว่าน่าสนใจจากมุมมองของ NoC คือจุดที่คุณจะต้องปรับเส้นทางเหล่านี้ให้เหมาะสมจากโปรเซสเซอร์ที่ผ่าน NoC เข้าถึงอินเทอร์เฟซหน่วยความจำที่มีตัวควบคุมที่อาจผ่าน UCIe เพื่อส่งผ่านชิปเล็ตไปยังชิปเล็ตอื่น ซึ่งจากนั้นจะมีหน่วยความจำใน มัน. ไม่ใช่ว่าสถาปัตยกรรมของ Von Neumann นั้นตายไปแล้ว แต่ตอนนี้มีหลายรูปแบบ ขึ้นอยู่กับปริมาณงานที่คุณต้องการคำนวณ จำเป็นต้องพิจารณาในบริบทของความทรงจำ และความทรงจำเป็นเพียงแง่มุมเดียวเท่านั้น คุณได้รับข้อมูลจากพื้นที่ข้อมูลจากที่ใด และมีการจัดเรียงข้อมูลใน DRAM นี้อย่างไร เรากำลังดำเนินการผ่านสิ่งเหล่านี้ทั้งหมด เช่น การวิเคราะห์ประสิทธิภาพของหน่วยความจำ จากนั้นจึงปรับสถาปัตยกรรมระบบให้เหมาะสม มันกระตุ้นให้เกิดนวัตกรรมมากมายสำหรับสถาปัตยกรรมใหม่ๆ ซึ่งฉันไม่เคยนึกถึงเมื่อตอนที่ฉันเรียนมหาวิทยาลัยเกี่ยวกับ Von Neumann ที่อีกด้านหนึ่งสุด คุณมีสิ่งต่างๆ เช่น ตาข่าย ขณะนี้ยังมีสถาปัตยกรรมอีกมากที่ต้องพิจารณา และขับเคลื่อนด้วยแบนด์วิธหน่วยความจำ ความสามารถในการคำนวณ และอื่นๆ ที่ไม่ได้เติบโตในอัตราเดียวกัน

สีขาว: มีแนวโน้มที่เกี่ยวข้องกับการประมวลผลแบบแยกส่วนหรือการประมวลผลแบบกระจาย ซึ่งหมายความว่าสถาปนิกจำเป็นต้องมีเครื่องมือเพิ่มเติมในการกำจัด ลำดับชั้นของหน่วยความจำได้ขยายออกไป มีความหมายรวมอยู่ด้วย เช่นเดียวกับ CXL และหน่วยความจำไฮบริดต่างๆ ที่พร้อมใช้งานสำหรับแฟลชและใน DRAM แอปพลิเคชันแบบขนานกับศูนย์ข้อมูลคือยานยนต์ ยานยนต์มักจะมีเซ็นเซอร์นี้คำนวณด้วย ECU (หน่วยควบคุมอิเล็กทรอนิกส์) ฉันทึ่งกับพัฒนาการของมันสู่ศูนย์ข้อมูล กรอไปข้างหน้า และวันนี้เราได้แจกจ่ายโหนดประมวลผล ที่เรียกว่าตัวควบคุมโดเมน มันเป็นเรื่องเดียวกัน กำลังพยายามแก้ไขปัญหาว่าพลังงานอาจไม่ใหญ่นัก เนื่องจากขนาดของคอมพิวเตอร์ไม่ใหญ่มากนัก แต่ความล่าช้าถือเป็นเรื่องใหญ่สำหรับยานยนต์อย่างแน่นอน ADAS ต้องการแบนด์วิธที่สูงมาก และคุณมีข้อดีที่แตกต่างกันออกไป จากนั้นคุณก็จะมีเซ็นเซอร์เชิงกลเพิ่มขึ้น แต่มีข้อจำกัดที่คล้ายกันในศูนย์ข้อมูล คุณมีห้องเย็นที่ไม่จำเป็นต้องมีเวลาแฝงต่ำ และคุณมีแอปพลิเคชันแบนด์วิธสูงอื่นๆ เป็นเรื่องน่าทึ่งที่ได้เห็นว่าเครื่องมือและตัวเลือกต่างๆ สำหรับสถาปนิกมีการพัฒนาไปมากเพียงใด อุตสาหกรรมตอบสนองได้ดีมากและเราทุกคนก็นำเสนอโซลูชั่นที่หลากหลายที่ป้อนเข้าสู่ตลาด

SE: เครื่องมือออกแบบหน่วยความจำมีการพัฒนาอย่างไร

เชอร์ไมสเตอร์: เมื่อฉันเริ่มต้นด้วยชิปสองสามตัวแรกในช่วงทศวรรษ 90 เครื่องมือระบบที่ใช้มากที่สุดคือ Excel ตั้งแต่นั้นมา ฉันหวังมาโดยตลอดว่ามันอาจจะพังถึงจุดหนึ่งสำหรับสิ่งที่เราทำในระดับระบบ หน่วยความจำ การวิเคราะห์แบนด์วิธ และอื่นๆ สิ่งนี้ส่งผลกระทบต่อทีมของฉันไม่น้อย สมัยนั้นเป็นเรื่องที่ก้าวหน้ามาก แต่สำหรับประเด็นของ Randy ตอนนี้ สิ่งที่ซับซ้อนบางอย่างจำเป็นต้องได้รับการจำลองในระดับความถูกต้อง ซึ่งก่อนหน้านี้ไม่สามารถทำได้หากไม่มีการคำนวณ เพื่อเป็นตัวอย่าง สมมติว่าการเข้าถึง DRAM มีความหน่วงแฝงอยู่บ้าง อาจนำไปสู่การตัดสินใจด้านสถาปัตยกรรมที่ไม่ดี และอาจออกแบบสถาปัตยกรรมการขนส่งข้อมูลบนชิปได้อย่างไม่ถูกต้อง ด้านพลิกก็เป็นจริงเช่นกัน หากคุณมักจะถือว่ากรณีที่เลวร้ายที่สุด คุณจะออกแบบสถาปัตยกรรมมากเกินไป การมีเครื่องมือทำ DRAM และวิเคราะห์ประสิทธิภาพ และการมีโมเดลที่เหมาะสมสำหรับคอนโทรลเลอร์ทำให้สถาปนิกสามารถจำลองโมเดลทั้งหมดได้ นั่นเป็นสภาพแวดล้อมที่น่าทึ่งมาก ความหวังของฉันจากยุค 90 ที่ Excel อาจพังทลายลงเมื่อถึงจุดหนึ่ง เครื่องมือระดับระบบอาจเป็นจริงขึ้นมาได้ เนื่องจากผลกระทบแบบไดนามิกบางอย่างที่คุณไม่สามารถทำได้ใน Excel อีกต่อไป เนื่องจากคุณจำเป็นต้องจำลองมันออกมา โดยเฉพาะอย่างยิ่งเมื่อคุณใช้อินเทอร์เฟซแบบ die-to-die ที่มีลักษณะเฉพาะของ PHY จากนั้นจึงลิงก์เลเยอร์ ลักษณะเช่นการตรวจสอบทั้งหมดว่าทุกอย่างถูกต้องหรือไม่และอาจส่งข้อมูลซ้ำอีกครั้ง การไม่จำลองสถานการณ์เหล่านั้นจะส่งผลให้สถาปัตยกรรมไม่มีประสิทธิภาพสูงสุด

เหล็ก: ขั้นตอนแรกในการประเมินส่วนใหญ่ที่เราทำคือการมอบม้านั่งทดสอบหน่วยความจำเพื่อเริ่มดูประสิทธิภาพของ DRAM นั่นเป็นก้าวที่ยิ่งใหญ่ แม้กระทั่งการทำสิ่งต่างๆ ง่ายๆ เหมือนกับการใช้เครื่องมือในเครื่องเพื่อทำการจำลอง DRAM แต่จากนั้นก็ไปสู่การจำลองเต็มรูปแบบ เราเห็นลูกค้าถามถึงการจำลองประเภทนั้นมากขึ้น การทำให้แน่ใจว่าประสิทธิภาพ DRAM ของคุณเพิ่มขึ้นในยุค 90 นั้นเป็นขั้นตอนแรกที่สำคัญมากในการประเมินใดๆ

แอ่ว: สาเหตุหนึ่งที่คุณเห็นการเพิ่มขึ้นของเครื่องมือจำลองระบบเต็มรูปแบบก็คือ DRAM มีความซับซ้อนมากขึ้น ตอนนี้เป็นเรื่องยากมากที่จะอยู่ในมาตรฐานสำหรับปริมาณงานที่ซับซ้อนเหล่านี้โดยใช้เครื่องมือง่ายๆ เช่น Excel หากคุณดูเอกสารข้อมูลสำหรับ DRAM ในยุค 90 เอกสารข้อมูลเหล่านั้นมีขนาดประมาณ 40 หน้า ตอนนี้มีหลายร้อยหน้าแล้ว นั่นแค่พูดถึงความซับซ้อนของอุปกรณ์เพื่อที่จะดึงแบนด์วิธสูงออกมา คุณจับคู่สิ่งนั้นกับความจริงที่ว่าหน่วยความจำเป็นตัวขับเคลื่อนต้นทุนของระบบ เช่นเดียวกับแบนด์วิดท์และเวลาแฝงที่เกี่ยวข้องกับประสิทธิภาพของโปรเซสเซอร์ นอกจากนี้ยังเป็นตัวขับเคลื่อนที่สำคัญอีกด้วย ดังนั้นคุณจึงต้องจำลองในระดับที่มีรายละเอียดมากขึ้นในตอนนี้ ในแง่ของการไหลของเครื่องมือ สถาปนิกระบบเข้าใจว่าหน่วยความจำเป็นตัวขับเคลื่อนที่สำคัญ ดังนั้นเครื่องมือจึงต้องมีความซับซ้อนมากขึ้นและจำเป็นต้องเชื่อมต่อกับเครื่องมืออื่นๆ เป็นอย่างดี เพื่อให้สถาปนิกระบบได้รับมุมมองทั่วโลกที่ดีที่สุดเกี่ยวกับสิ่งที่เกิดขึ้น โดยเฉพาะอย่างยิ่งกับวิธีที่หน่วยความจำส่งผลกระทบต่อระบบ

หยุน: เมื่อเราก้าวเข้าสู่ยุค AI มีการใช้ระบบ Multi-Core จำนวนมาก แต่เราไม่รู้ว่าข้อมูลไหนไปอยู่ที่ไหน มันจะขนานกับชิปมากขึ้นด้วย ขนาดของหน่วยความจำนั้นใหญ่กว่ามาก หากเราใช้ AI ประเภท ChatGPT การจัดการข้อมูลสำหรับโมเดลต่างๆ ต้องใช้ข้อมูลประมาณ 350MB ซึ่งเป็นข้อมูลจำนวนมหาศาลต่อน้ำหนักหนึ่งๆ และอินพุต/เอาท์พุตจริงจะมีขนาดใหญ่กว่ามาก ปริมาณข้อมูลที่ต้องการที่เพิ่มขึ้นนั้นหมายความว่ามีผลกระทบที่น่าจะเป็นไปได้มากมายที่เราไม่เคยเห็นมาก่อน เป็นการทดสอบที่ท้าทายอย่างยิ่งในการดูข้อผิดพลาดทั้งหมดที่เกี่ยวข้องกับหน่วยความจำจำนวนมากนี้ และ ECC ถูกใช้ทุกที่ แม้แต่ใน SRAM ซึ่งแต่ก่อนไม่เคยใช้ ECC แต่ตอนนี้กลายเป็นเรื่องธรรมดามากสำหรับระบบที่ใหญ่ที่สุด การทดสอบทั้งหมดนั้นเป็นเรื่องที่ท้าทายมากและจำเป็นต้องได้รับการสนับสนุนจากโซลูชัน EDA เพื่อทดสอบเงื่อนไขที่แตกต่างกันทั้งหมดเหล่านั้น

SE: ทีมวิศวกรเผชิญกับความท้าทายอะไรบ้างในแต่ละวัน?

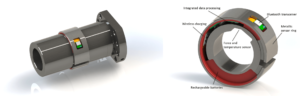

สีขาว: สักวันหนึ่งคุณจะพบฉันในห้องทดลอง ฉันพับแขนเสื้อขึ้น และมือฉันก็สกปรก โดนสายไฟ บัดกรี และอื่นๆ อีกมากมาย ฉันคิดมากเกี่ยวกับการตรวจสอบความถูกต้องของโพสต์ซิลิคอน เราได้พูดคุยเกี่ยวกับการจำลองเบื้องต้นและเครื่องมือออนไดย์ — BiST และอะไรทำนองนั้น ในตอนท้ายของวัน ก่อนที่เราจะจัดส่ง เราต้องการทำการตรวจสอบระบบหรือการทดสอบระดับอุปกรณ์บางรูปแบบ เราคุยกันถึงวิธีเอาชนะกำแพงความทรงจำ เราร่วมค้นหาหน่วยความจำ HBM อะไรทำนองนั้น หากเราดูวิวัฒนาการของเทคโนโลยีบรรจุภัณฑ์ เราจะเริ่มต้นด้วยบรรจุภัณฑ์ที่มีสารตะกั่ว พวกมันไม่ค่อยดีนักสำหรับความสมบูรณ์ของสัญญาณ ทศวรรษต่อมา เราได้ย้ายไปใช้ความสมบูรณ์ของสัญญาณที่ได้รับการปรับปรุง เช่น Ball Grid Array (BGA) เราไม่สามารถเข้าถึงสิ่งนั้นได้ ซึ่งหมายความว่าคุณไม่สามารถทดสอบได้ ดังนั้นเราจึงเกิดแนวคิดนี้ขึ้นมาที่เรียกว่าอุปกรณ์อินเทอร์โพเซอร์ - อินเทอร์โพเซอร์ BGA - และนั่นทำให้เราสามารถประกบฟิกซ์เจอร์พิเศษที่ส่งสัญญาณออกไปได้ จากนั้นเราก็สามารถเชื่อมต่อกับอุปกรณ์ทดสอบได้ ก้าวไปข้างหน้าอย่างรวดเร็วจนถึงวันนี้ และตอนนี้ เรามี HBM และชิปเล็ตแล้ว ฉันจะประกบฟิกซ์เจอร์ของฉันระหว่างบนซิลิคอนอินเตอร์โพเซอร์ได้อย่างไร เราทำไม่ได้ และนั่นคือการต่อสู้ มันเป็นความท้าทายที่ทำให้ฉันตื่นในตอนกลางคืน เราจะดำเนินการวิเคราะห์ความล้มเหลวในภาคสนามกับ OEM หรือลูกค้าระบบได้อย่างไร โดยที่พวกเขาไม่ได้รับประสิทธิภาพ 90% มีข้อผิดพลาดเพิ่มเติมในลิงก์ ไม่สามารถเริ่มต้นได้อย่างถูกต้อง และการฝึกอบรมไม่ทำงาน มันเป็นปัญหาความสมบูรณ์ของระบบหรือไม่?

เชอร์ไมสเตอร์: คุณไม่อยากทำเช่นนี้จากที่บ้านด้วยอินเทอร์เฟซเสมือนแทนที่จะเดินไปที่ห้องแล็บใช่ไหม คำตอบคือการวิเคราะห์ที่คุณสร้างไว้ในชิปไม่ใช่หรือ ด้วยชิปเล็ต เราผสานรวมทุกสิ่งให้ดียิ่งขึ้นไปอีก การนำหัวแร้งของคุณเข้าไปนั้นไม่มีทางเลือกจริงๆ ดังนั้นจึงจำเป็นต้องมีวิธีสำหรับการวิเคราะห์บนชิป เรามีปัญหาเดียวกันสำหรับ NoC ผู้คนมองไปที่ NoC และคุณส่งข้อมูลแล้วมันหายไป เราจำเป็นต้องใส่การวิเคราะห์เพื่อให้ผู้คนสามารถแก้ไขจุดบกพร่องได้ และนั่นขยายไปถึงระดับการผลิต เพื่อให้คุณสามารถทำงานจากที่บ้านได้ในที่สุด และทำทุกอย่างโดยใช้การวิเคราะห์ชิป

เหล็ก: โดยเฉพาะอย่างยิ่งเมื่อมีหน่วยความจำแบนด์วิธสูง คุณจะไม่สามารถเข้าไปข้างในได้ เมื่อเราออกใบอนุญาต PHY เราก็มีผลิตภัณฑ์ที่ใช้ร่วมกับสิ่งนั้นด้วย ดังนั้นคุณจึงสามารถจับตาดูทุก ๆ 1,024 บิตเหล่านั้นได้ คุณสามารถเริ่มอ่านและเขียน DRAM จากเครื่องมือได้ เพื่อที่คุณจะได้ไม่ต้องเข้าไปข้างในจริงๆ ฉันชอบความคิดของผู้ขัดขวาง เรานำพินบางส่วนออกจากอินเทอร์โพเซอร์ในระหว่างการทดสอบ ซึ่งคุณไม่สามารถทำได้ในระบบ การเข้าสู่ระบบ 3 มิติเหล่านี้เป็นเรื่องท้าทายมาก แม้จากมุมมองของโฟลว์เครื่องมือออกแบบ ดูเหมือนว่าบริษัทส่วนใหญ่จะดำเนินการโฟลว์ของตนเองกับเครื่องมือ 2.5D เหล่านี้จำนวนมาก เรากำลังเริ่มรวบรวมวิธีการที่เป็นมาตรฐานมากขึ้นเพื่อสร้างระบบ 2.5D ตั้งแต่ความสมบูรณ์ของสัญญาณ กำลัง และการไหลทั้งหมด

สีขาว: เมื่อสิ่งต่าง ๆ ดำเนินต่อไป ฉันหวังว่าเราจะยังสามารถรักษาความแม่นยำในระดับเดิมได้ ฉันอยู่ในกลุ่มการปฏิบัติตามข้อกำหนดฟอร์มแฟคเตอร์ของ UCIe ฉันกำลังดูวิธีการจำแนกลักษณะของแม่พิมพ์ที่ดีที่รู้จัก แม่พิมพ์สีทอง ท้ายที่สุดแล้ว การดำเนินการนี้จะใช้เวลานานกว่านี้มาก แต่เราจะพบสื่อกลางที่น่าพอใจระหว่างประสิทธิภาพและความแม่นยำของการทดสอบที่เราต้องการ และความยืดหยุ่นที่อยู่ภายใน

เชอร์ไมสเตอร์: หากฉันพิจารณาชิปเล็ตและการนำไปใช้ในสภาพแวดล้อมการผลิตที่เปิดกว้างมากขึ้น การทดสอบถือเป็นความท้าทายที่ยิ่งใหญ่อย่างหนึ่งในการทำให้ทำงานได้อย่างถูกต้อง หากฉันเป็นบริษัทขนาดใหญ่และฉันควบคุมทุกด้าน ฉันสามารถจำกัดสิ่งต่างๆ ได้อย่างเหมาะสมเพื่อให้การทดสอบและอื่นๆ เป็นไปได้ หากฉันต้องการใช้สโลแกนของ UCIe ที่ว่า UCI อยู่ห่างจาก PCI เพียงหนึ่งตัวอักษร และฉันจินตนาการถึงอนาคตที่การประกอบ UCIe จะกลายเป็น จากมุมมองของการผลิต เช่น สล็อต PCI ในพีซีในปัจจุบัน ดังนั้นด้านการทดสอบสำหรับสิ่งนั้นจริงๆ ที่ท้าทาย. เราจำเป็นต้องหาทางแก้ไข มีงานต้องทำมากมาย

บทความที่เกี่ยวข้อง

อนาคตแห่งความทรงจำ (ส่วนที่ 1 ของด้านบนปัดเศษได้)

ตั้งแต่ความพยายามที่จะแก้ไขปัญหาด้านความร้อนและพลังงานไปจนถึงบทบาทของ CXL และ UCIe อนาคตมีโอกาสมากมายสำหรับหน่วยความจำ

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/rethinking-memory/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- $ ขึ้น

- 1

- 2016

- 3d

- 40

- a

- เกี่ยวกับเรา

- ข้างบน

- เข้า

- การเข้าถึง

- ความถูกต้อง

- ที่เกิดขึ้นจริง

- จริง

- AD

- เพิ่ม

- ที่อยู่

- การนำมาใช้

- สูง

- ความได้เปรียบ

- ข้อได้เปรียบ

- อีกครั้ง

- AI

- การฝึกอบรม AI

- AI / ML

- ทั้งหมด

- อนุญาตให้

- ช่วยให้

- ด้วย

- เสมอ

- จำนวน

- an

- การวิเคราะห์

- การวิเคราะห์

- และ

- อื่น

- คำตอบ

- ใด

- อีกต่อไป

- ทุกแห่ง

- การใช้งาน

- การใช้งาน

- อย่างเหมาะสม

- สถาปนิก

- สถาปัตยกรรม

- เป็น

- AREA

- รอบ

- จัด

- แถว

- AS

- ขอให้

- แง่มุม

- ด้าน

- การชุมนุม

- สมมติ

- At

- ความพยายามในการ

- ยานยนต์

- ใช้ได้

- ไป

- กลับ

- ไม่ดี

- ลูกบอล

- แบนด์วิดธ์

- บาร์

- ตาม

- เป็นพื้น

- รากฐาน

- BE

- เพราะ

- กลายเป็น

- จะกลายเป็น

- รับ

- ก่อน

- กำลัง

- ประโยชน์ที่ได้รับ

- ที่ดีที่สุด

- ดีกว่า

- ระหว่าง

- ใหญ่

- ที่ใหญ่กว่า

- บิต

- ทำลาย

- นำมาซึ่ง

- สร้าง

- สร้าง

- ธุรกิจ

- การพัฒนาธุรกิจ

- แต่

- by

- จังหวะ

- ที่เรียกว่า

- มา

- CAN

- สามารถรับ

- ความสามารถในการ

- กรณี

- ศูนย์

- บาง

- อย่างแน่นอน

- โซ่

- ท้าทาย

- ความท้าทาย

- ท้าทาย

- ลักษณะ

- สมบัติ

- การตรวจสอบ

- ชิป

- ชิป

- ชั้น

- ชัดเจน

- เมฆ

- ผู้สมัครที่ไม่รู้จัก

- ห้องเย็น

- รวม

- อย่างไร

- มา

- ร่วมกัน

- บริษัท

- บริษัท

- ซับซ้อน

- ความซับซ้อน

- การปฏิบัติตาม

- ซับซ้อน

- คำนวณ

- คอมพิวเตอร์

- การคำนวณ

- แนวคิด

- เงื่อนไข

- เชื่อมต่อ

- ถือว่า

- ข้อ จำกัด

- สิ่งแวดล้อม

- ตรงกันข้าม

- ควบคุม

- ตัวควบคุม

- การสนทนา

- แกน

- แก้ไข

- ราคา

- ได้

- คู่

- ซีพียู

- สร้าง

- ลูกค้า

- ลูกค้า

- ข้อมูล

- ศูนย์ข้อมูล

- ชุดข้อมูล

- วัน

- วันต่อวัน

- วัน

- ตาย

- จัดการ

- ทศวรรษที่ผ่านมา

- การตัดสินใจ

- อย่างแน่นอน

- ความต้องการ

- ทั้งนี้ขึ้นอยู่กับ

- ขึ้นอยู่กับ

- ออกแบบ

- การออกแบบ

- รายละเอียด

- พัฒนาการ

- เครื่อง

- ตาย

- ต่าง

- ยาก

- โดยตรง

- ผู้อำนวยการ

- การสนทนา

- การกำจัด

- โดดเด่น

- กระจาย

- คอมพิวเตอร์แบบกระจาย

- do

- ทำ

- ไม่

- การทำ

- โดเมน

- เด่น

- ทำ

- Dont

- ลง

- ขับเคลื่อน

- คนขับรถ

- ในระหว่าง

- พลวัต

- ก่อน

- ผลกระทบ

- อย่างมีประสิทธิภาพ

- ที่มีประสิทธิภาพ

- อิเล็กทรอนิกส์

- ปลาย

- พลังงาน

- ชั้นเยี่ยม

- ทั้งหมด

- สิ่งแวดล้อม

- อุปกรณ์

- ยุค

- ข้อผิดพลาด

- โดยเฉพาะอย่างยิ่ง

- อีเธอร์ (ETH)

- การประเมินผล

- การประเมินผล

- แม้

- ในที่สุด

- ทุกๆ

- ทุกอย่าง

- ทุกที่

- วิวัฒนาการ

- คาย

- วิวัฒน์

- วิวัฒนาการ

- ตัวอย่าง

- Excel

- ขยาย

- แพง

- ขยาย

- สุดโต่ง

- อย่างยิ่ง

- Eyes

- ใบหน้า

- ความจริง

- ปัจจัย

- ความล้มเหลว

- ที่น่าสนใจ

- FAST

- เป็นไปได้

- มนุษย์

- ความจงรักภักดี

- สนาม

- รูป

- ในที่สุด

- หา

- ชื่อจริง

- แฟลช

- ความยืดหยุ่น

- พลิก

- ไหล

- ดังต่อไปนี้

- รอยพระบาท

- สำหรับ

- ฟอร์ม

- ออกมา

- ข้างหน้า

- พบ

- ตรงไปตรงมา

- ราคาเริ่มต้นที่

- เต็ม

- ต่อไป

- อนาคต

- ได้รับ

- ได้รับ

- ให้

- กำหนด

- เหตุการณ์ที่

- Go

- ไป

- ไป

- โกลเด้น

- ไป

- ดี

- งานที่ดี

- ได้

- ตะแกรง

- บัญชีกลุ่ม

- การเจริญเติบโต

- มี

- การจัดการ

- มือ

- มีความสุข

- มี

- มี

- หัว

- ช่วย

- ลำดับชั้น

- จุดสูง

- ถือ

- หน้าแรก

- ความหวัง

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- ทำอย่างไร

- HTML

- HTTPS

- ใหญ่

- ร้อย

- เป็นลูกผสม

- i

- ความคิด

- if

- ภาพ

- ที่กระทบ

- ส่งผลกระทบต่อ

- สำคัญ

- ปรับปรุง

- in

- แรงจูงใจ

- รวม

- อย่างไม่ถูกต้อง

- เพิ่ม

- ขึ้น

- เป็นรายบุคคล

- อุตสาหกรรม

- ข้อมูล

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- ภายใน

- รวบรวม

- ความสมบูรณ์

- การเชื่อมต่อระหว่างกัน

- อินเตอร์เฟซ

- เข้าไป

- ที่เกี่ยวข้องกับ

- ปัญหา

- ปัญหา

- IT

- ITS

- ตัวเอง

- การสัมภาษณ์

- เพียงแค่

- ทราบ

- ที่รู้จักกัน

- ห้องปฏิบัติการ

- ใหญ่

- ที่มีขนาดใหญ่

- ใหญ่ที่สุด

- ความแอบแฝง

- ต่อมา

- ชั้น

- นำ

- การเรียนรู้

- จดหมาย

- ชั้น

- License

- กดไลก์

- ถูก จำกัด

- LINK

- การเชื่อมโยง

- ในประเทศ

- ดู

- ที่ต้องการหา

- Lot

- จำนวนมาก

- ต่ำ

- เก็บรักษา

- ทำ

- การทำ

- การจัดการ

- ผู้จัดการ

- การผลิต

- หลาย

- ตลาด

- ความกว้างสูงสุด

- อาจจะ

- me

- วิธี

- หมายความว่า

- เชิงกล

- กลาง

- ความทรงจำ

- หน่วยความจำ

- อาจ

- โมเดล

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ย้าย

- ย้าย

- การเคลื่อนไหว

- การย้าย

- มาก

- my

- จำเป็นต้อง

- ความต้องการ

- ไม่เคย

- ใหม่

- คืน

- โหนด

- ตอนนี้

- จำนวน

- of

- ปิด

- เก่า

- on

- ONE

- เพียง

- เปิด

- โอกาส

- เพิ่มประสิทธิภาพ

- การปรับให้เหมาะสม

- การเพิ่มประสิทธิภาพ

- ตัวเลือกเสริม (Option)

- Options

- or

- ใบสั่ง

- อื่นๆ

- ผลิตภัณฑ์อื่นๆ

- ออก

- ทั้งหมด

- เอาชนะ

- ของตนเอง

- แพคเกจ

- บรรจุภัณฑ์

- หน้า

- Parallel

- ส่วนหนึ่ง

- ในสิ่งที่สนใจ

- ส่ง

- เส้นทาง

- เส้นทาง

- PC

- คน

- ดำเนินการ

- การปฏิบัติ

- มุมมอง

- กายภาพ

- ทางร่างกาย

- ต้นสน

- ดาวเคราะห์

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- จุด

- เป็นไปได้

- ที่อาจเกิดขึ้น

- อำนาจ

- ประธาน

- ก่อนหน้านี้

- อาจ

- ปัญหา

- หน่วยประมวลผล

- โปรเซสเซอร์

- ผลิตภัณฑ์

- การจัดการผลิตภัณฑ์

- การผลิต

- โครงการ

- เหมาะสม

- อย่างถูกต้อง

- ให้

- ใส่

- คำถาม

- ทีเดียว

- การยก

- คะแนน

- ค่อนข้าง

- การอ่าน

- จริงๆ

- ที่เกี่ยวข้อง

- วางใจ

- จำเป็นต้องใช้

- ต้อง

- แก้ไข

- การตอบสนอง

- ผล

- กำจัด

- ขวา

- ขึ้น

- บทบาท

- ม้วน

- วิ่ง

- วิ่ง

- เดียวกัน

- ลด

- เงินออม

- คำพูด

- ขนาด

- ที่สอง

- เห็น

- เห็น

- ดูเหมือนว่า

- เห็น

- อรรถศาสตร์

- สารกึ่งตัวนำ

- ส่ง

- เซ็นเซอร์

- เซ็นเซอร์

- เซิร์ฟเวอร์

- หลาย

- แผ่น

- เปลี่ยน

- เรือ

- ด้าน

- ด้านข้าง

- ซีเมนส์

- สัญญาณ

- สัญญาณ

- ซิลิคอน

- คล้ายคลึงกัน

- ง่าย

- จำลอง

- การจำลอง

- ตั้งแต่

- เดียว

- ขนาด

- สล็อต

- So

- ซอฟต์แวร์

- ทางออก

- โซลูชัน

- บาง

- ซับซ้อน

- พูด

- พิเศษ

- การใช้จ่าย

- บีบ

- กอง

- ซ้อนกัน

- การสุม

- มาตรฐาน

- จุดยืน

- เริ่มต้น

- ข้อความที่เริ่ม

- ที่เริ่มต้น

- ขั้นตอน

- สตีฟ

- steven

- ยังคง

- การเก็บรักษา

- จัดเก็บ

- การต่อสู้

- อย่างเช่น

- ที่สนับสนุน

- แน่ใจ

- ระบบ

- ระบบ

- ตาราง

- เอา

- คุย

- ทีม

- นักเทคโนโลยี

- เทคโนโลยี

- เงื่อนไขการใช้บริการ

- ทดสอบ

- การทดสอบ

- การทดสอบ

- กว่า

- ที่

- พื้นที่

- ก้าวสู่อนาคต

- ของพวกเขา

- พวกเขา

- แล้วก็

- ที่นั่น

- ร้อน

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- พวกเขา

- สิ่ง

- สิ่ง

- คิด

- ที่สาม

- นี้

- เหล่านั้น

- คิดว่า

- ตลอด

- เวลา

- ไปยัง

- ในวันนี้

- ร่วมกัน

- เครื่องมือ

- เครื่องมือ

- ด้านบน

- โดยสิ้นเชิง

- การแลกเปลี่ยน

- แบบดั้งเดิม

- ตามธรรมเนียม

- การฝึกอบรม

- การขนส่ง

- เทรนด์

- จริง

- พยายาม

- สอง

- สองในสาม

- ชนิด

- เข้าใจ

- หน่วย

- มหาวิทยาลัย

- us

- ใช้

- มือสอง

- การใช้

- การตรวจสอบ

- ความคุ้มค่า

- รูปแบบ

- ต่างๆ

- มาก

- รอง

- Vice President

- รายละเอียด

- เสมือน

- ของ

- ที่เดิน

- ผนัง

- ต้องการ

- คือ

- ทาง..

- we

- น้ำหนัก

- ดี

- คือ

- อะไร

- อะไรก็ตาม

- เมื่อ

- ว่า

- ที่

- ในขณะที่

- ขาว

- ทั้งหมด

- ทำไม

- จะ

- กับ

- ไม่มี

- แอ่ว

- งาน

- ทำงานที่บ้าน

- การทำงาน

- แย่ที่สุด

- การเขียน

- เธอ

- ของคุณ

- ลมทะเล