ในการทำงานอุปกรณ์ CPU สมัยใหม่ 80% ถึง 90% ของการใช้พลังงานและการหน่วงเวลามีสาเหตุมาจากการเคลื่อนที่ของข้อมูลระหว่าง CPU และหน่วยความจำนอกชิป เพื่อบรรเทาความกังวลด้านประสิทธิภาพนี้ นักออกแบบจึงเพิ่มหน่วยความจำบนชิปเพิ่มเติมให้กับ CPU ของตน ตามเนื้อผ้า SRAM เป็นประเภทหน่วยความจำ CPU บนชิปที่ใช้กันอย่างแพร่หลายที่สุด น่าเสียดายที่ปัจจุบัน SRAM ถูกจำกัดไว้ที่ขนาดหลายร้อยเมกะไบต์ ข้อจำกัดของหน่วยความจำบนชิปนี้อาจไม่เพียงพอสำหรับแอปพลิเคชันระดับแนวหน้า

แอปพลิเคชัน CPU ในอนาคต เช่น การเขียนโปรแกรมโมเดลภาษา AI และการประมวลผลภาพสำหรับวิดีโอ 8K UHD จะต้องใช้แบนด์วิดธ์การเข้าถึงหน่วยความจำ I/O ในช่วง 10 เทราไบต์/วินาที เพื่อให้เป็นไปตามข้อกำหนดแบนด์วิธเหล่านี้ หน่วยความจำ CPU บนชิปจะต้องมีขนาดมากกว่า 1 เทราไบต์ อาจจำเป็นต้องใช้ทางเลือก SRAM เพื่อให้เป็นไปตามข้อกำหนดหน่วยความจำบนชิปในอนาคต วิธีแก้ไขปัญหาหนึ่งที่เป็นไปได้คือการใช้ Resistive Random Access Memory (ReRAM) [1,2,3]

อุปกรณ์ ReRAM เป็นเซลล์หน่วยความจำแบบไม่ลบเลือนซึ่งมีวัสดุเมมเบรน วัสดุเหล่านี้ทำหน้าที่เป็นฉนวนอิเล็กทริก เมื่อใช้ไฟฟ้าแรงสูงเพียงพอ จะเกิดเส้นทางการนำไฟฟ้า วัสดุหน่วยความจำทั่วไปที่ใช้เป็นเมมริสเตอร์ประกอบด้วย HfO2, ทา2O5และ TiO2- [4] สถานะความต้านทานของเซลล์หน่วยความจำสามารถอ่านได้โดยใช้วงจรอิเล็กทรอนิกส์เพื่อตรวจสอบว่าเซลล์หน่วยความจำถูกตั้งโปรแกรมหรือลบหรือไม่ ซึ่งจะช่วยระบุสถานะของบิตหน่วยความจำ เซลล์หน่วยความจำ ReRAM สามารถซ้อนกันในแนวตั้งได้ เช่นเดียวกับสถาปัตยกรรม 3D-NAND เพื่อเพิ่มความหนาแน่นในการจัดเก็บข้อมูล

ในบทความนี้, SEMulator3D การผลิตเสมือนจริง จะใช้สำหรับการค้นหาเส้นทางกระบวนการและการแสดงภาพสถาปัตยกรรม 3D ReRAM ที่เป็นไปได้ เราจะประมาณความต้านทานของเซลล์โดยเป็นฟังก์ชันของรูปร่างเซลล์หน่วยความจำ พร้อมด้วยประสิทธิภาพของ Id-Vg ของทรานซิสเตอร์ช่องสัญญาณแบบฝังในอุปกรณ์ ReRAM

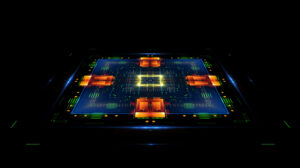

โมเดล 3D ReRAM แสดงในรูปที่ 1 อุปกรณ์มี wordlines (WL) 64 เลเยอร์ โดยมีเสาวางอยู่ในอาร์เรย์เว้นระยะหกเหลี่ยม ข้อความนี้ประกอบขึ้นด้วยชั้นตัวนำโลหะและไดอิเล็กทริกออกไซด์ที่สลับกัน เสาถูกแกะสลักผ่าน WL จากนั้นชั้นบางๆ ของวัสดุหน่วยความจำจะถูกวางลงบนผนังด้านข้างของเสา วัสดุหน่วยความจำจะถูกลบออกจากด้านล่างและด้านบนของเสา เหลือเพียงวัสดุที่ผนังด้านข้างของเสา เสานั้นเต็มไปด้วยโลหะทนไฟและทังสเตน

ภายใต้ชั้นอาเรย์จะมีหน้าสัมผัสและโลหะเชื่อมต่อระหว่างแหล่งกำเนิด ท่อระบายน้ำ และประตูของทรานซิสเตอร์เอฟเฟกต์สนามแบบเกท (GAA FET) ช่องระบายทรานซิสเตอร์เชื่อมต่อกับเสาอาร์เรย์หน่วยความจำและรวมเข้ากับวงจร WL เพื่อให้ฟังก์ชันแก่เซลล์หน่วยความจำแต่ละเซลล์

เซลล์หน่วยความจำประกอบด้วยอิเล็กโทรดโลหะ 2 อิเล็กโทรด: ข้อความที่เป็นตัวนำโลหะและอิเล็กโทรดโลหะทนไฟ (รูปที่ XNUMX) ในระหว่างการจำลองกระบวนการเสมือนของอุปกรณ์นี้ เราจะใช้ตัวแปรกระบวนการเพื่อตั้งค่าและรีเซ็ตเมมเบรน แรงดันไฟฟ้าที่ใช้อย่างจงใจจะสร้างเส้นทางนำไฟฟ้าด้วยกล้องจุลทรรศน์ที่เรียกว่าเส้นใยนำไฟฟ้า เมื่อใช้สัญญาณไฟฟ้าที่มีขั้วต่างกัน ไอออนที่มีประจุภายในเมมเบรนจะเคลื่อนที่เพื่อสร้าง (ตั้งค่า) หรือละลาย (รีเซ็ต) เส้นใยนำไฟฟ้า

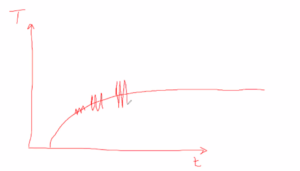

ความต้านทานของเส้นใยนำไฟฟ้าจะแตกต่างกันไปตามแรงดันไฟฟ้าของโปรแกรมที่แตกต่างกัน สถานะความต้านทานต่ำอยู่ในช่วง 10k โอห์ม (ตั้งค่า) และสถานะความต้านทานสูงอยู่ในช่วง 1M โอห์ม (รีเซ็ต) [5] เราได้พัฒนาแบบจำลองเสมือนจริงเพื่อสาธิตความต้านทานการสลับของอุปกรณ์ 3D ReRAM โดยผลลัพธ์จะแสดงในรูปที่ 3 สถานะความต้านทานสูงของเมมเบรนมีความต้านทานสูงกว่าสถานะความต้านทานต่ำประมาณ 100 เท่า

จากนั้นจึงทำการออกแบบการทดลองเสมือนจริง (DOE) เพื่อให้เข้าใจความสัมพันธ์ระหว่างอัตราส่วนความต้านทานต่อเซลล์หน่วยความจำกับขนาดและรูปร่างของเซลล์หน่วยความจำได้ดียิ่งขึ้น ตัวแปรในการทดลองได้แก่ พีลลาร์ซีดี ความหนาของ WL และความหนาของเมมเบรน การวิเคราะห์ผลลัพธ์ของ DOE บ่งชี้ว่าเสาซีดีและความหนาของเมมเบรนเป็นตัวขับเคลื่อนการตอบสนองที่สำคัญที่สุด รูปที่ 4 แสดงโครงร่างของอัตราส่วนความต้านทานของเซลล์หน่วยความจำเทียบกับตัวแปรทั้งสองนี้ มีการเปลี่ยนแปลงความต้านทานเซลล์หน่วยความจำถึง 3 เท่าสำหรับค่ารัศมีเสาและความหนาของเมมเบรนที่สูง ความแตกต่างในรูปร่างของเซลล์หน่วยความจำในช่วงที่ศึกษาจะไม่ส่งผลต่อความสามารถในการอ่านสถานะหน่วยความจำของเมมเบรน แต่อาจส่งผลต่อความสามารถในการแยกแยะสถานะของโปรแกรมในรูปแบบมัลติบิตต่ออุปกรณ์เซลล์

สามารถตั้งโปรแกรมเมมเบรนได้โดยใช้กระแส < 0.10 uA และแรงดันไฟฟ้า < 0.5V การตั้งค่าแรงดันและกระแสเหล่านี้จะช่วยให้เมมริสเตอร์ (หน่วยความจำ ReRAM) สามารถรวมเป็นหน่วยความจำบนชิปเข้ากับอุปกรณ์ลอจิกขั้นสูงได้อย่างง่ายดาย การจำลองอุปกรณ์ SEMulator3D ได้แสดงให้เห็นก่อนหน้านี้ว่าทรานซิสเตอร์ใต้อาร์เรย์ GAA FET ควรจะสามารถขับเคลื่อนแรงดันไฟฟ้าและกระแสไฟฟ้าที่ต้องการโดยสถานะการตั้งค่าและรีเซ็ตของเซลล์หน่วยความจำ memristor [6]

ปัญหาสำคัญสองประการของอุปกรณ์ CPU สมัยใหม่คือการใช้พลังงานและเวลาหน่วงที่เกิดจากการย้ายข้อมูลระหว่าง CPU และหน่วยความจำนอกชิป การเพิ่มขนาดของหน่วยความจำบนชิปอาจช่วยแก้ปัญหาเหล่านี้ได้ ในการศึกษานี้ เราได้ใช้ SEMulator3D เพื่อตรวจสอบการรวมทางเลือก SRAM (ReRAM) สำหรับ CPU สำหรับหน่วยความจำบนชิป เราใช้แบบจำลองเสมือนจริงเพื่อทำความเข้าใจขั้นตอนกระบวนการและปัญหาเค้าโครงที่อาจเกิดขึ้นสำหรับเซลล์เมมเบรนแต่ละเซลล์ได้ดียิ่งขึ้น นอกจากนี้เรายังทำการศึกษาเพื่อตรวจสอบสถานะการตั้งค่าและการรีเซ็ตของเมมเบรนและผลกระทบของขนาดอุปกรณ์ (รูปร่างและขนาดเซลล์หน่วยความจำ) ต่อการต้านทานเวิร์ดไลน์ เราได้เน้นย้ำว่าหน่วยความจำออนบอร์ด ReRAM สามารถบูรณาการเข้ากับตรรกะขั้นสูงได้ โดยใช้เอาต์พุตไฟฟ้าของทรานซิสเตอร์ GAA pFET เพื่อตั้งค่าและรีเซ็ตเซลล์เมมเบรน ผลลัพธ์เหล่านี้ยืนยันว่า Resistive Random Access Memory (ReRAM) เป็นทางเลือกที่น่าสนใจแทนหน่วยความจำ SRAM ออนบอร์ดสำหรับแอปพลิเคชันลอจิกแบนด์วิธสูงในอนาคต

อ้างอิง

- ลานซา, มาริโอ (2014) “การทบทวนการสลับตัวต้านทานในไดอิเล็กทริกสูง: มุมมองระดับนาโนโดยใช้กล้องจุลทรรศน์แรงอะตอมนำไฟฟ้า” วัสดุเล่ม 7, ฉบับที่ 3, หน้า 2155-2182, ดอย:10.3390/ma7032155.

- N. Sedghi และคณะ “บทบาทของการเติมไนโตรเจนใน ALD Ta2O5 และอิทธิพลของมันต่อการสลับเซลล์หลายระดับใน RRAM”, มีนาคม 2017, จดหมายฟิสิกส์ประยุกต์, DOI:10.1063/1.4978033

- Y. Bai, Et Al, “การศึกษาคุณลักษณะหลายระดับสำหรับหน่วยความจำการสลับตัวต้านทานแนวตั้งแบบ 3 มิติ” รายงานทางวิทยาศาสตร์เล่มที่ 4, หมายเลขบทความ: 5780 (2014)

- เฉิน, YC, ซาร์การ์, เอส., กิ๊บส์, เจจี, หวง, วาย., ลี, เจซี, ลิน, ซีซี, และลิน, CH (2022) “หน่วยความจำต้านทานแบบฟังก์ชั่นคู่ที่มีรูปทรงนาโนเฮลิคอลสำหรับแอปพลิเคชันอาร์เรย์คานประตูพลังงานต่ำ”, วัสดุวิศวกรรมประยุกต์ของ ACS, 1(1), 252-257

- Y. Wu และคณะ “RRAM HfOx ระดับนาโนเมตร”, จดหมายอุปกรณ์ IEEE Electron, เล่ม: 34, ฉบับ: 8, สิงหาคม 2013), doi:10.1109/LED.2013.2265404

- V. Sreenivasulu และคณะ “การวิเคราะห์วงจรและการเพิ่มประสิทธิภาพของ GAA Nanowire FET สู่พลังงานต่ำและการสลับสูง”, 11 พฤศจิกายน 2021, วิทยาการคอมพิวเตอร์, doi:10.1007/s12633-022-01777-6

เบรตต์ โลว์

Brett Lowe เป็นผู้จัดการทีมกระบวนการเซมิคอนดักเตอร์และบูรณาการที่ Coventor ซึ่งเป็นบริษัท Lam Research Company เขาทำงานด้านการพัฒนาเทคโนโลยีเซมิคอนดักเตอร์มานานกว่า 35 ปี เขาเริ่มต้นอาชีพที่ Philips Semiconductors ซึ่งเขาทำงานในด้านการผลิตและการพัฒนากระบวนการในตำแหน่งวิศวกรกระบวนการในด้านการพิมพ์หินด้วยแสง การกัดแบบแห้ง และกระบวนการเปียก จากนั้นเขาใช้เวลาแปดปีที่ Zilog โดยทำงานเกี่ยวกับการพัฒนากระบวนการในหน่วย ต่อมา Brett เข้าร่วมกับ Micron Technology ซึ่งเขาทำงานในการพัฒนาและการบูรณาการกระบวนการ DRAM และ 3D NAND ที่ Coventor เขามุ่งเน้นไปที่การสนับสนุนลูกค้าของบริษัทในการสร้างแบบจำลองกระบวนการเซมิคอนดักเตอร์ 3 มิติและข้อกำหนดในการพัฒนาเทคโนโลยี

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiengineering.com/developing-reram-as-next-generation-on-chip-memory-for-machine-learning-image-processing-and-other-advanced-cpu-applications/

- :มี

- :เป็น

- :ไม่

- :ที่ไหน

- 1

- 10

- 100

- 10K

- 11

- 16

- 1M

- 2013

- 2014

- 2017

- 2021

- 2022

- 35%

- 3d

- 400

- 7

- 75

- 8

- 8k

- a

- ความสามารถ

- สามารถ

- เข้า

- ข้าม

- กระทำ

- เพิ่ม

- เพิ่มเติม

- สูง

- มีผลต่อ

- AI

- AL

- ทั้งหมด

- โพสต์ทั้งหมด

- บรรเทา

- อนุญาต

- ตาม

- ด้วย

- ทางเลือก

- an

- การวิเคราะห์

- และ

- การใช้งาน

- การใช้งาน

- ประยุกต์

- ประมาณ

- สถาปัตยกรรม

- เป็น

- พื้นที่

- แถว

- บทความ

- AS

- At

- อะตอม

- สิงหาคม

- b

- แบนด์วิดธ์

- BE

- รับ

- เริ่ม

- ดีกว่า

- ระหว่าง

- บิต

- Black

- ด้านล่าง

- สีน้ำตาล

- กำ

- แต่

- by

- ที่เรียกว่า

- CAN

- ความก้าวหน้า

- ที่เกิดจาก

- CD

- เซลล์

- เซลล์

- ศูนย์

- เปลี่ยนแปลง

- ช่อง

- ลักษณะ

- การเรียกเก็บเงิน

- รวม

- บริษัท

- บริษัท

- เมื่อเทียบกับ

- คอมพิวเตอร์

- วิทยาการคอมพิวเตอร์

- กังวล

- ตัวนำ

- ยืนยัน

- เชื่อมต่อ

- ประกอบ

- การบริโภค

- รายชื่อผู้ติดต่อ

- มี

- ความสัมพันธ์

- ได้

- ซีพียู

- สร้าง

- ที่สร้างขึ้น

- ข้าม

- ปัจจุบัน

- ขณะนี้

- ลูกค้า

- มืด

- ข้อมูล

- ความล่าช้า

- ความล่าช้า

- สาธิต

- แสดงให้เห็นถึง

- ฝาก

- ออกแบบ

- นักออกแบบ

- กำหนด

- พัฒนา

- ที่กำลังพัฒนา

- พัฒนาการ

- เครื่อง

- อุปกรณ์

- ความแตกต่าง

- ความแตกต่าง

- ต่าง

- มิติ

- มองเห็น

- แสดง

- แสดง

- DOE

- ท่อระบายน้ำ

- การวาดภาพ

- ขับรถ

- แห้ง

- ในระหว่าง

- E&T

- แต่ละ

- อย่างง่ายดาย

- ขอบ

- ผล

- XNUMX

- อิเล็กทรอนิกส์

- ที่ฝัง

- พลังงาน

- การใช้พลังงาน

- วิศวกร

- ชั้นเยี่ยม

- ประมาณการ

- อีเธอร์ (ETH)

- ตรวจสอบ

- ดำเนินการ

- การทดลอง

- การทดลอง

- FET

- สนาม

- รูป

- ที่เต็มไป

- โฟกัส

- สำหรับ

- บังคับ

- ฟอร์ม

- ที่เกิดขึ้น

- รูปแบบ

- พบ

- ราคาเริ่มต้นที่

- ฟังก์ชัน

- อนาคต

- ประตู

- เกตส์

- รุ่น

- กราฟ

- มากขึ้น

- สีเขียว

- มี

- he

- จุดสูง

- สูงกว่า

- ไฮไลต์

- ของเขา

- HTTPS

- Huang

- ร้อย

- ID

- ระบุ

- อีอีอี

- if

- ภาพ

- in

- ประกอบด้วย

- เพิ่ม

- ที่เพิ่มขึ้น

- แสดง

- เป็นรายบุคคล

- มีอิทธิพล

- ภายใน

- รวบรวม

- แบบบูรณาการ

- บูรณาการ

- เข้าไป

- สอบสวน

- ปัญหา

- ITS

- เข้าร่วม

- หวด

- ภาษา

- ต่อมา

- ชั้น

- ชั้น

- แบบ

- ชั้นนำ

- การเรียนรู้

- การออกจาก

- Lee

- ซ้าย

- กดไลก์

- ถูก จำกัด

- lin

- ตรรกะ

- ต่ำ

- เครื่อง

- เรียนรู้เครื่อง

- สำคัญ

- ผู้จัดการ

- การผลิต

- มีนาคม

- มาริโอ

- วัสดุ

- วัสดุ

- ความกว้างสูงสุด

- อาจ..

- พบ

- หน่วยความจำ

- โลหะ

- ไมครอน

- แบบ

- การสร้างแบบจำลอง

- ทันสมัย

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ย้าย

- การเคลื่อนไหว

- จำเป็นต้อง

- จำเป็น

- ถัดไป

- พฤศจิกายน

- จำนวน

- of

- OHM

- on

- ONE

- เพียง

- การดำเนินการ

- การเพิ่มประสิทธิภาพ

- or

- อื่นๆ

- เอาท์พุต

- เส้นทาง

- เส้นทาง

- ต่อ

- การปฏิบัติ

- ฟิลิปส์

- ฟิสิกส์

- เสา

- เสา

- สีชมพู

- วางไว้

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- จุด

- จุดชมวิว

- เป็นไปได้

- โพสต์

- ที่มีศักยภาพ

- อำนาจ

- ก่อนหน้านี้

- ปัญหา

- ปัญหาที่เกิดขึ้น

- กระบวนการ

- การประมวลผล

- โครงการ

- โปรแกรม

- การเขียนโปรแกรม

- แวว

- ให้

- สุ่ม

- พิสัย

- อัตราส่วน

- อ่าน

- สีแดง

- ลบออก

- รายงาน

- ต้องการ

- จำเป็นต้องใช้

- ความต้องการ

- การวิจัย

- ความต้านทาน

- คำตอบ

- ผลสอบ

- ทบทวน

- ขวา

- บทบาท

- s

- วิทยาศาสตร์

- วิทยาศาสตร์

- Section

- สารกึ่งตัวนำ

- อุปกรณ์กึ่งตัวนำ

- ชุด

- การตั้งค่า

- รูปร่าง

- น่า

- แสดง

- ด้าน

- สัญญาณ

- สำคัญ

- จำลอง

- ขนาด

- ทางออก

- แก้

- แหล่ง

- การใช้จ่าย

- ซ้อนกัน

- สถานะ

- สหรัฐอเมริกา

- ขั้นตอน

- การเก็บรักษา

- มีการศึกษา

- การศึกษา

- ศึกษา

- อย่างเช่น

- ที่สนับสนุน

- ทีม

- เทคโนโลยี

- การพัฒนาเทคโนโลยี

- กว่า

- ที่

- พื้นที่

- กราฟ

- ที่มา

- รัฐ

- ของพวกเขา

- แล้วก็

- ที่นั่น

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- นี้

- ตลอด

- ดังนั้น

- เวลา

- ครั้ง

- ระยะเวลา

- ไปยัง

- ด้านบน

- ไปทาง

- ตามธรรมเนียม

- สอง

- ชนิด

- ตามแบบฉบับ

- ภายใต้

- เข้าใจ

- น่าเสียดาย

- หน่วย

- ใช้

- มือสอง

- การใช้

- ความคุ้มค่า

- ต่างๆ

- กับ

- แนวตั้ง

- ดิ่ง

- วีดีโอ

- รายละเอียด

- เสมือน

- การสร้างภาพ

- แรงดันไฟฟ้า

- ปริมาณ

- vs

- คือ

- we

- webp

- คือ

- เมื่อ

- ในขณะที่

- ขาว

- อย่างกว้างขวาง

- จะ

- กับ

- ทำงาน

- การทำงาน

- จะ

- wu

- ปี

- ลมทะเล