หากเราดูการขยายตัวของอุตสาหกรรมเซมิคอนดักเตอร์ในช่วง 25 ปีที่ผ่านมา การนำ IP การออกแบบมาใช้ในทุกแอปพลิเคชันดูเหมือนจะเป็นหนึ่งในปัจจัยสำคัญของความสำเร็จ ด้วยเทคโนโลยีซิลิคอนมีการพัฒนาอย่างเหลือเชื่อด้วยปัจจัย x100 จาก 250 นาโนเมตรในปี 2018 เป็น 3 นาโนเมตร (หาก ไม่ใช่ 2 นาโนเมตร) ในปี 2023 เราคาดการณ์ว่าจะมีการเปลี่ยนไปใช้สถาปัตยกรรมที่ใช้ชิปเล็ตเพื่อมีบทบาทเดียวกันกับสถาปัตยกรรมที่ใช้ชิป SoC และการใช้งาน IP การออกแบบจำนวนมากในปี 2000 ในไม่ช้า

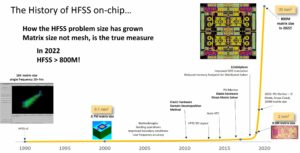

คำถามคือจะคาดการณ์กรอบเวลาการนำชิปเล็ตไปใช้อย่างแม่นยำได้อย่างไร และอะไรจะเป็นปัจจัยสำคัญในการปฏิวัติครั้งนี้ เราจะดูว่าการแพร่กระจายของทฤษฎีนวัตกรรมจะเป็นประโยชน์ในการปรับแต่งการทำนายหรือไม่ และพิจารณาว่าแอปพลิเคชันประเภทใดจะเป็นตัวขับเคลื่อน ข้อกำหนดมาตรฐานโปรโตคอลการเชื่อมต่อระหว่างชิปกับชิปช่วยให้สามารถนำไปใช้ในอุตสาหกรรมได้อย่างรวดเร็ว การขับเคลื่อนแอปพลิเคชัน เช่น IA หรือโปรเซสเซอร์แอปพลิเคชันสมาร์ทโฟนอย่างรวดเร็วดูเหมือนจะเป็นตัวเปิดใช้งานอันดับต้นๆ แต่ประสิทธิภาพของเครื่องมือ EDA หรือการบรรจุเทคโนโลยีใหม่ และการสร้าง fab โดยเฉพาะ เหนือสิ่งอื่นใด ถือเป็นกุญแจสำคัญอย่างแน่นอน

บทนำ: การเกิดขึ้นของเทคโนโลยีชิปเล็ต

ในช่วงทศวรรษปี 2010 ประโยชน์ของกฎของมัวร์เริ่มที่จะขาดหายไป กฎของมัวร์ระบุว่าความหนาแน่นของทรานซิสเตอร์เพิ่มขึ้นสองเท่าทุก ๆ สองปี ค่าใช้จ่ายในการประมวลผลจะลดลง 50% ที่สอดคล้องกัน การเปลี่ยนแปลงกฎของมัวร์เกิดจากการเพิ่มความซับซ้อนในการออกแบบวิวัฒนาการของโครงสร้างทรานซิสเตอร์จากอุปกรณ์ระนาบไปสู่ Finfets Finfet จำเป็นต้องมีรูปแบบหลายรูปแบบสำหรับการพิมพ์หินเพื่อให้ได้ขนาดอุปกรณ์ที่ต่ำกว่าโหนด 20 นาโนเมตร

ในช่วงปลายทศวรรษนี้ ความต้องการด้านคอมพิวเตอร์ได้เพิ่มสูงขึ้น ส่วนใหญ่เนื่องมาจากการขยายตัวของศูนย์ข้อมูล และเนื่องจากปริมาณของข้อมูลที่ถูกสร้างขึ้นและประมวลผล ในความเป็นจริง การนำปัญญาประดิษฐ์ (AI) มาใช้และเทคนิคต่างๆ เช่น การเรียนรู้ของเครื่อง (ML) ถูกนำมาใช้ในการประมวลผลข้อมูลที่เพิ่มมากขึ้นเรื่อยๆ และทำให้เซิร์ฟเวอร์เพิ่มความสามารถในการประมวลผลอย่างมีนัยสำคัญ เซิร์ฟเวอร์ได้เพิ่มคอร์ CPU มากขึ้น ได้รวม GPU ขนาดใหญ่ที่ใช้สำหรับ ML โดยเฉพาะ ไม่ได้ใช้สำหรับกราฟิกอีกต่อไป และได้ฝังตัวเร่งความเร็ว ASIC AI แบบกำหนดเองหรือตัวประมวลผล AI เสริมที่ใช้ FPGA การออกแบบชิป AI ในยุคแรกๆ ถูกนำมาใช้โดยใช้ SoC แบบเสาหินที่มีขนาดใหญ่กว่า ซึ่งบางอันมีขนาดถึงขีดจำกัดที่กำหนดโดยเรติเคิลประมาณ 700 มม.2.

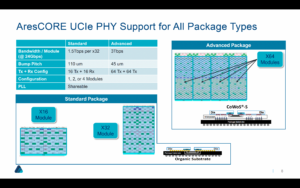

ณ จุดนี้ การแยกออกเป็น SoC ที่เล็กลงบวกกับการประมวลผลและชิปเล็ต IO ต่างๆ ดูเหมือนจะเป็นวิธีแก้ปัญหาที่ถูกต้อง ผู้ผลิตชิปหลายราย เช่น Intel, AMD หรือ Xilinx ได้เลือกตัวเลือกนี้สำหรับผลิตภัณฑ์ที่เข้าสู่การผลิต ในเอกสารไวท์เปเปอร์ที่ยอดเยี่ยมจาก The Linley Group เรื่อง “Chiplets ได้รับการนำไปใช้อย่างรวดเร็ว: ทำไมชิปขนาดใหญ่ถึงมีขนาดเล็ก” แสดงให้เห็นว่าตัวเลือกนี้นำไปสู่ต้นทุนที่ดีกว่าเมื่อเปรียบเทียบกับ SoC แบบเสาหิน เนื่องจากมีผลกระทบต่อผลผลิตที่ใหญ่กว่า ผู้ผลิตชิปเหล่านี้ได้ออกแบบชิปเล็ตที่เป็นเนื้อเดียวกัน แต่การเกิดขึ้นและการปรับใช้มาตรฐานการเชื่อมต่อระหว่างกัน เช่น Universal Chiplet Interconnect Express (UCIe) IP กำลังช่วยลดการนำชิปเล็ตที่ต่างกันมาใช้

วิวัฒนาการของมาตรฐานโปรโตคอลที่ใหม่กว่า เร็วกว่านั้นกำลังเพิ่มความเร็วขึ้น เนื่องจากอุตสาหกรรมร้องขอประสิทธิภาพที่สูงขึ้นอย่างต่อเนื่อง น่าเสียดายที่มาตรฐานต่างๆ ไม่ได้รับการซิงโครไนซ์โดยองค์กรเดียว มาตรฐาน PCIe ใหม่อาจเกิดขึ้นหนึ่งปี (หรือมากกว่า) ก่อนหรือหลังมาตรฐานโปรโตคอลอีเทอร์เน็ตใหม่ การใช้การบูรณาการที่ต่างกันช่วยให้ผู้ให้บริการซิลิคอนสามารถปรับตัวเข้ากับตลาดที่เปลี่ยนแปลงอย่างรวดเร็วโดยการเปลี่ยนการออกแบบชิปเล็ตที่เกี่ยวข้องเท่านั้น เมื่อพิจารณาถึงการออกแบบ SoC ขั้นสูงต้องใช้เงินลงทุนจำนวนมหาศาลสำหรับโหนดกระบวนการ 5 นาโนเมตร 4 นาโนเมตร หรือ 3 นาโนเมตร ผลกระทบของสถาปัตยกรรมชิปเล็ตนั้นยิ่งใหญ่มากในการขับเคลื่อนนวัตกรรมในอนาคตในพื้นที่เซมิคอนดักเตอร์

การออกแบบชิปเล็ตที่แตกต่างกันช่วยให้เราสามารถกำหนดเป้าหมายการใช้งานหรือกลุ่มตลาดที่แตกต่างกันโดยการปรับเปลี่ยนหรือเพิ่มเฉพาะชิปเล็ตที่เกี่ยวข้อง ขณะเดียวกันก็รักษาส่วนที่เหลือของระบบไว้ไม่เปลี่ยนแปลง การพัฒนาใหม่ๆ สามารถออกสู่ตลาดได้รวดเร็วยิ่งขึ้นด้วยการลงทุนที่ลดลงอย่างมาก เนื่องจากการออกแบบใหม่จะส่งผลกระทบต่อพื้นผิวบรรจุภัณฑ์ที่ใช้กักชิปเล็ตเท่านั้น ตัวอย่างเช่น ชิปประมวลผลสามารถออกแบบใหม่จาก TSMC 5nm เป็น TSMC 3nm เพื่อรวมแคช L1 ที่ใหญ่ขึ้นหรือ CPU ที่มีประสิทธิภาพสูงกว่า หรือจำนวนแกน CPU ขณะเดียวกันก็รักษาส่วนที่เหลือของระบบไว้ไม่เปลี่ยนแปลง Chiplet ที่รวม SerDes สามารถออกแบบใหม่เพื่อให้ได้อัตราที่เร็วขึ้นบนโหนดกระบวนการใหม่ที่นำเสนอแบนด์วิดท์ IO ที่มากขึ้นเพื่อการวางตำแหน่งทางการตลาดที่ดีขึ้น

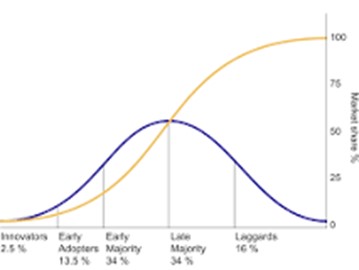

การใช้ชิปเล็ตที่ต่างกันจะช่วยให้ Time-to-Market (TTM) ดีขึ้นเมื่ออัปเดตระบบ โดยนำส่วนของระบบกลับมาใช้ใหม่โดยไม่มีการเปลี่ยนแปลงหากได้รับการออกแบบในชิปเล็ต นี่จะเป็นวิธีการลดต้นทุนเมื่อเก็บชิปเล็ตที่ใช้งานได้บางส่วนไว้บนโหนดขั้นสูงน้อยกว่า ซึ่งมีราคาถูกกว่าโหนดที่ทันสมัยที่สุด แต่คำถามหลักคือการคาดการณ์ว่าเทคโนโลยีชิปเล็ตจะสร้างส่วนสำคัญของตลาดเซมิคอนดักเตอร์เมื่อใด เราจะตรวจสอบประวัติการใช้ IP เนื่องจาก Chiplet และ IP มีความคล้ายคลึงกัน ทั้งคู่ต้องทำลายกลุ่มอาการ NIH จึงจะประสบความสำเร็จ เราจะแยกสาเหตุหลักของการนำ Chiplet มาใช้และสร้างการคาดการณ์โดยใช้ทฤษฎีนวัตกรรมและหมวดหมู่ที่กำหนด (ผู้สร้างนวัตกรรม ผู้ที่นำมาใช้ในช่วงแรก ฯลฯ ดูรูปภาพด้านล่าง)

เราจะตรวจสอบการนำ IP ของ CPU ARM มาใช้จนถึงปี 1991 ถึง 2018 และประวัติการใช้ IP จนถึงปี 1995 ถึง 2027 และตรวจสอบว่าอัตราการนำไปใช้นี้สอดคล้องกับทฤษฎีนวัตกรรมอย่างไร

เราจะอธิบายว่าทำไมการใช้ชิปเล็ตจึงได้รับการส่งเสริม โดยทบทวนเหตุผลที่เกี่ยวข้องกับเทคโนโลยีและการตลาด:

- จาก SoC ที่ใช้ IP ไปจนถึงระบบที่ใช้ Chiplet

- ความสามารถในการทำงานร่วมกันด้วยมาตรฐานโปรโตคอลที่ต้องการของ Chiplet Interconnect

- อธิบายว่าเหตุใด IP อินเทอร์เฟซระดับไฮเอนด์จึงเป็นกุญแจสำคัญในการนำ Chiplet มาใช้

- ความท้าทายที่เกี่ยวข้องกับการออกแบบที่ต้องแก้ไข

- สุดท้ายแต่ไม่ท้ายสุด การลงทุนจากโรงหล่อ

สุดท้ายนี้ เราสามารถสร้างการคาดการณ์การนำชิปเล็ตไปใช้เบื้องต้นได้ โดยอิงตามทฤษฎีนวัตกรรม ที่ต้องกล่าวถึงก็คือ อุตสาหกรรมเพิ่งเข้าสู่ระยะ "Early adopters" โดยเห็นผู้จำหน่าย IP และ Chiplet จำนวนมากที่ให้บริการ HPC และ AI

หากคุณดาวน์โหลด กระดาษสีขาวคุณจะเพลิดเพลินไปกับข้อความทั้งหมดและรูปภาพจำนวนมากซึ่งบางส่วนสร้างขึ้นเพื่องานนี้โดยเฉพาะ

By เอริค เอสตีฟ (ปริญญาเอก) นักวิเคราะห์ เจ้าของ IPnest

Alphawave สนับสนุนการสร้างเอกสารไวท์เปเปอร์นี้ แต่ความคิดเห็นและการวิเคราะห์เป็นความคิดเห็นของผู้เขียน สามารถพบได้ที่นี่:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

ยังอ่าน:

ระบบแบบแยกส่วน: การเปิดใช้งานคอมพิวเตอร์ด้วย UCIe Interconnect และการออกแบบที่ใช้ Chiplets

Interface IP ในปี 2022: การเติบโต 22% เมื่อเทียบเป็นรายปี ยังคงขับเคลื่อนด้วยข้อมูลเป็นศูนย์กลาง

แชร์โพสต์นี้ผ่าน:

- เนื้อหาที่ขับเคลื่อนด้วย SEO และการเผยแพร่ประชาสัมพันธ์ รับการขยายวันนี้

- PlatoData.Network Vertical Generative Ai เพิ่มพลังให้กับตัวเอง เข้าถึงได้ที่นี่.

- เพลโตไอสตรีม. Web3 อัจฉริยะ ขยายความรู้ เข้าถึงได้ที่นี่.

- เพลโตESG. คาร์บอน, คลีนเทค, พลังงาน, สิ่งแวดล้อม แสงอาทิตย์, การจัดการของเสีย. เข้าถึงได้ที่นี่.

- เพลโตสุขภาพ เทคโนโลยีชีวภาพและข่าวกรองการทดลองทางคลินิก เข้าถึงได้ที่นี่.

- ที่มา: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- :มี

- :เป็น

- :ไม่

- $ ขึ้น

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- เกี่ยวกับเรา

- เร่ง

- บรรลุ

- ปรับ

- ที่เพิ่ม

- เพิ่ม

- ผู้รับใช้

- การนำมาใช้

- สูง

- AI

- ข้อมูล AI

- ทั้งหมด

- การอนุญาต

- ช่วยให้

- ด้วย

- เอเอ็มดี

- ในหมู่

- จำนวน

- การวิเคราะห์

- นักวิเคราะห์

- และ

- นอกเหนือ

- ปรากฏ

- การใช้งาน

- การใช้งาน

- สถาปัตยกรรม

- เป็น

- ARM

- บทความ

- เทียม

- ปัญญาประดิษฐ์

- ปัญญาประดิษฐ์ (AI)

- AS

- ASIC

- ขอให้

- At

- ผู้เขียน

- แบนด์วิดธ์

- ตาม

- BE

- กลายเป็น

- เริ่ม

- กำลัง

- ด้านล่าง

- ประโยชน์ที่ได้รับ

- ดีกว่า

- ใหญ่

- เพิ่มขึ้น

- ทั้งสอง

- ทำลาย

- สร้าง

- แต่

- by

- แคช

- CAN

- ความจุ

- เมืองหลวง

- หมวดหมู่

- สาเหตุที่

- อย่างแน่นอน

- ความท้าทาย

- เปลี่ยนแปลง

- เปลี่ยนแปลง

- ราคาถูก

- ตรวจสอบ

- ชิป

- ชิป

- อย่างไร

- เมื่อเทียบกับ

- ประกอบ

- ความซับซ้อน

- คำนวณ

- การคำนวณ

- พิจารณา

- ตรงกัน

- ราคา

- ค่าใช้จ่าย

- ได้

- ซีพียู

- สร้าง

- ที่สร้างขึ้น

- การสร้าง

- ประเพณี

- ข้อมูล

- ทศวรรษ

- ทุ่มเท

- กำหนด

- ออกแบบ

- ได้รับการออกแบบ

- การออกแบบ

- กำหนด

- พัฒนาการ

- การพัฒนา

- อุปกรณ์

- ต่าง

- การจัดจำหน่าย

- มิติ

- สองเท่า

- ดาวน์โหลด

- ขับรถ

- คนขับรถ

- การขับขี่

- สอง

- ในระหว่าง

- ก่อน

- ก่อน

- ในช่วงเริ่มต้น

- การทำให้สบาย

- ระบบนิเวศ

- อย่างมีประสิทธิภาพ

- ที่ฝัง

- ภาวะฉุกเฉิน

- ตัวเปิดใช้งาน

- การเปิดใช้งาน

- ปลาย

- เพลิดเพลิน

- ฯลฯ

- เพิ่มขึ้นเรื่อยๆ

- ทุกๆ

- วิวัฒนาการ

- ตัวอย่าง

- ยอดเยี่ยม

- โดยเฉพาะ

- การขยายตัว

- อธิบาย

- ด่วน

- สารสกัด

- ความจริง

- ปัจจัย

- ปัจจัย

- ตก

- FAST

- เร็วขึ้น

- รูป

- สำหรับ

- พยากรณ์

- ล่วงรู้

- พบ

- FPGA

- ราคาเริ่มต้นที่

- การทำงาน

- อนาคต

- ได้รับ

- สร้าง

- ได้รับ

- ไป

- GPUs

- กราฟิก

- บัญชีกลุ่ม

- การเจริญเติบโต

- มี

- เป็นประโยชน์

- โปรดคลิกที่นี่เพื่ออ่านรายละเอียดเพิ่มเติม

- High-End

- สูงกว่า

- ประวัติ

- บ้าน

- สรุป ความน่าเชื่อถือของ Olymp Trade?

- ทำอย่างไร

- HPC

- HTTPS

- ia

- if

- ส่งผลกระทบ

- การดำเนินการ

- กำหนด

- in

- เพิ่มขึ้น

- ที่เพิ่มขึ้น

- เหลือเชื่อ

- อุตสาหกรรม

- นักวิเคราะห์ส่วนบุคคลที่หาโอกาสให้เป็นไปได้มากที่สุด

- ประดิษฐ์

- รวบรวม

- แบบบูรณาการ

- การบูรณาการ

- บูรณาการ

- อินเทล

- Intelligence

- อินเตอร์เฟซ

- เข้าไป

- การลงทุน

- IP

- IT

- jpg

- เพียงแค่

- การเก็บรักษา

- คีย์

- ที่มีขนาดใหญ่

- ชื่อสกุล

- ต่อมา

- เปิดตัว

- กฏหมาย

- นำไปสู่

- การเรียนรู้

- น้อยที่สุด

- นำ

- น้อยลง

- กดไลก์

- LIMIT

- อีกต่อไป

- ดู

- ลด

- เครื่อง

- เรียนรู้เครื่อง

- ทำ

- หลัก

- สำคัญ

- ผู้ผลิต

- หลาย

- ตลาด

- การตลาด

- มาก

- กล่าวถึง

- ลด

- ML

- เป็นเสาหิน

- ข้อมูลเพิ่มเติม

- มากที่สุด

- ส่วนใหญ่

- ย้าย

- ย้าย

- หลาย

- จำเป็นต้อง

- ความต้องการ

- ใหม่

- เทคโนโลยีใหม่ ๆ

- ใหม่

- NIH

- ไม่

- โหนด

- ตอนนี้

- จำนวน

- มากมาย

- of

- เสนอ

- การเสนอ

- on

- ONE

- เพียง

- ความคิดเห็น

- ตัวเลือกเสริม (Option)

- or

- organizacja

- ผลิตภัณฑ์อื่นๆ

- เจ้าของ

- แพ็คเกจ

- บรรจุภัณฑ์

- กระดาษ

- ส่วนหนึ่ง

- การปฏิบัติ

- ที่มีประสิทธิภาพ

- ระยะ

- phd

- PHP

- การเลือก

- ภาพ

- เพลโต

- เพลโตดาต้าอินเทลลิเจนซ์

- เพลโตดาต้า

- เล่น

- เล่น

- บวก

- จุด

- การวางตำแหน่ง

- โพสต์

- powering

- อย่างแม่นยำ

- คาดการณ์

- คำทำนาย

- ที่ต้องการ

- กระบวนการ

- การประมวลผล

- การประมวลผล

- หน่วยประมวลผล

- การผลิต

- ผลิตภัณฑ์

- โปรโตคอล

- ผู้ให้บริการ

- คำถาม

- ได้เร็วขึ้น

- อย่างรวดเร็ว

- รวดเร็ว

- คะแนน

- ราคา

- ถึง

- อ่าน

- เหตุผล

- การออกแบบ

- การออกแบบใหม่

- ที่เกี่ยวข้อง

- ตรงประเด็น

- การแจ้งเตือน

- ต้อง

- REST

- ทบทวน

- การตรวจสอบ

- การปฏิวัติ

- ขวา

- บทบาท

- เดียวกัน

- เห็น

- เห็น

- ดูเหมือนว่า

- ส่วน

- กลุ่ม

- เลือก

- สารกึ่งตัวนำ

- เซิร์ฟเวอร์

- การให้บริการ

- หลาย

- แสดง

- สำคัญ

- อย่างมีความหมาย

- ซิลิคอน

- คล้ายคลึงกัน

- เดียว

- ขนาด

- มีขนาดเล็กกว่า

- มาร์ทโฟน

- ทางออก

- แก้

- บาง

- ในไม่ช้า

- ช่องว่าง

- ข้อกำหนด

- ความเร็ว

- ผู้ให้การสนับสนุน

- มาตรฐาน

- มาตรฐาน

- ระบุ

- ติด

- ยังคง

- โครงสร้าง

- ความสำเร็จ

- ที่ประสบความสำเร็จ

- ระบบ

- ระบบ

- เป้า

- เทคนิค

- เทคโนโลยี

- เทคโนโลยี

- ข้อความ

- กว่า

- ขอบคุณ

- ที่

- พื้นที่

- ของพวกเขา

- พวกเขา

- ทฤษฎี

- ล้อยางขัดเหล่านี้ติดตั้งบนแกน XNUMX (มม.) ผลิตภัณฑ์นี้ถูกผลิตในหลายรูปทรง และหลากหลายเบอร์ความแน่นหนาของปริมาณอนุภาคขัดของมัน จะทำให้ท่านได้รับประสิทธิภาพสูงในการขัดและการใช้งานที่ยาวนาน

- นี้

- เหล่านั้น

- ตลอด

- ระยะเวลา

- ไปยัง

- เครื่องมือ

- ด้านบน

- มหึมา

- ทีเอสเอ็มซี

- สอง

- ชนิด

- น่าเสียดาย

- สากล

- การปรับปรุง

- us

- ใช้

- มือสอง

- การใช้

- ต่างๆ

- ผู้ขาย

- ผ่านทาง

- คือ

- ทาง..

- we

- คือ

- อะไร

- เมื่อ

- ในขณะที่

- ขาว

- กระดาษสีขาว

- ทำไม

- จะ

- กับ

- งาน

- จะ

- ปี

- ปี

- ผล

- เธอ

- ลมทะเล