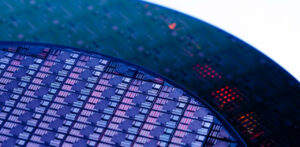

Banias Labs är ett halvledarföretag som utvecklar infrastrukturlösningar för nästa generations kommunikation. Dess målmarknad är marknaden för högpresterande datorinfrastruktur inklusive hyperskala datacenter, nätverk, AI, optisk modul och Ethernet-switch SoCs för framväxande högpresterande datordesigner. Dessa SoC:er kräver höghastighets-Ethernet-designer och lösningar med låg latens för att ge ökad systemprestanda och accelerera time-to-market. Företaget har utvecklat en optisk DSP SoC på 5nm processteknologi för att möta kraven på denna marknad.

![]()

En optisk DSP SoC är en specialiserad typ av system-on-chip (SoC) designad för användning i höghastighets optiska kommunikationssystem. Utöver DSP, inkluderar den optiska DSP SoC vanligtvis höghastighetsgränssnitt IP-block, såsom Ethernet PHY IP, PCIe IP och DDR minneskontroller. Dessa typer av SoC möjliggör höghastighetsdataöverföringar med låga latenser för signalbehandling i realtid. De är också designade för att minimera strömförbrukningen, vilket gör dem idealiska för applikationer som kräver effektiv drift med minskade termiska problem. Med fördelarna kommer också utmaningar. De specialiserade kraven på optiska kommunikationssystem gör att designa en optisk DSP SoC mer utmanande än att designa en vanlig SoC.

Implementeringsutmaningar

Utmaningarna kretsar kring komplexiteten i designen, de snäva kraft- och prestandakraven och behovet av att uppfylla olika industristandarder. Integreringen av flera IP-block inklusive DSP-processorn, Ethernet PHY IP och andra anpassade block kräver noggrann design och validering. Ytterligare höghastighetsgränssnitt som PCIe och DDR ökar designens komplexitet ytterligare. Höghastighetsgränssnitten och flera IP-block i systemet kan skapa signalförvrängning, överhörning och elektromagnetisk störning, vilket kan påverka systemets prestanda och tillförlitlighet. Analys och optimering av signal- och effektintegritet måste utföras tidigt i designcykeln för att säkerställa att systemet kan uppfylla sina krav på prestanda och tillförlitlighet. Slutligen kan det vara svårt att uppfylla kraven på tid till marknaden. Marknaden för högpresterande datorinfrastruktur utvecklas snabbt, och SoC-utvecklingsteam måste leverera sina konstruktioner snabbt för att ligga före konkurrenterna.

Att komma till First Pass Silicon Success

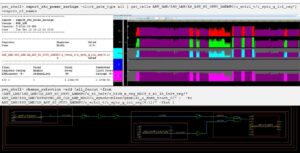

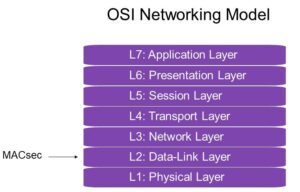

Att övervinna de ovan nämnda utmaningarna kräver ett övergripande tillvägagångssätt. En av de kritiska komponenterna i högpresterande lösningar med låg latens är Ethernet PHY IP. Ethernet PHY IP ansvarar för det fysiska lagrets gränssnitt mellan SoC och Ethernet-nätverket. IP:n måste stödja höghastighets Ethernet-gränssnitt, inklusive 10G, 25G, 40G, 50G, 100G, 200G, 400G och 800G, och ge låg latens och låg strömförbrukning. Dessutom måste IP:n stödja olika standarder, inklusive IEEE 802.3 och Ethernet Alliance. En annan viktig komponent är EDA-designsviten. EDA-designsviten måste tillhandahålla en heltäckande lösning för att designa och verifiera SoC, inklusive effektoptimering, prestandaanalys, områdesoptimering och avkastningsanalys. I den mån EDA-designsviten innehåller avancerade funktioner, såsom artificiell intelligens (AI) och maskininlärning (ML), desto bättre för ökad produktivitet och minskad time-to-market.

Synopsys accelererar First Pass Silicon Success

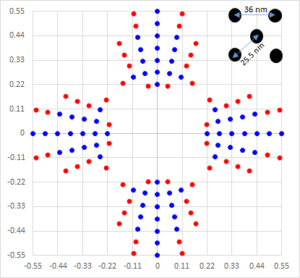

Synopsys erbjuder lösningar som tar itu med de unika utmaningarna med att utveckla SoCs för marknaden för högpresterande datorinfrastruktur. Företaget tillhandahåller en omfattande IP-lösning som inkluderar en genomförbarhetsstudie för routing, riktlinjer för förpackningssubstrat, modeller för signal- och strömintegritet och noggrann överhörningsanalys. Detta är absolut nödvändigt för att ta itu med utmaningarna med signal- och effektintegritet när man utvecklar en optisk DSP SoC. Synopsys 112G Ethernet PHY IP erbjuder låg latens, flexibla räckviddslängder och mognad på 5nm processteknik, vilket gör den till en idealisk lösning för hyperskala datacenter, nätverk, AI, optisk modul och Ethernet-switch SoCs. Dessutom erbjuder Synopsys en EDA Design Suite som levererar högkvalitativa resultat med optimerad kraft, prestanda, yta och avkastning. Synopsys AI-drivna EDA Design Suite tillhandahåller lösningar för att öka systemets prestanda och accelerera time-to-market, vilket gör den till en viktig komponent i en framgångsrik lösning för marknaden för högpresterande datorinfrastruktur.

Sammanfattning

Synopsys tillhandahåller högpresterande lösningar med låg latens som påskyndar utvecklingen av avancerade Ethernet-switch och nätverks-SoCs. För att lära dig mer om Synopsys omfattande IP-lösningar, deras omfattande EDA Design Suite och deras AI-Enhanced EDA Suite, besök följande sidor.

Synopsys omfattande IP-lösningar

Synopsys AI-drivna EDA Design Suite

Läs också:

Multi-Die Systems: Den största störningen i datoranvändning på flera år

Ta risken med att utveckla din egen RISC-V-processor med snabb, arkitekturdriven PPA-optimering

Matar den växande hungern efter bandbredd med High-Speed Ethernet

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- Platoblockchain. Web3 Metaverse Intelligence. Kunskap förstärkt. Tillgång här.

- Minting the Future med Adryenn Ashley. Tillgång här.

- Källa: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- : har

- :är

- a

- Om oss

- ovan

- accelerera

- accelererar

- Dessutom

- Annat

- Dessutom

- adress

- avancerat

- fördelar

- framåt

- AI

- Alliance

- också

- an

- analys

- och

- Annan

- tillämpningar

- tillvägagångssätt

- ÄR

- OMRÅDE

- runt

- konstgjord

- artificiell intelligens

- Konstgjord intelligens (AI)

- AS

- At

- Bandbredd

- BE

- Bättre

- mellan

- störst

- Block

- lyft

- KAN

- noggrann

- Centrum

- utmaningar

- utmanande

- komma

- Kommunikation

- Trygghet i vårdförloppet

- företag

- konkurrens

- Komplexiteten

- komponent

- komponenter

- omfattande

- databehandling

- konsumtion

- skapa

- kritisk

- beställnings

- cykel

- datum

- Data Center

- leverera

- levererar

- Designa

- utformade

- design

- mönster

- utvecklade

- utveckla

- Utveckling

- utvecklar

- Störningar

- Tidig

- effektiv

- smärgel

- möjliggöra

- förbättrad

- säkerställa

- väsentlig

- utvecklas

- inför

- SNABB

- Funktioner

- Slutligen

- Förnamn

- flexibel

- efter

- För

- från

- ytterligare

- Odling

- riktlinjer

- högpresterande

- hög kvalitet

- html

- HTTPS

- hunger

- idealisk

- IEEE

- bild

- Inverkan

- nödvändigt

- med Esport

- in

- innefattar

- Inklusive

- ökat

- industrin

- industristandarder

- Infrastruktur

- integrering

- integritet

- Intelligens

- Gränssnitt

- gränssnitt

- IP

- problem

- IT

- DESS

- Labs

- Latens

- lager

- LÄRA SIG

- inlärning

- Låg

- Maskinen

- maskininlärning

- göra

- Framställning

- marknad

- förfall

- max-bredd

- Möt

- möte

- Minne

- nämnts

- ML

- modeller

- modul

- mer

- multipel

- Behöver

- nät

- nätverk

- nästa generation

- of

- Erbjudanden

- on

- ONE

- drift

- optimering

- optimerad

- Övriga

- egen

- förpackning

- passera

- prestanda

- fysisk

- plato

- Platon Data Intelligence

- PlatonData

- Inlägg

- kraft

- process

- bearbetning

- Processorn

- produktivitet

- ge

- ger

- snabbt

- snabbt

- nå

- Läsa

- realtid

- Minskad

- regelbunden

- tillförlitlighet

- kräver

- Krav

- Kräver

- ansvarig

- Resultat

- Risk

- halvledare

- Signal

- Kisel

- lösning

- Lösningar

- specialiserad

- standarder

- bo

- Läsa på

- framgång

- framgångsrik

- sådana

- svit

- stödja

- Växla

- system

- System

- Målet

- lag

- Teknologi

- än

- den där

- Smakämnen

- deras

- Dem

- termisk

- Dessa

- de

- detta

- till

- alltför

- överföringar

- typer

- typiskt

- unika

- användning

- godkännande

- olika

- verifiera

- via

- Besök

- som

- med

- Avkastning

- Din

- zephyrnet