Att förhindra spridning av systematiska defekter i dagens halvledardesign-till-tillverkningsprocess kräver många validerings-, analys- och optimeringssteg. Verktyg som är involverade i denna process kan inkludera designregelkontroll (DRC), verifiering av optisk närhetskorrigering (OPC), maskskrivning och mätning/inspektion av waferutskrift (för att mäta processen), mätning/inspektion för waferutskrift och fysisk felanalys för att bekräfta fel diagnos. Utbytet av information och samoptimering mellan dessa steg är en komplex process, med många feed-forward- och feedback-loopar. Kommunikationen hämmas ofta av "väggar" mellan olika delar av processtekniken, vilket bromsar innovationen. Vid SPIE-konferensen nyligen presenterade Siemens EDA ett huvudtal som föreslog en rad metoder för att bryta ner dessa väggar för att förbättra chipdesignen till tillverkningsprocessen. Läs vidare och se hur Siemens siktar på att bryta innovationshinder genom att utöka samoptimeringen av designteknologi.

Om Keynote

SPIE är det internationella samhället för optik och fotonik. Organisationen går tillbaka till 1955 och dess konferens har blivit ett ledande evenemang för avancerad design och tillverkningsämnen. Vid årets evenemang presenterade Siemens keynoten som är ämnet för detta inlägg. Det var många bidragsgivare till presentationen, inklusive Le Hong, Fan Jiang, Yuansheng Ma, Srividya Jayaram, Joe Kwan, Siemens EDA (USA); Doohwan Kwak, Siemens EDA (Republiken Korea); Sankaranarayanan Paninjath Ayyappan, Siemens EDA (Indien). Titeln på föredraget var Utöka samoptimering av designteknik från tekniklansering till HVM.

Föredraget var en del av en session om design technology co-optimization (DTCO). Det här konceptet är inte nytt, men Siemens tittade på dess tillämpning över ett bredare omfång av processen, från design till högvolymtillverkning (HVM). De idéer och resultat som presenteras har betydande implikationer. Låt oss ta en närmare titt.

Vad som presenterades

Först presenterades en titt på det aktuella tillståndet för DTCO-användning över viktiga delar av ekosystemet. Ur ett designperspektiv har många avancerade fabellösa företag ett DFM-team som ser gränserna för ett mönsterbaserat tillvägagångssätt. Vad som verkligen behövs är ny teknik för att underlätta inlärning utan gjuteriberoende.

Gjuterierna använder brute-force mönsterbaserade metoder för maskininlärning, som är kostsamma men inte helt effektiva. De söker också effektiv informationsutvinning av den massiva tillverkningsdata de skapar. Utrustningsleverantörer och EDA-leverantörer har arbetat närmare varandra och kommer med effektivare lösningar för maskininlärning.

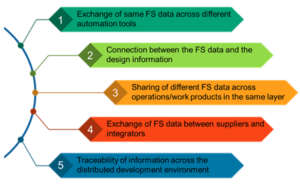

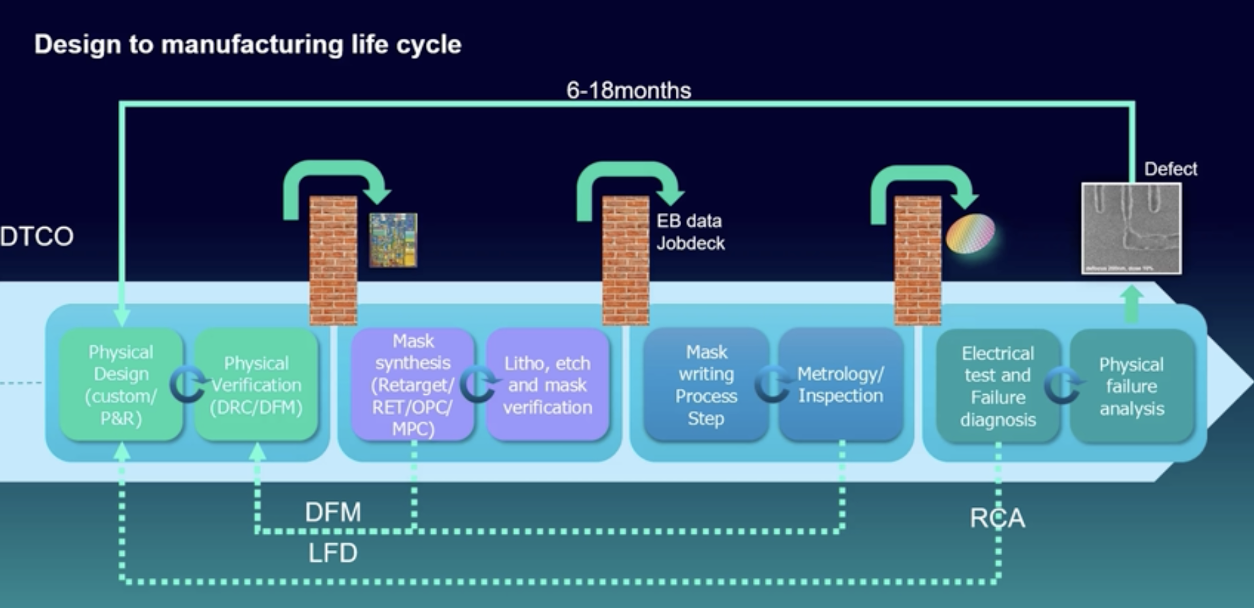

Med ett steg tillbaka påpekades det att det finns väggar mellan design- och tillverkningsfasen av processen. Fabless företag skapar designen, utför DRC och design for manufacturing (DFM), sedan kastar de det över väggen till OPC/RET-teamet inom gjuteriet eller IDM. Designen får uppgifter som OPC och verifiering gjorda och sedan slängs data över en annan vägg för maskskrivning och mätning/inspektion. Den sista väggen är för tillverkning. Här kommer eltest och felanalys att göras. När en grundorsak till misslyckande hittas har 6-18 månader gått. Det är en väldigt lång feedbackloop. Grafiken överst i det här inlägget visar denna process.

DTCO försöker bryta ner murarna, men de tillgängliga metoderna är ofullständiga. Traditionell DTCO startar mycket tidigt i processutvecklingen. Med utgångspunkt från ett skalningsbehov definieras en standardcell, och syntes, plats och rutt utförs för att komma fram till grundläggande mönster och mäta prestanda och kraft. SRAM-avkastning görs också och att data loopar tillbaka till standardcelldesignen.

Det som presenterades på SPIEs keynote var ett sätt att utöka detta samoptimeringskoncept till hela processen från design till tillverkning. Tillvägagångssättet innebär att möjliggöra ett enklare informationsflöde från design hela vägen till slutprocessen och fysisk analys genom att skapa en informationskanal.

Även om detta låter enkelt, så är det inte det. Många utmaningar diskuterades med konkreta tillvägagångssätt för att mildra problemen. Till exempel kan tidiga design skapas med syntetiska layoutgeneratorer för att hjälpa till att kalibrera processen till verkliga designproblem när processen utvecklas. Detta kan lindra många av de överraskningar som för närvarande möter med tidiga tapeouts.

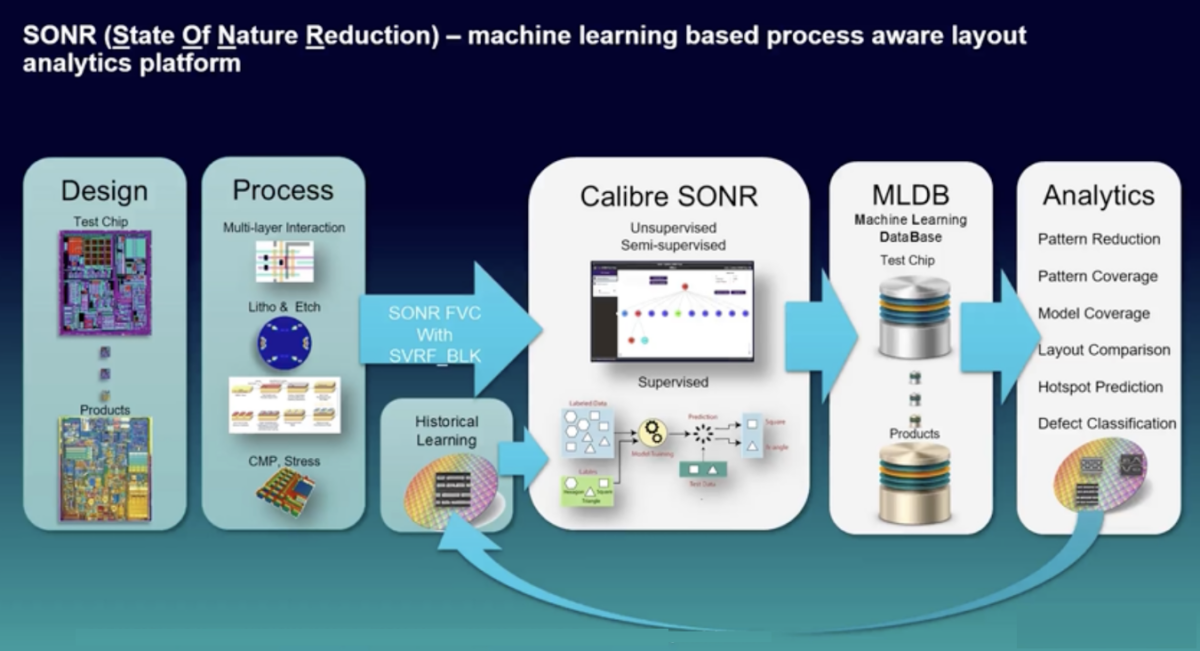

Att hantera enorma datavolymer är en annan utmaning. Genom att använda nya sofistikerade kompressionstekniker är en 30X förbättring möjlig. Detta förbättrar datahanteringen och analysuppgifterna en hel del. Ett koncept som kallas förklarlig AI kan hjälpa till att hitta bakomliggande orsaker till problem mycket snabbare. Möjligheten att träna om AI-modeller senare i tillverkningsprocessen utan att ogiltigförklara tidigare resultat är ett annat förbättringsområde. Även inom dataanalysområdet finns tekniker för att hantera "obalanserad data". Till exempel kan det finnas en hot spot i 100,000,000 XNUMX XNUMX mönster.

Att sätta ihop allt detta kan skapa ett mycket mer effektivt designflöde från slut till ände, som visas i figuren nedan.

Att lära sig mer

Effekten av de tillvägagångssätt som beskrivs i denna huvudpresentation är betydande. Du kan se presentationen och få tillgång till en vitbok om processen här. Det finns mycket användbar information att hämta. Och det är så Siemens siktar på att bryta innovationsbarriärer genom att utöka samoptimeringen av designteknologi.

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- Källa: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- : har

- :är

- :inte

- $UPP

- 000

- 100

- 2023

- a

- förmåga

- tillgång

- tvärs

- adress

- avancerat

- AI

- AI-modeller

- Syftet

- Alla

- lindra

- också

- an

- analys

- och

- Annan

- Ansökan

- tillvägagångssätt

- tillvägagångssätt

- ÄR

- OMRÅDE

- AS

- At

- Försök

- tillgänglig

- tillbaka

- barriärer

- grundläggande

- BE

- blir

- varit

- nedan

- mellan

- Bit

- Ha sönder

- bredare

- men

- by

- kallas

- KAN

- Orsak

- Orsakerna

- cellen

- utmanar

- utmaningar

- Kanal

- kontroll

- chip

- närmare

- CO

- komma

- kommande

- Kommunikation

- Företag

- fullständigt

- komplex

- begrepp

- betong

- Konferens

- Bekräfta

- contributors

- kostsam

- skapa

- skapas

- Skapa

- Aktuella

- Nuvarande tillstånd

- För närvarande

- datum

- dataanalys

- Datum

- behandla

- definierade

- beroende

- Designa

- mönster

- detaljer

- utvecklade

- Utveckling

- diagnos

- diskuteras

- gjort

- ner

- drc

- Tidigare

- Tidig

- lättare

- ekosystemet

- Effektiv

- effektiv

- möjliggör

- början till slut

- Hela

- Utrustning

- händelse

- exempel

- utbyta

- förlänga

- sträcker

- inför

- främja

- Misslyckande

- fläkt

- snabbare

- återkoppling

- Figur

- slutlig

- hitta

- flöda

- För

- hittade

- Gjuteri

- från

- vunnits

- mätare

- generatorer

- grafisk

- Arbetsmiljö

- Har

- hjälpa

- här.

- Hong

- HET

- Hur ser din drömresa ut

- HTTPS

- idéer

- Inverkan

- implikationer

- förbättra

- förbättring

- förbättrar

- in

- innefattar

- Inklusive

- indien

- informationen

- Innovation

- Internationell

- involverade

- innebär

- problem

- IT

- DESS

- joe

- Nyckel

- Keynote

- korea

- senare

- lansera

- Layout

- LÄRA SIG

- inlärning

- gränser

- Lång

- se

- såg

- Lot

- Maskinen

- maskininlärning

- Produktion

- många

- mask

- massiv

- max-bredd

- Maj..

- mäta

- metoder

- Gruvdrift

- Mildra

- modeller

- månader

- mer

- mer effektiv

- mycket

- Behöver

- behövs

- Nya

- of

- Ofta

- on

- ONE

- optik

- Optik och fotonik

- optimering

- or

- organisation

- ut

- skisse

- över

- Papper

- del

- reservdelar till din klassiker

- Godkänd

- mönster

- utföra

- prestanda

- utfört

- perspektiv

- fysisk

- Plats

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- möjlig

- Inlägg

- kraft

- Premier

- presentation

- presenteras

- tryckning

- problem

- process

- förökning

- föreslagen

- ganska

- Läsa

- verklig

- verkligen

- senaste

- Republiken

- Kräver

- Resultat

- rot

- Rutt

- Regel

- skalning

- omfattning

- se

- se

- söker

- halvledare

- Serier

- session

- visas

- siemens

- signifikant

- saktar

- Samhället

- Lösningar

- sofistikerade

- Spot

- standard

- Starta

- startar

- Ange

- Stater

- Steg

- väsentlig

- sådana

- överraskningar

- syntes

- syntetisk

- Ta

- Diskussion

- uppgifter

- grupp

- tekniker

- Teknologi

- testa

- den där

- Smakämnen

- sedan

- Där.

- Dessa

- de

- detta

- tid

- Titel

- till

- dagens

- tillsammans

- verktyg

- topp

- ämne

- ämnen

- kasta

- kastade

- traditionell

- United

- USA

- Användning

- användbar information

- med hjälp av

- godkännande

- olika

- försäljare

- Verifiering

- mycket

- via

- volymer

- Vägg

- var

- Sätt..

- były

- Vad

- Vad är

- som

- vit

- vitt papper

- kommer

- med

- inom

- utan

- arbetssätt

- skrivning

- Avkastning

- vilket gav

- dig

- zephyrnet