Under åren har DRC-verktyg gjort ett beundransvärt jobb med att hålla jämna steg med den enorma tillväxten av IC-designstorlek. Ändå kör DRC för sign-off på den fullständiga designen med hjälp av gjuteriregeldäck som tar många timmar att slutföra. Dessa långa körtider är acceptabla för slutlig avregistrering, men det finns många situationer där DRC-resultat behövs snabbt när små ändringar görs i designen för att åtgärda problem i sena skeden. Siemens EDA har i samarbete med MaxLinear skrivit en vitbok som visar hur Caliber RealTime Digital in-design DRC kan ge DRC-resultat snabbt när små förändringar har gjorts i designen. Snabbare DRC-omställning för lokaliserade ändringar kan påskynda iterativa felkorrigeringar som ofta behövs för att nå tapeout.

I vitboken med titeln "MaxLinear and Caliber RealTime Digital: Faster signoff DRC convergence plus design optimization for manufacturability" talar MaxLinear och Siemens om omständigheterna där möjligheten att köra DRC på en liten region av en design med hela gjuteriregeldäcket kan spara många timmar och smärtsamma långsamma iterationer.

Moderna P&R-verktyg gör ett utmärkt jobb med att producera DRC korrekt layout. Det finns dock alltid fall där källorna till kränkningar är mer komplexa och missas under P&R. Dessa kräver vanligtvis en manuell fix med hänsyn till komplexa designregler. Under dessa manuella korrigeringar finns det också sannolikhet att nya fel kan introduceras. Siemens presenterar information från MaxLinear i vitboken som belyser hur Caliber RealTime Digital samverkar med deras P&R-verktyg gör att de snabbt kan implementera och validera manuella korrigeringar. Alternativet är att utföra en fullständig DRC-körning bara för att se om ändringar i ett litet område är korrekta.

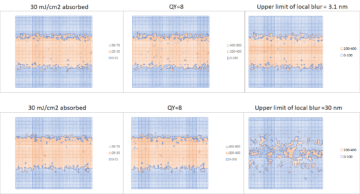

MaxLinear gör chips med analoga och digitala block. De analoga blocken kräver färre metallskikt, så för att minska tillverkningskostnaderna försöker de minska routingskikten i den fullständiga designen. Detta skapar problem med routingdensitet, som ofta står i konflikt med att upprätthålla en hög DFM-rankning. Single-cut vias använder minst utrymme men bidrar till en låg DFM-rankning. När pressen kommer att knuffa kan MaxLinear-designers manuellt växla mellan typer för att hantera routbarhet kontra DFM-avvägningar. Men dessa måste följas upp med ett omfattande DRC för att kontrollera saker som kränkningar med flera mönster. Caliber RealTime Digital låter designers byta mellan typer och sedan snabbt se om några DRC-fel finns.

Vias är inte det enda problemet som kan leda till DRC-problem som kräver tid och ansträngning att lösa. Vitboken beskriver flera situationer där manuellt arbete krävs och det enda sättet att slutligen lösa dessa problem är att få en ren DRC-körning. En av dessa situationer som inträffar sent i processen är när re-tapeout (RTO) kontroller behövs för att säkerställa att ECOs är kompatibla med befintliga masker. RTO-reglerna är till sin natur mer restriktiva än de ursprungliga DRC-reglerna.

Vitboken berör också elektromigreringsproblem som kan orsakas av användning av olämpliga vias. Även här var Caliber ReatTime Digital avgörande för MaxLinear för att implementera DRC korrekt via ersättning. Sammantaget finns det många omständigheter som kräver DRC-kontroller efter att små ändringar har gjorts för att rätta till funktions- eller tillverkningsproblem i en design. Att ha förmågan att få omedelbara resultat, istället för att vänta på en dag eller längre tid på full DRC-körning, kan raka dagar eller veckor bort från ett projekt. Det är inte bra att hitta överraskningar efter ett stort DRC-lopp. Siemens Calibre RealTime Digital-gränssnitt till P&R-verktyg verkar vara en idealisk passform för detta. Denna Siemens vitbok finns på Siemens EDA:s webbplats.

Dela det här inlägget via:

Källa: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/

- Alla

- OMRÅDE

- artiklar

- orsakas

- Kontroller

- Pommes frites

- konflikt

- innehåll

- dag

- behandla

- Designa

- digital

- Slutligen

- passa

- Fast

- Gjuteri

- full

- god

- Tillväxt

- här.

- Hög

- Hur ser din drömresa ut

- HTTPS

- stor

- informationen

- problem

- Jobb

- hålla

- leda

- Lång

- Produktion

- Masker

- metall

- Papper

- projektet

- minska

- Resultat

- regler

- Körning

- siemens

- Storlek

- Small

- So

- Utrymme

- fart

- Etapp

- Växla

- miniatyr

- tid

- Kontra

- Webbplats

- vitt papper

- Arbete

- år