Om vi tittar på halvledarindustrins expansion under de senaste 25 åren, verkar införandet av design-IP i varje applikation vara en av de viktigaste framgångsfaktorerna, med kiselteknologin otrolig utveckling med en x100-faktor, från 250nm 2018 till 3nm (om inte 2nm) 2023. Vi förutser att övergången till chipletbaserad arkitektur snart kommer att spela samma roll som SoC-chipbaserad arkitektur och massiv användning av design-IP har spelat på 2000-talet.

Frågan är hur man exakt kan förutsäga tidsramen för adoption av chiplet och vad som kommer att vara nyckelfaktorerna för denna revolution. Vi kommer att se om spridning av innovationsteori kan vara till hjälp för att finjustera en förutsägelse, avgöra vilken typ av tillämpning som kommer att vara drivkraften. Chip-to-chip interconnect-protokollstandardspecifikationer som tillåter snabb industrianpassning, driver applikationer som IA eller smartphone-applikationsprocessor verkar snabbt vara den bästa möjliggöraren, men EDA-verktygens effektivitet eller paketering av ny teknik och dedikerad fab-skapande, bland annat, är verkligen nyckeln.

Introduktion: framväxten av chiplet-teknik

Under 2010-decenniet började fördelarna med Moores lag falla isär. Moores lag angav att transistortätheten fördubblades vartannat år, kostnaden för beräkning skulle krympa med motsvarande 50%. Förändringen i Moores lag beror på ökad designkomplexitet utvecklingen av transistorstrukturen från plana enheter till Finfets. Finfets behöver flera mönster för litografi för att uppnå enhetsdimensioner till noder under 20 nm.

I slutet av detta decennium har datorbehoven exploderat, mestadels på grund av spridningen av datacenter och på grund av mängden data som genereras och bearbetas. Faktum är att antagandet av artificiell intelligens (AI) och tekniker som Machine Learning (ML) nu används för att bearbeta ständigt ökande data och har lett till att servrar avsevärt har ökat sin beräkningskapacitet. Servrar har lagt till många fler CPU-kärnor, har integrerat större GPU:er som används exklusivt för ML, används inte längre för grafik och har inbäddade anpassade ASIC AI-acceleratorer eller kompletterande, FPGA-baserad AI-behandling. Tidiga AI-chipdesigner implementerades med hjälp av större monolitiska SoC:er, några av dem nådde storleksgränsen som påtvingats av hårkorset, cirka 700 mm2.

Vid denna tidpunkt verkar uppdelning till en mindre SoC plus olika dator- och IO-chiplets vara den rätta lösningen. Flera chiptillverkare, som Intel, AMD eller Xilinx, har valt detta alternativ för produkter som går i produktion. I den utmärkta vitboken från The Linley Group, "Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small", visades det att detta alternativ leder till bättre kostnader jämfört med monolitiska SoCs, på grund av avkastningseffekten av större. Dessa chiptillverkare har designat homogena chiplets, men uppkomsten och antagandet av sammankopplingsstandarder som Universal Chiplet Interconnect Express (UCIe) IP underlättar införandet av heterogena chiplets.

Utvecklingen av de nyare, snabbare, protokollstandarderna tar fart när branschen fortsätter att begära högre prestanda. Tyvärr är de olika standarderna inte synkroniserade av en enda organisation. Nya PCIe-standarder kan komma ett år (eller mer) tidigare eller senare än den nya Ethernet-protokollstandarden. Genom att använda heterogen integration kan kiselleverantörer anpassa sig till den snabbt föränderliga marknaden genom att endast ändra designen på den relevanta chipleten. Med tanke på att avancerad SoC-designtillverkning kräver massiva investeringar för 5nm, 4nm eller 3nm processnoder, är effekten av chiplet-arkitekturer enorm för att driva framtida innovation i halvledarutrymmet.

Heterogen chipletdesign gör att vi kan rikta in oss på olika applikationer eller marknadssegment genom att modifiera eller lägga till bara relevanta chiplets samtidigt som resten av systemet hålls oförändrat. Nya utvecklingar skulle kunna lanseras snabbare på marknaden, med betydligt lägre investeringar, eftersom omdesign endast kommer att påverka paketets substrat som används för att hysa chipletarna. Till exempel kan beräkningschiplet designas om från TSMC 5nm till TSMC 3nm för att integrera större L1-cache eller högre presterande CPU eller antal CPU-kärnor, samtidigt som resten av systemet hålls oförändrat. Chipletintegrerande SerDes kan designas om för snabbare hastigheter på nya processnoder som erbjuder mer IO-bandbredd för bättre marknadspositionering.

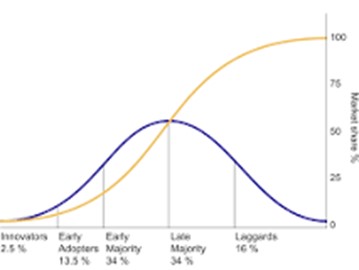

Att använda heterogena chiplet kommer att erbjuda bättre Time-to-Market (TTM) vid uppdatering av systemet, återanvändning av den del av systemet utan förändring om den är designad i chiplet. Detta kommer också att vara ett sätt att minimera kostnaden när du håller en funktionell chiplet på mindre avancerade noder, billigare än de mest avancerade. Men huvudfrågan är att förutse när chiplet-tekniken kommer att skapa ett betydande segment av halvledarmarknaden? Vi kommer att granska IP-adoptionshistoriken eftersom chiplet och IP är lika, båda måste bryta NIH-syndromet för att bli framgångsrika. Vi kommer att extrahera de huvudsakliga orsakerna till chipletadoption och bygga en prognos, med hjälp av innovationsteorin och den definierade kategorin (Innovators, Early Adopters, etc. se figur nedan).

Vi kommer att granska ARM CPU IP-adoption till och med 1991 till 2018 och IP-adoption historik till och med 1995 till 2027, och kontrollera hur denna adoptionsfrekvens håller sig med innovationsteorin.

Vi kommer att förklara varför användningen av chiplet kommer att öka, genom att se över tekniken och marknadsföringsrelaterade skäl:

- Från IP-baserat SoC till chipletbaserat system

- Interoperabilitet, tack vare chiplet interconnect föredragen protokollstandard

- Förklara varför avancerad gränssnitts-IP är nyckeln för att använda chiplet

- Designrelaterade utmaningar att lösa.

- Sist men inte minst, investeringar gjorda av gjuteriet

Slutligen kan vi bygga en preliminär prognos för adoption av chiplet, baserad på innovationsteori. Bara för att nämna, branschen har precis gått in i "Early adopters"-fasen, och såg många IP- och chipletleverantörer som serverar HPC och AI.

Om du laddar ner vitt papper, kommer du att njuta av all text och många bilder, några av dem är skapade exklusivt för detta arbete.

By Erik Esteve (PhD.) Analytiker, ägare IPnest

Alphawave sponsrade skapandet av denna vitbok, men åsikterna och analysen är författarens. Artikeln hittar du här:

https://awavesemi.com/resource/will-chiplet-adoption-to-mimic-ip-adoption/

Läs också:

Disaggregerade system: Möjliggör datoranvändning med UCIe Interconnect och Chiplets-baserad design

Gränssnitts-IP 2022: 22 % tillväxt på årsbasis, fortfarande datacentrerad

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- Källa: https://semiwiki.com/chiplet/339927-will-chiplet-adoption-mimic-ip-adoption/

- : har

- :är

- :inte

- $UPP

- 1

- 1995

- 200

- 2018

- 2022

- 2023

- 25

- a

- Om Oss

- acceleratorer

- Uppnå

- anpassa

- lagt till

- tillsats

- adopterare

- Antagande

- avancerat

- AI

- AI-data

- Alla

- tillåta

- tillåter

- också

- AMD

- bland

- mängd

- analys

- analytiker

- och

- isär

- visas

- Ansökan

- tillämpningar

- arkitektur

- ÄR

- ARM

- Artikeln

- konstgjord

- artificiell intelligens

- Konstgjord intelligens (AI)

- AS

- ASIC

- be

- At

- Författaren

- Bandbredd

- baserat

- BE

- blir

- började

- Där vi får lov att vara utan att konstant prestera,

- nedan

- Fördelarna

- Bättre

- Stor

- ökat

- båda

- Ha sönder

- SLUTRESULTAT

- men

- by

- cache

- KAN

- Kapacitet

- kapital

- Kategori

- Orsakerna

- säkerligen

- utmaningar

- byta

- byte

- billigare

- ta

- chip

- Pommes frites

- komma

- jämfört

- komplementär

- Komplexiteten

- Compute

- databehandling

- med tanke på

- Motsvarande

- Pris

- Kostar

- kunde

- CPU

- skapa

- skapas

- skapande

- beställnings

- datum

- årtionde

- dedicerad

- definierade

- densitet

- Designa

- utformade

- mönster

- Bestämma

- Utveckling

- utvecklingen

- enheter

- olika

- Diffusion

- dimensioner

- fördubblats

- ladda ner

- driv

- chaufför

- drivande

- grund

- under

- Tidigare

- Tidig

- tidiga adoptörer

- lätta

- ekosystemet

- effektivitet

- inbäddade

- uppkomst

- möjliggörare

- möjliggör

- änden

- njuta

- etc

- ständigt ökande

- Varje

- Utvecklingen

- exempel

- utmärkt

- uteslutande

- expansionen

- Förklara

- uttrycker

- extrahera

- Faktum

- faktor

- faktorer

- Höst

- SNABB

- snabbare

- Figur

- För

- Prognos

- förutse

- hittade

- FPGA

- från

- funktionella

- framtida

- Få

- genereras

- få

- kommer

- GPUs

- grafik

- Grupp

- Tillväxt

- Har

- hjälp

- här.

- High-End

- högre

- historia

- Huset

- Hur ser din drömresa ut

- How To

- HPC

- HTTPS

- ia

- if

- Inverkan

- genomföras

- ålagts

- in

- ökat

- ökande

- otroligt

- industrin

- Innovation

- innovatörer

- integrera

- integrerade

- Integrera

- integrering

- Intel

- Intelligens

- Gränssnitt

- in

- investering

- IP

- IT

- jpg

- bara

- hålla

- Nyckel

- större

- Efternamn

- senare

- lanserades

- Lag

- Leads

- inlärning

- t minst

- Led

- mindre

- tycka om

- BEGRÄNSA

- längre

- se

- lägre

- Maskinen

- maskininlärning

- gjord

- Huvudsida

- större

- Beslutsfattare

- många

- marknad

- Marknadsföring

- massiv

- nämna

- minimera

- ML

- Monolitisk

- mer

- mest

- för det mesta

- flytta

- rörd

- multipel

- Behöver

- behov

- Nya

- Ny teknik

- nyare

- NIH

- Nej

- noder

- nu

- antal

- talrik

- of

- erbjudanden

- erbjuda

- on

- ONE

- endast

- Åsikter

- Alternativet

- or

- organisation

- Övrigt

- ägaren

- paket

- förpackning

- Papper

- del

- prestanda

- utför

- fas

- phd

- PHP

- plockning

- Bilder

- plato

- Platon Data Intelligence

- PlatonData

- Spela

- spelat

- plus

- Punkt

- positionering

- Inlägg

- Strömförsörjning

- exakt

- förutse

- förutsägelse

- föredragen

- process

- bearbetade

- bearbetning

- Processorn

- Produktion

- Produkter

- protokoll

- leverantörer

- fråga

- snabbare

- snabbt

- snabb

- Betygsätta

- rates

- nå

- Läsa

- skäl

- redesign

- omgjorda

- relaterad

- relevanta

- påminnelse

- Kräver

- REST

- översyn

- reviewing

- Rotation

- höger

- Roll

- Samma

- se

- se

- verkar

- segmentet

- segment

- välj

- halvledare

- servrar

- portion

- flera

- visas

- signifikant

- signifikant

- Kisel

- liknande

- enda

- Storlek

- mindre

- smartphone

- lösning

- LÖSA

- några

- Alldeles strax

- Utrymme

- specifikationer

- fart

- Sponsrade

- standard

- standarder

- anges

- Stick

- Fortfarande

- struktur

- framgång

- framgångsrik

- system

- System

- Målet

- tekniker

- Tekniken

- Teknologi

- text

- än

- tack

- den där

- Smakämnen

- deras

- Dem

- Teorin

- Dessa

- detta

- de

- Genom

- tidsram

- till

- verktyg

- topp

- enorm

- tsmc

- två

- Typ

- tyvärr

- Universell

- uppdatering

- us

- användning

- Begagnade

- med hjälp av

- olika

- försäljare

- via

- var

- Sätt..

- we

- były

- Vad

- när

- medan

- vit

- vitt papper

- varför

- kommer

- med

- Arbete

- skulle

- år

- år

- Avkastning

- dig

- zephyrnet