RISC-V som en instruktionsuppsättningsarkitektur (ISA) har vuxit snabbt i kommersiell betydelse och relevans sedan den släpptes till det öppna samhället 2015, vilket lockar många IP-leverantörer som nu tillhandahåller en mängd olika RTL-kärnor. Roger Espasa, VD och grundare av Semidynamik, har presenterat vid RISC-V-evenemang om hur deras IP är anpassad för datorutmaningar som kräver hög bandbredd och högpresterande kärnor med vektorenheter. Semidynamics grundades 2016, har Barcelona för huvudkontoret och har redan kunder i USA och Asien genom att erbjuda två anpassningsbara RISC-V IP:er:

- Avispado – i beställning RISCV64GCV, stöder AXI och CHI

- Atrevido – out-of-order RISCV64GC, stöder AXI och CHI

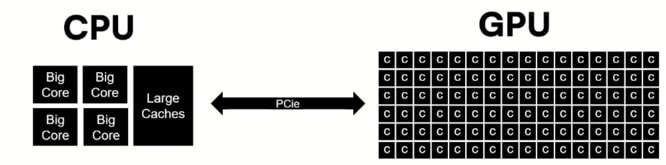

En typisk CPU har en handfull stora kärnor och stora cacher, vilket gör dem lätta att programmera, men inte hög prestanda.

GPU:er, däremot, har många små kärnor som ger hög prestanda för parallell kod, men är svårare att programmera och lägga till kommunikationslatens genom PCIe-bussen när data behöver skickas fram och tillbaka mellan CPU:n och GPU:n.

Tillvägagångssättet hos Espasa är att använda en RISC-V-kärna kopplad till beräkningskärnor som gör den enkel att programmera, högre prestanda för parallella koder och erbjuder noll kommunikationslatens. CPU plus vektorenhet ger det bästa av två världar.

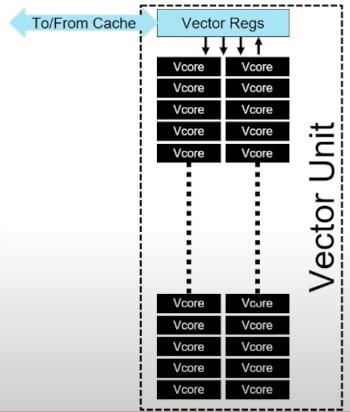

RISC-V-specifikationen dokumenterar 32 vektorregister, och du kan lägga till ett antal vektorkärnor, tillsammans med en anslutning till din cache inuti en vektorenhet.

Med Semidynamics IP kan du anpassa antalet vektorkärnor: 4, 8, 16, 32. Ett annat sätt att se på detta är att notera att 4 vektorkärnor är 256-bitar, upp till 32 vektorkärnor som är 2,048 XNUMX-bitar.

IP-användare väljer också vilka datatyper: FP64, FP32, FP16, BF16, INT64, INT32, INT16, INT8. För en AI-applikation kan de välja datatyperna FP16, BF16, medan en HPC-applikation kan välja FP64, FP32.

Den tredje anpassningen är Vector Register Length, där du för mer prestanda och lägre effekt kan göra vektorregistret större än vektorenheten.

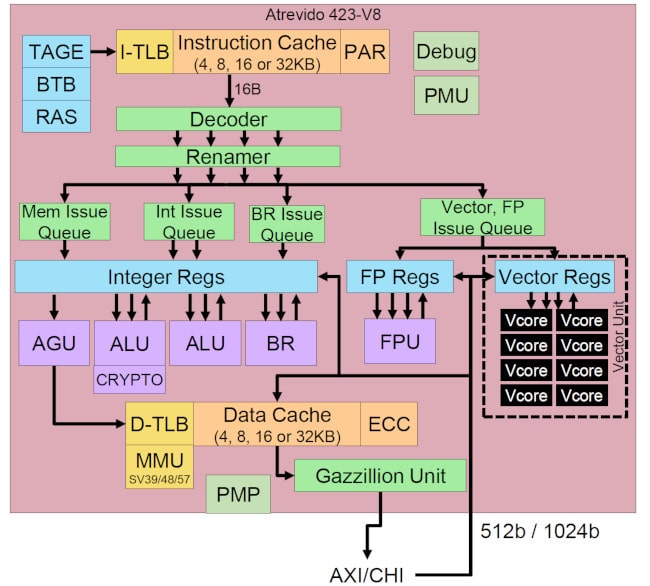

Här är blockschemat för Atrevideo 423-V8:

Vektorenheten är helt ur funktion, vilket är unikt bland RISC-V IP-leverantörer. Kombinationen av vektorenheten plus Gazzillion-enheten kan strömma data med över 60 byte/cykler.

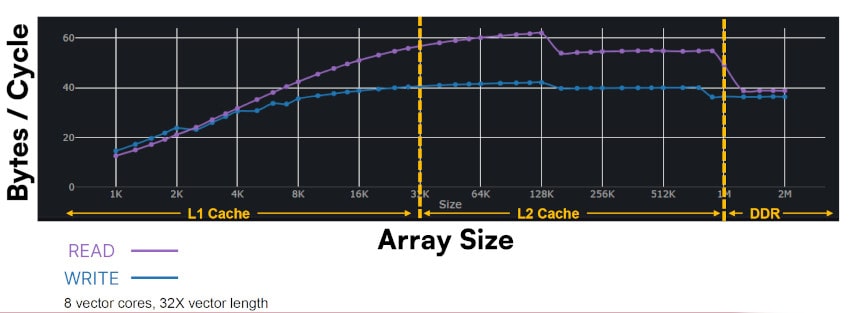

Den lila linjen visar läsprestandan och i L1-cachen är det 20-60 byte/cykel, andra maskiner visar en snabb minskning av bandbredden efter att ha lämnat L1-cachen, medan detta tillvägagångssätt fortsätter, med en utjämning vid 56. Går även till DDR-minne visar en bandbredd på 40. Med en klockfrekvens på 1.0GHz gör det 40 GB/s bandbredd.

IP-kunder kan till och med lägga till sin egen RTL-kod kopplad till Vector Unit för sina egna ändamål.

Prestanda för matrismultiplikation är viktig i AI-arbetsbelastningar, och på OOO V8 Vector Unit finns en topp på 16 FP64 FLOPS/cykel och en topp på 99 % för en matrisstorlek >= 400. För en liten matrisstorlek på 24×24 prestandan är 7 FP64 FLOPS/cykel, eller 50 % av topp. Matrismultiplikation för FP16 med en vektorenhet med 8 vektorkärnor har en topp på 64 FP16 FLOPS/cykel och 99% av toppen för M >= 600.

Ett riktmärke för objektdetektering i realtid som heter YOLO (You Only Look Once) kördes på Atrevido 423-V8-plattformen, och den visade 58 % högre prestanda per vektorkärna än konkurrenterna. Dessa resultat var för video med 24 lager. 5.56 Gops/ram och ca 9M parametrar.

Sammanfattning

Att välja en RISC-V IP-leverantör är en komplicerad uppgift, så att känna till leverantörer som Semidynamics kan hjälpa dig att bättre förstå hur ett anpassat tillvägagångssätt mest effektivt kan köra dina specifika arbetsbelastningar. Med Semidynamics kan du välja mellan arkitektoniska val som i ordning eller ur ordning, med eller utan vektorenheter. De rapporterade siffrorna från denna IP-leverantör ser lovande ut, och jag ser fram emot deras framtida tillkännagivanden.

Related Videos

Dela det här inlägget via:

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- PlatoData.Network Vertical Generative Ai. Styrka dig själv. Tillgång här.

- PlatoAiStream. Web3 Intelligence. Kunskap förstärkt. Tillgång här.

- Platoesg. Fordon / elbilar, Kol, CleanTech, Energi, Miljö, Sol, Avfallshantering. Tillgång här.

- PlatoHealth. Biotech och kliniska prövningar Intelligence. Tillgång här.

- ChartPrime. Höj ditt handelsspel med ChartPrime. Tillgång här.

- BlockOffsets. Modernisera miljökompensation ägande. Tillgång här.

- Källa: https://semiwiki.com/ip/333718-risc-v-64-bit-ip-for-high-performance/

- : har

- :är

- :inte

- :var

- $UPP

- 1

- 16

- 200

- 2015

- 2016

- 24

- 32

- 40

- 60

- 7

- 8

- a

- Om oss

- lägga till

- Efter

- AI

- längs

- redan

- också

- bland

- an

- och

- Meddelanden

- Annan

- Ansökan

- tillvägagångssätt

- arkitektoniska

- arkitektur

- ÄR

- AS

- asien

- At

- locka

- tillbaka

- Bandbredd

- Barcelona

- BE

- riktmärke

- BÄST

- Bättre

- mellan

- Stor

- större

- Bit

- Blockera

- båda

- Bussen

- men

- by

- cache

- kallas

- KAN

- kapabel

- VD

- VD och grundare

- utmaningar

- val

- Välja

- klocka

- koda

- koder

- kombination

- kommersiella

- Kommunikation

- samfundet

- konkurrenter

- komplicerad

- Compute

- anslutna

- anslutning

- Däremot

- Kärna

- kunde

- CPU

- Kunder

- anpassningsbar

- anpassning

- skräddarsy

- kundanpassad

- datum

- Detektering

- dokument

- Drop

- lätt

- effektivt

- Även

- händelser

- För

- vidare

- Framåt

- Grundad

- grundare

- från

- fullständigt

- framtida

- skaffa sig

- kommer

- GPU

- vuxen

- näve

- hårdare

- Har

- hjälpa

- Hög

- högre

- Hur ser din drömresa ut

- HPC

- hq

- HTTPS

- i

- vikt

- med Esport

- in

- inuti

- IP

- IT

- DESS

- jpg

- Menande

- Large

- Latens

- skikt

- lämnar

- Längd

- tycka om

- linje

- se

- lägre

- Maskiner

- göra

- GÖR

- Framställning

- många

- Matris

- max-bredd

- Maj..

- Minne

- min

- mer

- mest

- behov

- Notera

- nu

- antal

- nummer

- objektet

- Objektdetektion

- of

- erbjuda

- on

- gång

- endast

- öppet

- or

- beställa

- Övriga

- ut

- över

- egen

- Parallell

- parametrar

- Godkänd

- Topp

- för

- prestanda

- plattform

- plato

- Platon Data Intelligence

- PlatonData

- plus

- Inlägg

- kraft

- presenteras

- Program

- lovande

- ge

- ger

- syfte

- snabbt

- snabb

- Betygsätta

- Läsa

- realtid

- registrera

- register

- frigöra

- relevans

- Rapporterad

- kräver

- Resultat

- Körning

- in

- show

- visade

- Visar

- eftersom

- Storlek

- Small

- So

- specifik

- specifikation

- streaming

- Stödjande

- uppgift

- än

- den där

- Smakämnen

- Kvarteret

- deras

- Dem

- Dessa

- de

- Tredje

- detta

- fastän?

- Genom

- till

- två

- typer

- typisk

- förstå

- unika

- enhet

- enheter

- us

- användning

- användare

- med hjälp av

- mängd

- leverantör

- försäljare

- via

- Video

- var

- Sätt..

- były

- när

- som

- medan

- med

- utan

- Världens

- Yolo

- dig

- Din

- zephyrnet

- noll-