Termisk stress är ett välkänt problem i avancerade förpackningar, tillsammans med utmaningarna med mekanisk stress. Båda förvärras av heterogen integration, vilket ofta kräver att material blandas med inkompatibla termiska expansionskoefficienter (CTE).

Effekterna visar sig redan och kommer sannolikt bara att bli värre när förpackningens täthet ökar över 1,000 XNUMX stötar per chip.

”Du kombinerar metaller som har en relativt hög CTE, då har du polymerer som har ännu större CTE-styvhet, och sedan har du dielektrikum som har extremt låg CTE. När du väl har satt ihop allt är stress oundviklig”, säger Mario Gonzalez, vetenskaplig chef och FoU-chef för mekanisk och termisk modellering och karakterisering på imec.

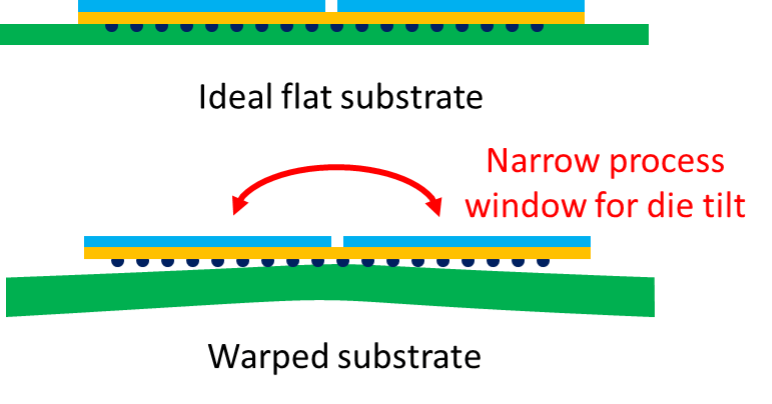

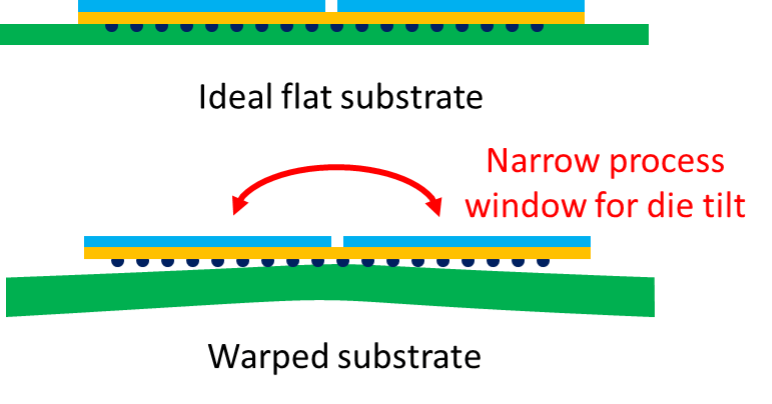

Sådan stress resulterar ofta i betydande skevhet eller lutning, vilket i sin tur leder till tillstånd som minskar tillförlitligheten. "Du har att göra med olika substratteknologier med flera lagerantal", säger Chip Greely, vice vd för ingenjörsarbete på Promex Industries. ”Särskilt olika kärntjocklekar i substrat börjar skapa många klassiska mekaniska problem, inklusive skevhet, vilket har blivit en smärtpunkt för några av de större aktörerna. Vi ber många av våra kunder som har en system-i-paket, heterogen integration multi-chip-modul, att tillhandahålla skuggmoiré-data för sina substrat så att vi kan se hur dess skevhet förändras över återflödestemperaturen och helst hitta dess reflektionspunkt.”

Denna stam har olika negativa effekter, upplevda över många dimensionella skalor, enligt Gilad Barak, vice vd för avancerad ny teknologi på Nytt. "Ofta är böjning och vridning av funktioner på nanostrukturnivå ett resultat av den inbyggda stress som har skapats, som finns i vissa DRAM och front-end logik nanoark," sa han. "Ett annat exempel är mikronskaliga områden där inducerad töjning förhindrar tillverkning av avancerade halvledarstrukturer, vilket är typiskt i 'hållningszoner' runt genomgående kiselvias (TSV). Slutligen kan de storskaliga effekterna av inducerad töjning orsaka waferböjning, vilket avsevärt komplicerar waferhantering och tillverkning, vilket riskerar att spricka själva wafern. Waferböjning ses särskilt under avsättningen av tjocka dielektriska skikt, vilket är vanligt under tillverkningen av 3D NAND-enheter."

Den goda nyheten är att branschen är mycket medveten om dessa och tillhörande problem. Den dåliga nyheten är att det fortfarande är ont om lösningar, även om det finns många tillvägagångssätt som för närvarande undersöks.

"Det finns olika metoder för att minska skevhet, men ingen av dem är helt framgångsrik, och de kommer alltid med kompromisser", säger Frank Chen, chef för applikationer och produkthantering på Bruker Nano Surfaces & Metrology. ”Problemen är inte isolerade till ett snävt urval av applikationer. Varje gång du fäster en form på ett annat substrat kommer du att få dessa problem.”

Allt detta innebär att inspektion och mätteknik måste fortsätta att spela en avgörande roll. Andra problem, såsom hot spots, kan också förvärras när flera chips kombineras i heterogena förpackningar.

"Under testet kommer olika chips att värmas upp vid olika tidpunkter och olika temperaturer, vilket skapar möjliga hot spots som måste kylas ordentligt, säger Andrei Berar, senior director för Test Business Development på Amkor. "Förutom att skapa specifika termiskt aktiva styrenheter - som matchar området för olika chips - finns det betydande ansträngningar för att utveckla adaptiva termiska styrenheter som kan 'förutse' hot spots baserat på vektorerna som tillhandahålls av testprogrammet."

Sådana kombinationer leder också till ökad användning av hybridmetrologi – genom att kombinera olika tekniker för att så snabbt som möjligt komma till roten till problemen.

Design, inspektion, testlösningar

Det klassiska samspelet mellan design, inspektion och termomekanisk stress har faktiskt bara blivit mer komplext med tusentals allt mindre och ömtåligare anslutningar.

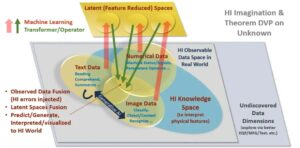

Ett resultat är en förnyad betoning på att växla vänster, för att förhoppningsvis "designa ut" CTE-problemen och därav följande kaskadeffekter som kan leda till överhettning och mekanisk stress. Och för att öka chanserna att förebygga, såväl som att hitta kritiska defekter, behövs både simulering och inspektion, enligt Andras Vass-Varnai, portföljutvecklingschef inom segmentet Electronics and Semiconductor Industry. Siemens Digital Industries-programvara.

"Termisk och strukturell samsimulering med hjälp av beräkningsflödesdynamik (CFD), finita elementmodellering (FEA), etc., i det tidiga designstadiet av paketet hjälper både att förstå den förväntade prestandan för monteringen och ger också en bra grund för ' AI-driven optimering eftersom många av designvalen kan parametriseras”, förklarade Vass-Varnai. "När den första prototypen väl är byggd kan termisk transienttestning hjälpa till att kartlägga komponentens termiska prestanda. Om det finns en bristande överensstämmelse mellan det förväntade och det verkliga termiska beteendet, kan testdata användas för att "kalibrera" materialegenskaperna för paketets digitala tvilling och uppdatera materialbiblioteken för högre initial noggrannhet för kommande konstruktioner."

Att hitta det bästa sättet att testa bump-arrayer och designa för test är en växande utmaning. "Tänk om det finns en signal som går upp och ner?" frågade Rob Aitken, en Synopsys Kompis. "Det skapar ett testproblem, för nu har du en signal som går till ingenstans och en annan signal som kommer från ingenstans, och du måste ta reda på hur du ska testa dessa saker. Undersöker du dem? Men i så fall är det fysiska dimensioner du måste underhålla, och då riskerar du att få mekaniska skador. Eller hittar du någon slags JTAG-liknande struktur? Men det minskar då effektiviteten hos dessa kopplingspunkter. Vi är i den enorma experimentfasen där alla säger, "Kanske det här kommer att fungera, kanske det kommer att fungera." Just nu skulle jag inte nödvändigtvis vilja satsa på vad "det" är."

Det finns både indirekta och direkta testmöjligheter för defektutredning, enligt JCET. Till exempel är CSAM (Computed Scanning Acoustic Tomography) och 3D-röntgen indirekta, medan mekanisk tvärsnittsanalys är ett verktyg för direkt bevis. JCET har avancerad utrustning för termisk karakterisering för att karakterisera material-/strukturproblemen till följd av mekaniska defekter.

Optisk inspektion är, som alltid, det snabbaste tillvägagångssättet för inline-inspektion, men bästa praxis är en hybrid metod. "Den bästa metoden för att upptäcka kortslutningar/öppningar och marginella defekter skulle vara SPI (Solder Paste Inspection) till pre-reflow AOI (automatiserad optisk inspektion) till post-reflow AOI till inline röntgen," rådde Timothy Skunes, vice vd för forskning och utveckling inom Nordson Test & Inspection's Cyberoptik portfölj.

Dessutom kan andra modaliteter vara användbara, speciellt vid avancerade noder. Till exempel är en ny metod för att karakterisera stam i halvledarenheter Raman Spectroscopy (RS). "RS är mycket användbar för mätningar på strukturen, och erbjuder snabba mätningar i storleksordningen sekunder och små fläckstorlekar på några mikron för att möjliggöra detaljerade mätningar", säger Novas Barak. "Svårigheten att direkt mäta belastningen på strukturer innan introduktionen av Raman-spektroskopi som in-line metrologiverktyg i fabriken ledde till tester i mycket senare skeden av tillverkningsprocessen."

I slutändan, för grundlig inspektion, finns det inga skärande hörn. Budgetberäkningar kan kräva jämförande mätvärden, såsom initialkostnaden för ett nytt instrument kontra den löpande kostnaden för överdrivna RMA:er. Och det finns en sak till att tänka på — hur du ser till att du kan lita på din data.

”Ska du slänga det som förmodligen var bra material för att säkerställa att du inte har något problemmaterial i det du skickar vidare till slutanvändaren? Vem ska stå för kostnaden för det?” varnade Mike McIntyre, chef för mjukvaruprodukthantering på På innovation, som rekommenderar en statistisk databas för korrekt jämförande bedömning när man gör automatiserad defektklassificering.

skevhet

Ett av de värsta resultaten av stress är skevhet. Det kan vara förvånande att skevhet kan vara svårt att upptäcka, men effekten är inte alltid så uppenbar som den verkar. Skevhet orsakar små skillnader i planaritet mellan chip och substrat, vilket gör att vissa mikrobump inte ansluter tillräckligt med kuddar nedan, ett fel som kallas icke-vått.

"Tänk på en avancerad processor som är 50 till 60 mm, som ett exempel," sa Chen. "På grund av sin stora storlek är den utmanande att bearbeta utan att det ska ske. Ändå, om verktyget för att fästa stansen är avstämt i mitten av sitt processfönster, kan det klara inspektionen och tillverkas med högt utbyte. Problemet är att toleransen kan vara mycket snäv. Så fort du har lite tärningstilt på toppen av skevningen har du problem som inte är våta."

Än värre, om detta händer vid ojämnheter i intervallet 50 µm ( ̴35 µm bumpstorlek), föreställ dig problemen när bumpens dimensioner krymper ytterligare. Det är redan ett bekymmer för bilindustrin, eftersom den går mot sin nästa generation 2023 till 2024. Den kritiska övergången kommer att vara runt 28nm-noden, sa Chen.

Fig. 1 Formfästverktyg har ett mycket snävt processfönster för formlutning vid skevhet. Källa: Bruker

Icke våta

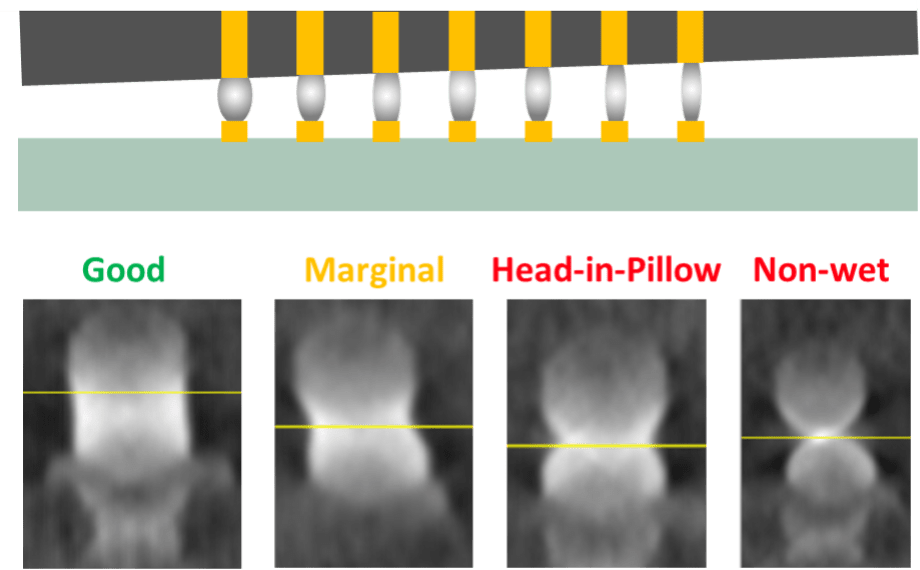

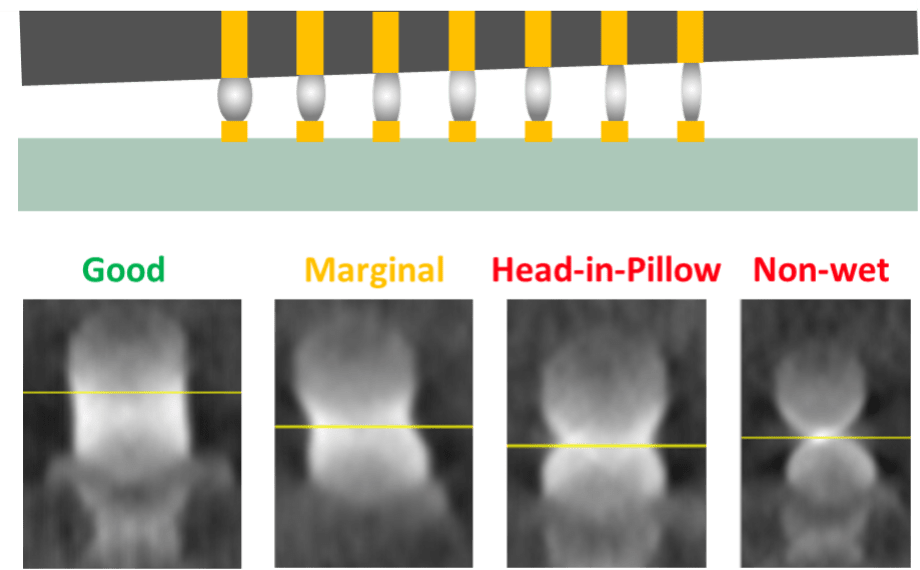

"Icke-våt" är ett brett begrepp som täcker flera problem som kan uppstå med lödbultar, varav de flesta är frustrerande subtila. Eftersom lodet ofta är i flytande tillstånd har processen att applicera det kallats "vätning". Tunna länkar kallas "icke-våta", som blir mer av en utmaning vid mindre noder med tunnare anslutningar.

Icke-våta ämnen slipper ofta typiska screeningprocesser, för att senare dyka upp som returnerade spån (RMA). Grundorsakerna kan vara termiska, mekaniska eller en kombination, till exempel termisk cykling i en bil som också kör i ojämn terräng. Den kumulativa effekten kan ge tillräckligt med termisk-mekanisk spänning för att bryta kontakten.

Det finns ytterligare smeknamn som beskriver specifika typer av problem. Istället för den släta, kolumnformade formen av en bra anslutning, i en "huvud-i-kudde"-defekt, verkar den ena bollen sjunka in i den andra, som ett huvud på en kudde.

"Den har fortfarande kontakt så det elektriska testet kan vara bra, men du kan se att det är väldigt ömtåligt," sa Chen och pekade på röntgenbilden av en huvud-i-kudde. "Så fort du har en viss termisk stress eller mekanisk stress kan den gå sönder helt. Även om det är en kontakt som inte är våt, leder den tunna anslutningen till hög resistans, suboptimal prestanda och kommer troligen inte att hålla länge. En öppen icke-våt fungerar inte alls. I ett typiskt scenario med formlutning finns det en synlig övergång från välformade stötar till icke-våta."

Det kritiska problemet är latenta defekter – anslutningar som är tillräckligt funktionella för att klara det elektriska testet men misslyckas i fält.

Fig. 2 Gradvis övergång från bra ojämnheter till icke-våta i närvaro av formlutning. Källa: Bruker

"Det är ett stort problem just nu med många typer av enheter på grund av effekterna av termisk stress," sade Chen. "En kund hade en produkt som klarade e-testscreeningen och skickades ut. Tyvärr hade de många RMAs på grund av fel som inte var våta som utvecklades efteråt."

Vissa företag tar itu med detta genom smärtsamt tråkiga manuella inspektioner. Tyvärr är alla mänskliga undersökningar föremål för operatörsutmattning, särskilt när examinatorer försöker upptäcka subtila fel under ett flertimmarsskift.

På den positiva sidan finns det nu automatiserade metoder för inspektion, såsom röntgenverktyg som kan användas inline. "Det finns en stor drivkraft mot höghastighets, helautomatisk inspektion för att uppnå <100 dppb, speciellt för fordonsindustrin," sa Chen.

Det blir mer komplicerat därifrån. "Särskilt är lod, boven bakom många icke-våta, också föremål för elektromigrering", säger Tom Marinis, en huvudmedlem i Laboratory Technical Staff på Draper. "Om strömtätheten i en anslutning mellan ett chip och ett substrat är för hög för ett visst lod under en tidsperiod, eftersom smälttemperaturen för lodet kan vara relativt låg jämfört med enhetens driftstemperatur, kan du få migrering av atomerna och bildar faktiskt tomrum och öppnar så småningom upp en koppling."

Marinis varnade för att kommersiella modelleringsverktyg på enhet-PCB-nivå inte är tillräckligt mogna för att konsekvent varna för potentiella elektromigreringsproblem, så det är viktigt att fortfarande utföra ett accelererat åldringstest.

Slutsats

I slutändan kommer att upptäcka tillförlitlighetsproblem från latenta defekter att kräva högre provtagningsmetrologi som är känslig för stansförskjutning, rotation, höjd, lutning och andra parametrar. Det kommer också att kräva mer beroende av multifysisk modellering för att försöka förutse och lösa potentiella problem före produktion. Och när halvledar- och fordonsindustrin fortsätter att blandas samman, står det mycket mer på spel än bara RMA:er.

"Kostnaden för misslyckanden ökar exponentiellt när latenta defekter överförs från enheter till moduler till bilar som kan äventyra människors liv", säger Chen. Det är därför chiptillverkare skapar holistiska lösningar som kombinerar design, inspektion och testning för att bättre fånga upp latenta fel.

- SEO-drivet innehåll och PR-distribution. Bli förstärkt idag.

- Platoblockchain. Web3 Metaverse Intelligence. Kunskap förstärkt. Tillgång här.

- Källa: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- accelererad

- Enligt

- noggrannhet

- exakt

- Uppnå

- aktiv

- faktiskt

- Dessutom

- Annat

- adresse

- avancerat

- Åldrande

- Varna

- Alla

- tillåter

- redan

- Även

- alltid

- analys

- och

- Annan

- förutse

- tillämplig

- tillämpningar

- Tillämpa

- tillvägagångssätt

- tillvägagångssätt

- OMRÅDE

- områden

- runt

- Montage

- bedömning

- associerad

- bifoga

- Automatiserad

- fordonsindustrin

- bilindustrin

- Badrum

- boll

- baserat

- grund

- Bear

- därför att

- blir

- passande

- innan

- bakom

- Där vi får lov att vara utan att konstant prestera,

- nedan

- BÄST

- Bet

- Bättre

- mellan

- Bortom

- Stor

- större

- Bit

- Ha sönder

- bred

- budget

- byggt

- inbyggd

- företag

- affärsutveckling

- kallas

- Kan få

- bil

- bilar

- Vid

- brottning

- Orsak

- Orsakerna

- orsakar

- Centrum

- CFD

- utmanar

- utmanade

- utmaningar

- utmanande

- chanser

- Förändringar

- karakterisera

- chen

- chip

- Pommes frites

- val

- klassiska

- klassificering

- kombination

- kombinationer

- kombinera

- kombinerad

- kombinera

- komma

- kommersiella

- Gemensam

- Företag

- jämfört

- fullständigt

- komplex

- komplicerad

- komponent

- Oro

- villkor

- Kontakta

- anslutning

- Anslutningar

- Tänk

- kontakta

- fortsätta

- Kärna

- hörn

- Pris

- kunde

- beläggning

- skapa

- skapas

- skapar

- Skapa

- kritisk

- Aktuella

- För närvarande

- kund

- Kunder

- skärning

- datum

- Databas

- som handlar om

- densitet

- beskriva

- Designa

- mönster

- detaljerad

- utveckla

- utvecklade

- Utveckling

- anordning

- enheter

- den

- skillnader

- olika

- Svårighet

- digital

- digital tvilling

- dimensioner

- rikta

- direkt

- Direktör

- gör

- inte

- ner

- draper

- chaufför

- dubbade

- under

- Dynamiken

- Tidig

- effekt

- effekter

- effektivitet

- ansträngningar

- Elektronik

- vikt

- Teknik

- tillräckligt

- säkerställa

- Utrustning

- fel

- speciellt

- etc

- Eter (ETH)

- Även

- så småningom

- allt

- exempel

- verkställande

- expansionen

- förväntat

- erfaren

- förklarade

- utforskas

- exponentiellt

- extremt

- MISSLYCKAS

- Misslyckande

- snabbast

- trötthet

- Funktioner

- Kompis

- få

- fält

- Fig.

- Figur

- Slutligen

- hitta

- finna

- Förnamn

- flöda

- formen

- hittade

- från

- frustrerande

- funktionella

- ytterligare

- generering

- skaffa sig

- Går

- kommer

- god

- gradvis

- Odling

- Växer

- Arbetsmiljö

- Hård

- huvud

- höjd

- hjälpa

- hjälper

- Hög

- högre

- höggradigt

- helhetssyn

- Förhoppningsvis

- HET

- Hur ser din drömresa ut

- How To

- HTTPS

- humant

- Hybrid

- Konsekvenser

- med Esport

- in

- Inklusive

- Öka

- ökande

- industrier

- industrin

- inledande

- istället

- Instrumentet

- integrering

- Beskrivning

- Undersökningen

- isolerat

- fråga

- problem

- IT

- sig

- Snäll

- laboratorium

- Large

- storskalig

- större

- Efternamn

- lager

- skikt

- leda

- ledande

- Leads

- Led

- Nivå

- bibliotek

- sannolikt

- länkar

- Flytande

- Bor

- Lång

- Lot

- Låg

- bibehålla

- göra

- Framställning

- ledning

- chef

- manuell

- tillverkad

- många

- karta

- Mario

- matchande

- Materialet

- material

- mogen

- max-bredd

- betyder

- mätningar

- mätning

- mekanisk

- medlem

- Metaller

- metod

- metoder

- Metrics

- Metrology

- kanske

- migration

- mingel

- modellering

- modul

- Moduler

- mer

- mest

- förflyttar

- multipel

- nano

- nödvändigtvis

- behövs

- negativ

- Icke desto mindre

- Nya

- Ny teknik

- nyheter

- Nästa

- nod

- noder

- Uppenbara

- erbjuda

- ONE

- pågående

- öppet

- drift

- Operatören

- optimering

- Tillbehör

- beställa

- Övriga

- paket

- paket

- förpackning

- Smärta

- parametrar

- särskilt

- särskilt

- Godkänd

- människors

- utföra

- prestanda

- perioden

- fas

- fysisk

- platser

- plato

- Platon Data Intelligence

- PlatonData

- Spela

- spelare

- Punkt

- poäng

- polymerer

- portfölj

- positiv

- möjlig

- potentiell

- praktiken

- Närvaron

- VD

- förebyggande

- Principal

- Innan

- förmodligen

- sond

- Problem

- problem

- process

- processer

- Processorn

- Produkt

- produktledning

- Produktion

- Program

- bevis

- ordentligt

- egenskaper

- Prototypen

- ge

- förutsatt

- sätta

- R&D

- område

- snabb

- verklig

- senaste

- rekommenderar

- minska

- minskar

- reflektion

- relativt

- tillförlitlighet

- tillit

- förnyas

- kräver

- Kräver

- forskning

- forskning och utveckling

- resultera

- resulterande

- Resultat

- Risk

- risker

- roller

- rot

- Körning

- Nämnda

- säger

- skalor

- scanning

- scenario

- screening

- sekunder

- verkar

- segmentet

- Val

- halvledare

- senior

- känslig

- flera

- skugga

- Forma

- skifta

- SKIFTANDE

- skeppas

- Kort

- show

- Signal

- signifikant

- signifikant

- simulering

- Storlek

- storlekar

- Small

- mindre

- So

- Mjukvara

- Lösningar

- några

- Alldeles strax

- Källa

- specifik

- spektroskopi

- Spot

- Personal

- Etapp

- stadier

- spel

- starta

- Ange

- statistisk

- Fortfarande

- påkänning

- strukturell

- struktur

- ämne

- framgångsrik

- sådana

- förvånande

- Teknisk

- tekniker

- Tekniken

- testa

- Testning

- Smakämnen

- Området

- deras

- Där.

- termisk

- sak

- saker

- tusentals

- Genom

- Kasta

- tid

- gånger

- till

- tillsammans

- tolerans

- alltför

- verktyg

- verktyg

- topp

- mot

- övergång

- Litar

- SVÄNG

- typer

- typisk

- förstå

- kommande

- Uppdatering

- användning

- Användare

- olika

- Omfattande

- Vice President

- synlig

- ALLBEKANT

- Vad

- som

- medan

- VEM

- kommer

- utan

- Arbete

- värsta

- skulle

- röntgen

- utbyten

- Din

- zephyrnet