Oblikovalci imajo veliko poti za razlikovanje rešitev RISC-V. Ena pot se zažene v različne osnovne prilagoditve in razširitve RISC-V glede na specifikacijo. Drugi se osredotoča na izbiro in sestavljanje blokov IP v popolni zasnovi sistema na čipu (SoC) okoli enega ali več jeder RISC-V. Pojavlja se tretji: medsebojno povezovanje jeder RISC-V in drugih blokov IP z omrežjem na čipu (NoC) namesto s preprosto strukturo vodila. In ne le na vrhunskem nivoju – združevanje jeder RISC-V z NoC-ji odgovarja na številne izzive načrtovanja SoC, kjer morajo podatki učinkovito teči pri kateri koli delovni obremenitvi z uporabo katerega koli protokola na čipu.

Stopnje zmogljivosti se spreminjajo z naprednimi povezovalnimi shemami

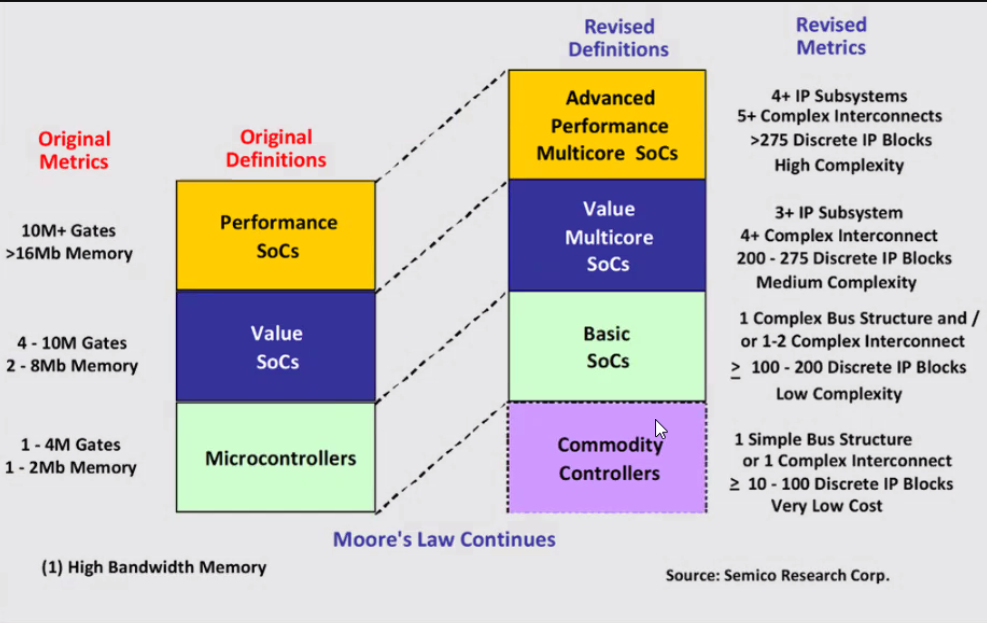

Preprosto štetje vrat, jeder in perifernih blokov ne opisuje več zmogljivosti zasnove SoC. Sheme medsebojnih povezav zdaj opredeljujejo črte med stopnjami zmogljivosti SoC, glede na Semico Research, in odprla se je nova raven, kjer se medsebojne povezave spremenijo iz preprostih struktur vodil v bolj sofisticirane sheme.

Semicova posodobljena definicija priznava tri sile na delu: prodornost večjedrnih zasnov, višjo letvico za tisto, kar velja za kompleksno zasnovo, in kasnejšo zabrisano mejo med "mikrokontrolerjem" in "SoC". V najnovejšem pogledu podjetja Semico pojem števila vrat kot metrike izgine, saj lahko eno sodobno procesorsko jedro s seboj povleče veliko vrat. Kompleksnost postane funkcija medsebojnih povezav, ki se razlikujejo glede na podsisteme in različne bloke IP.

Stopnje zmogljivosti SoC, avtorstvo slike Semico Research Corp.

Kjer bo primerno preprosto vodilo, verjetno del z enim procesorskim jedrom in perifernimi napravami z nizkim delovnim ciklom, ki se ne borijo nenehno za vodilo, Semico vidi raven krmilnika blaga. Vse nad tem postane SoC, verjetno z vsaj nekaterimi zunanjimi napravami, ki se borijo za pasovno širino na čipu in pozornost procesorskih jeder. Višje ravni SoC imajo več jeder in več podsistemov IP, od katerih ima vsak prilagojeno tehnologijo medsebojnega povezovanja.

NoC-ji poberejo več protokolov in podsistemov

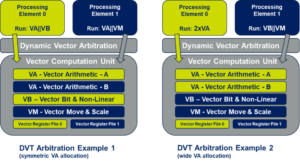

RISC-V je hitro dvignil te stopnje zmogljivosti, ko se pojavijo zmogljivejša jedra, z nič manjšo uporabnostjo na spodnjem koncu lestvice Semico. Vendar pa imajo načrtovalci RISC-V morda manj izkušenj s kompleksnimi povezovalnimi shemami, ki jih vidimo na višjih nivojih. »TileLink je morda prva misel za medsebojno povezovanje RISC-V, vendar ga je lahko težko uporabiti v bolj zapletenih scenarijih,« pravi Frank Schirrmeister, podpredsednik za rešitve in poslovni razvoj za Arteris.

Velemoč NoC je njegova zmožnost povezovanja podsistemov z uporabo različnih protokolov in načrtovalci SoC bodo verjetno naleteli na več protokolov pri celo zmerni kompleksnosti. AXI je izenačil konkurenčne pogoje za preproste blokovne povezave IP. Večjedrne rešitve z bloki za soprocesiranje zahtevajo skladnost predpomnilnika, zaradi česar nastane protokol CHI. Skupna raba V/I pomnilnika je pomagala oblikovati hitrejšo medsebojno povezavo CXL. »Ko je čas za sooptimiziranje računalništva in transporta z različnimi podsistemi in protokoli v igri, je NoC boljša rešitev,« nadaljuje Schirrmeister.

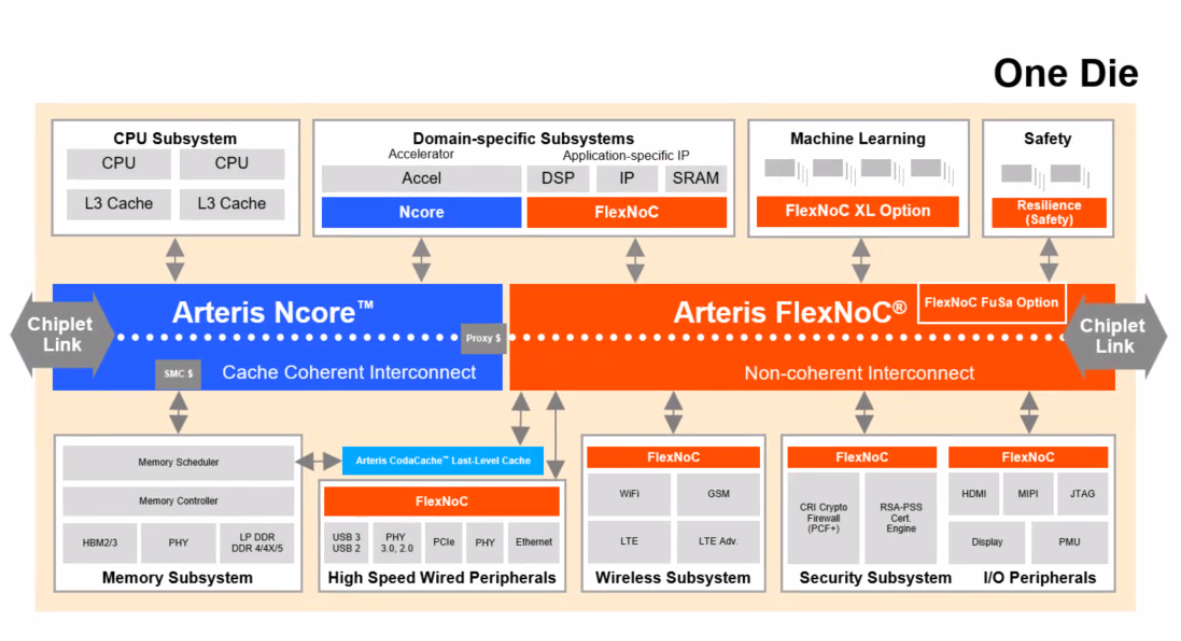

Kako lahko izgleda združevanje jeder RISC-V z NoC? Stranka Arteris Tenstorrent ponuja vpogled v možnosti. Njihov nedavni poudarek je na ustvarjanju čipleta za večkratno uporabo, ki združuje jedra RISC-V, IP za pospeševanje strojnega učenja in standardne zunanje naprave, ki jih najdemo v številnih robnih aplikacijah AI. V obsegu bi lahko izvedba z eno matrico izgledala kot naslednji diagram, z uporabo koherentne medpomnilniške povezave Arteris Ncore in več segmentov nekoherentne medpovezave Arteris FlexNoC.

avtor slike Arteris

Pametni krmilnik pomnilnika (SMC) zagotavlja visoko zmogljivo pomnilniško povezavo na ravni strežnika v aplikacijah, ki zahtevajo veliko pomnilnika. Neimenovana "povezava čipleta" bi lahko bila UCIe, razmeroma nova specifikacija, optimizirana za tesnejšo integracijo čipleta. Ko se pojavijo nove medsebojne povezave podsistemov, je prilagoditev dela NoC bolj obvladljiva kot raztrganje celotne strukture celotnega čipa.

Združevanje jeder RISC-V z NoC-ji zmanjša tveganje in čas do trženja

Če je ta diagram videti zapleten in odobren, morda večina aplikacij RISC-V trenutno ni tako zapletena, razmislite o tem: čipleti že spodbujajo integracijo veliko višje. Današnji napredni večjedrni del RISC-V bo vrednost SoC naslednjega leta, saj bodo inovacije pospešene.

Razvojna orodja Arteris Ncore in Arteris FlexNoC dajejo RTL za implementacijo, kar zagotavlja več prednosti. Fizična ocena NoC je v poteku dela EDA enostavna. Prilagoditve parametrov NoC, kot je število stopenj cevovoda, so v orodjih EDA prav tako oddaljene nekaj klikov. Zgoraj omenjene spremembe za dodajanje protokola podsistema so tudi zlahka dosegljive. »Na višjem nivoju uporabniki dobijo takojšen dostop do našega strokovnega znanja o NoC,« pravi Schirrmeister. »Na nizkem nivoju so naša orodja preprosta za uporabo za uspeh prvega prehoda in zagotavljajo pot rasti za bolj ambiciozne prihodnje projekte s kompleksnimi povezavami.«

Združevanje jeder RISC-V z NoC-ji zmanjša tveganje, da bi še en blok IP vstopil v zasnovo in sprožil valovanje preoblikovanja medsebojnih povezav v celotnem čipu. Prav tako skrajša čas do trženja za kompleksne zasnove SoC v primerjavi s povezovalnimi strukturami, ki jih naredi sam. Tukaj nismo razpravljali o drugih prednostih NoC-jev, kot sta pasovna širina in upravljanje porabe energije, vendar je primer NoC-jev v zasnovah RISC-V močan že ob upoštevanju raznolike mešanice protokolov.

Obiščite spletno mesto Arteris za več informacij o NoC in drugih izdelkov.

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :ima

- : je

- :ne

- :kje

- $GOR

- a

- sposobnost

- nad

- pospešek

- dostop

- doseženo

- Po

- čez

- dodajanje

- Popravki

- napredno

- Prednosti

- AI

- že

- Prav tako

- ambiciozni

- an

- in

- Še ena

- odgovori

- kaj

- karkoli

- zdi

- aplikacije

- SE

- okoli

- AS

- At

- pozornosti

- stran

- pasovna širina

- bar

- BE

- postane

- Prednosti

- Boljše

- med

- Block

- Bloki

- avtobus

- poslovni

- poslovni razvoj

- vendar

- CAN

- primeru

- izzivi

- spremenite

- spreminjanje

- čip

- združevanje

- blago

- v primerjavi z letom

- dokončanje

- kompleksna

- kompleksnost

- Izračunajte

- Connect

- povezava

- povezave

- Razmislite

- šteje

- upoštevamo

- se nadaljuje

- stalno

- krmilnik

- Core

- telo

- bi

- štetje

- Ustvarjanje

- stranka

- datum

- opredeliti

- opredelitev

- Povpraševanje

- Oblikovanje

- oblikovalci

- modeli

- Razvoj

- razvojna orodja

- drugačen

- težko

- razpravljali

- razne

- do

- vožnjo

- vsak

- lahka

- Edge

- učinkovito

- pojavljajo

- smirkovim

- konec

- V

- Celotna

- Tudi

- izkušnje

- strokovno znanje

- razširitve

- hitreje

- Nekaj

- Polje

- boju proti

- prva

- Pretok

- Osredotočite

- Osredotoča

- po

- za

- sile

- je pokazala,

- frank

- iz

- funkcija

- Prihodnost

- Gain

- Gates

- Giving

- Pogled

- odobreno

- Rast

- Imajo

- pomagal

- tukaj

- visoka

- visokozmogljivo

- več

- Vendar

- HTTPS

- slika

- Takojšen

- Izvajanje

- in

- Podatki

- Inovacije

- Namesto

- integracija

- medsebojno povezovanje

- medsebojne povezave

- v

- IP

- IT

- ITS

- samo

- Zadnji

- izstrelki

- vsaj

- manj

- kot

- Verjeten

- vrstica

- linije

- več

- Poglej

- izgleda kot

- POGLEDI

- nizka

- nižje

- upravljanje

- več

- max širine

- Maj ..

- mogoče

- Spomin

- omenjeno

- meritev

- mix

- zmerno

- sodobna

- spremembe

- več

- Najbolj

- premaknjeno

- veliko

- več

- morajo

- Novo

- Naslednja

- št

- Pojem

- zdaj

- Številka

- of

- on

- ONE

- odprt

- optimizirana

- or

- Ostalo

- naši

- izhod

- Pace

- seznanjanje

- parameter

- del

- pot

- za

- performance

- periferni

- periferne

- fizično

- kramp

- Izbiramo

- plinovod

- platon

- Platonova podatkovna inteligenca

- PlatoData

- Predvajaj

- igranje

- možnosti

- Prispevek

- potencial

- moč

- močan

- Procesor

- Izdelki

- projekti

- protokol

- protokoli

- zagotavljajo

- zagotavlja

- zagotavljanje

- hitro

- zlahka

- nedavno

- prepozna

- preoblikovanje

- zmanjšuje

- relativno

- Raziskave

- za večkratno uporabo

- Pravica

- Ripple

- Rise

- Tveganje

- Run

- s

- pravi

- Lestvica

- scenariji

- sheme

- Oddelek

- videl

- vidi

- segmentih

- izbiranje

- več

- Oblikujte

- delitev

- Enostavno

- saj

- sam

- pametna

- Rešitev

- rešitve

- nekaj

- prefinjeno

- specifikacija

- postopka

- standardna

- naravnost

- močna

- Struktura

- strukture

- kasneje

- uspeh

- taka

- velesila

- Tehnologija

- kot

- da

- O

- njihove

- te

- tretja

- ta

- mislil

- 3

- živali

- Vezi

- tesnejši

- čas

- do

- današnje

- skupaj

- orodja

- prevoz

- sproži

- NEIMENOVAN

- posodobljeno

- uporaba

- Uporabniki

- uporabo

- vrednost

- različnih

- različno

- preko

- Poglej

- vp

- we

- Spletna stran

- Kaj

- Kaj je

- kdaj

- bo

- z

- delo

- potek dela

- zefirnet