Izzivi pri testiranju SoC nastanejo zaradi kompleksnosti in raznolikosti funkcionalnih blokov, integriranih v čip. Ko postanejo sistemi na čipu bolj zapleteni, postane vse težje dostopati do vseh funkcionalnih blokov v čipu za testiranje. SoC-ji lahko vsebujejo tudi milijarde tranzistorjev, zaradi česar je testiranje čipov izjemno zamudno. Ker čas testiranja neposredno vpliva na stroške testiranja, je zmanjšanje časa testiranja ključnega pomena za obvladovanje stroškov končnega izdelka. Avtomatski generator testnih vzorcev (ATPG) je ključni del testiranja SoC, saj ustvarja testne vzorce za odkrivanje napak v načrtu. Vendar pa je avtomatizacija ATPG zahtevna naloga, zlasti za kompleksne SoC, zaradi velikega števila funkcionalnih blokov in testnih točk, ki jih je treba pokriti. Razvoj učinkovitih in učinkovitih algoritmov ATPG je ključni izziv za testiranje SoC. Toda mnoga današnja orodja ATPG niso popolnoma avtomatizirana. Uporabniki se morajo naučiti vseh ukazov in možnosti, ki jih ponujajo orodja, da jih lahko učinkovito uporabljajo.

Ali obstaja rešitev, ki prinese nekaj avtomatizacije v proces ATPG in s tem poveča inženirsko produktivnost? Kaj pa, če ta rešitev prinaša tudi znatne prihranke pri preskusnem času? Rešitev Tessent Streaming Scan Network (SSN) podjetja Siemens EDA obljublja, da bo zagotovila te prednosti. To je med nedavno konferenco User2User utemeljil Intel, ena od strank družbe Siemens EDA. Intelov Toai Vo je predstavil dokazne točke na podlagi izkušenj svoje ekipe z njihovim prvim dizajnom z uporabo rešitve Tessent SSN. V njegovi ekipi so bili Kevin Li, Joe Chou in Chienkuo (Tom) Woo.

Rešitev Tessent SSN

Pri standardnem pristopu testiranja skeniranja se testni podatki nalagajo v vezje en bit naenkrat in premikajo skozi verige skeniranja, da se opazujejo izhodni odzivi. Ta postopek se ponovi za vsak preskusni vzorec, kar je lahko dolgotrajno in lahko privede do dolgih preskusnih časov. Toda rešitev Tessent SSN paketira testne podatke za drastično zmanjšanje truda pri implementaciji DFT in krajše čase proizvodnih testov. Z ločitvijo zahtev DFT na ravni jedra in ravni čipa je mogoče vsako jedro oblikovati z najbolj optimalno konfiguracijo stiskanja za to jedro. To rešitev je mogoče uporabiti za učinkovito testiranje velikih in zapletenih čipov, ki imajo veliko število notranjih vozlišč, ki jih je treba preizkusiti. Uporablja namensko omrežje za prenos testnih podatkov na pretočni način, kar omogoča vzporedno obdelavo podatkov in s tem skrajša čas testiranja.

Prilagodljivost

Streaming Scan Network podpira razširljive arhitekture skeniranja, ki lahko upravljajo sisteme na čipu z velikim številom funkcionalnih blokov. Orodje zagotavlja razširljiv pristop testiranja poljubnega števila jeder hkrati, hkrati pa zmanjšuje čas testiranja in količino skeniranih podatkov. Testna infrastruktura Tessent SSN je zgrajena okoli standarda IEEE 1687/IJTAG za zagotavljanje večje prilagodljivosti in razširljivosti za obvladovanje kompleksnejših načrtov in testnih scenarijev.

Avtomatizacija

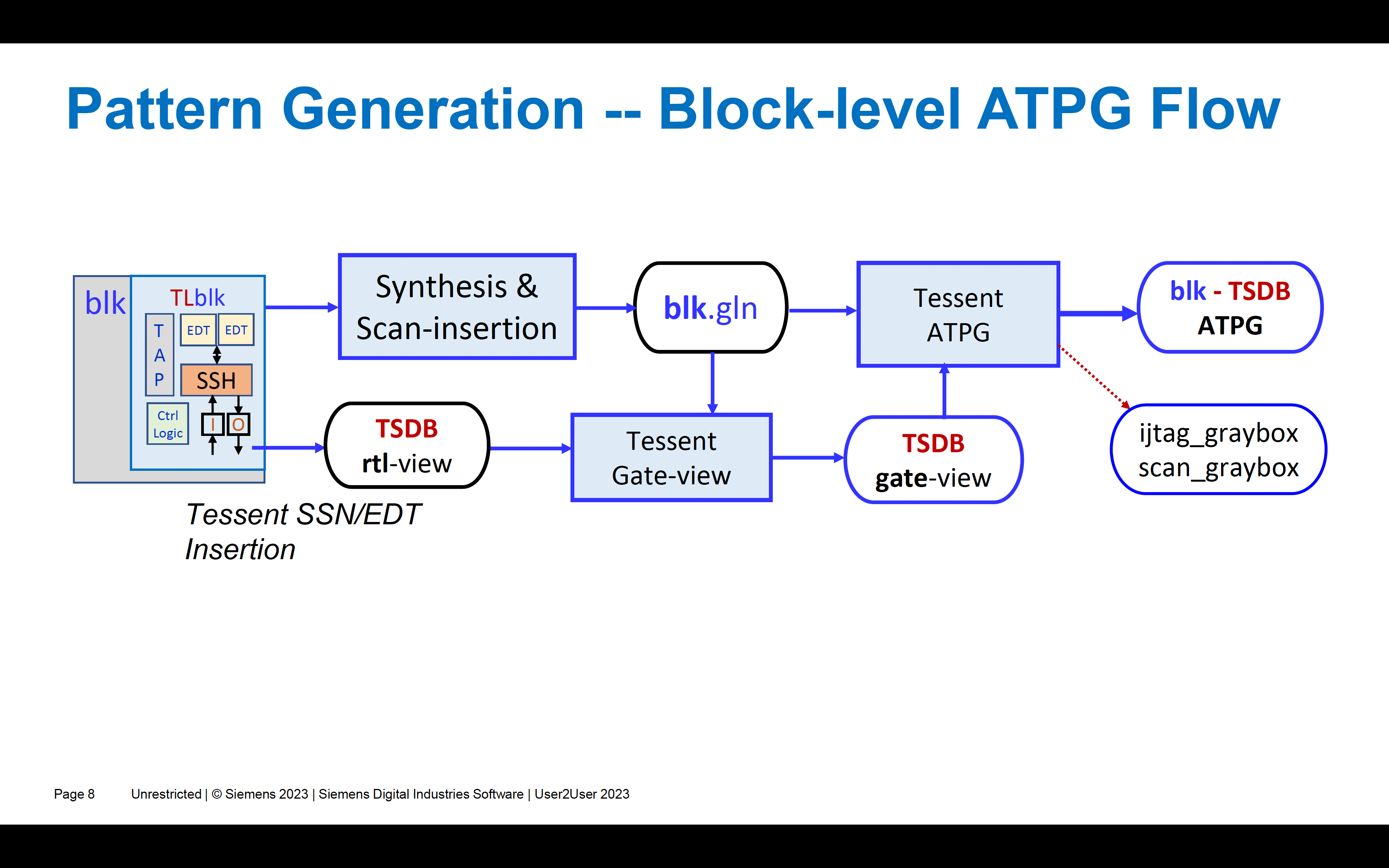

Hierarhična objektno usmerjena narava testne infrastrukture je primerna za lažjo avtomatizacijo. Z uporabo infrastrukture Tessent lahko uporabnik preprosto vstavi testno logiko v čip. Postopek se začne z zasnovo RTL, kjer se s pomočjo avtomatizacije vstavi preskusna logika SSN.

Preizkusite prihranek časa

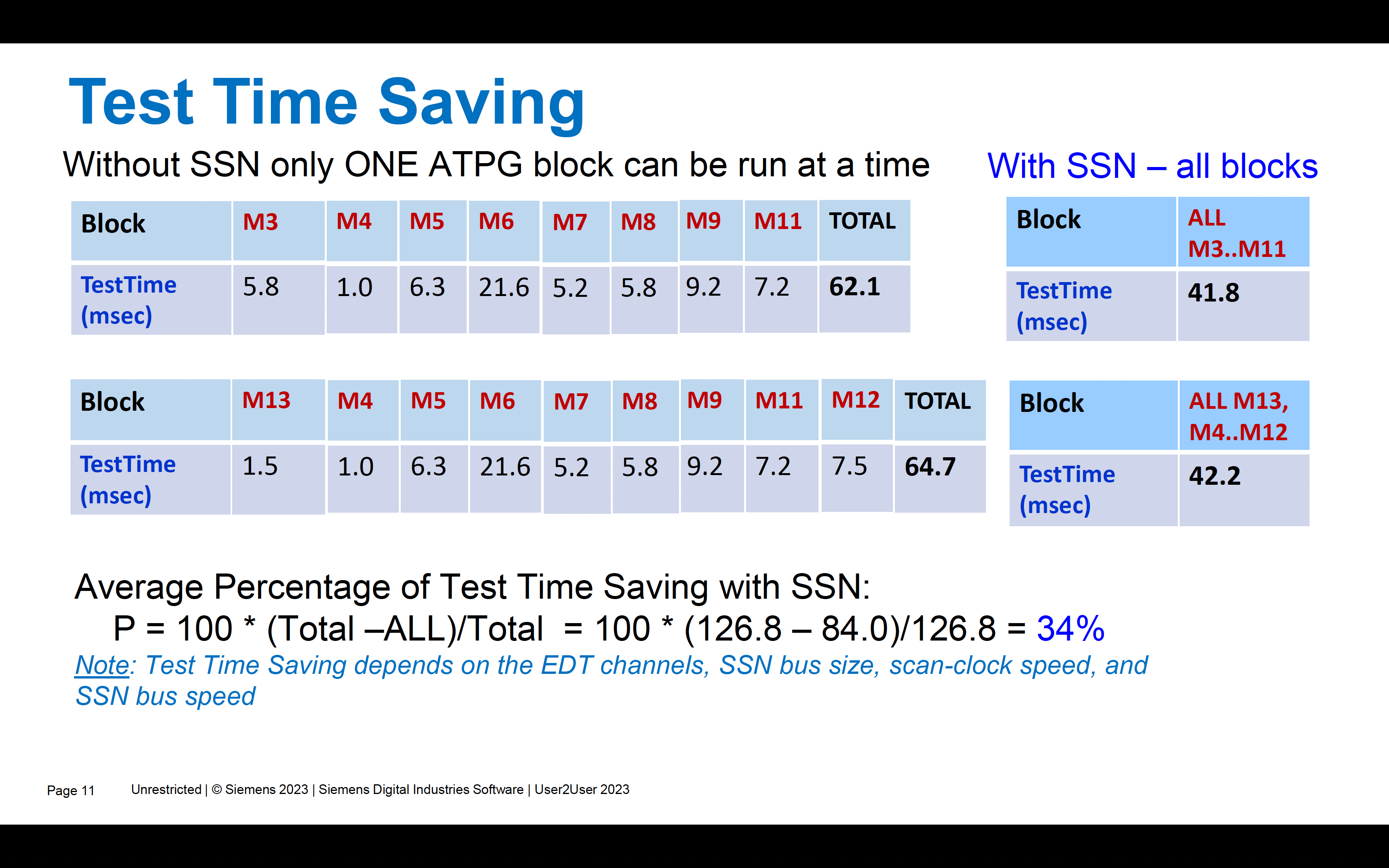

Z uporabo tradicionalnega pristopa ATPG je običajno mogoče naenkrat izvajati samo blok, kar podaljša skupni čas preskusa. S pristopom Tessent SSN ATPG je mogoče več blokov izvajati vzporedno, s čimer se močno zmanjša skupni čas testiranja. Naslednja tabela prikazuje prihranek časa pri preskusu, ki ga je dosegla Toaijeva ekipa pri svojem dizajnu.

Povzetek

Toaijeva ekipa je ugotovila, da je prehod s tradicionalnega vgrajenega determinističnega testiranja (EDT), ki temelji na kanalih ATPG, na paketno zasnovan ATPG s SSN zelo enostaven. Rešitev Tessent SSN je močno skrajšala inženirski napor in čas priprave silicija. Skrajšanje preskusnega časa je bilo znatno v primerjavi s tradicionalno rešitvijo za testiranje. Po besedah Toai Voja je to absolutno inovativna testna rešitev in resnično deluje.

Za več podrobnosti obiščite stran izdelka Tessent SSN.

Preberite tudi:

Doseganje optimalnega PPA pri umestitvi in prenos do odjave

Zmanjšanje učinkov širjenja napak DFE na hitre povezave SerDes

Zaupanje v strojno opremo za avtomobilsko varnost

Delite to objavo prek:

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoAiStream. Podatkovna inteligenca Web3. Razširjeno znanje. Dostopite tukaj.

- Kovanje prihodnosti z Adryenn Ashley. Dostopite tukaj.

- Kupujte in prodajajte delnice podjetij pred IPO s PREIPO®. Dostopite tukaj.

- vir: https://semiwiki.com/eda/328395-tessent-ssn-enables-significant-test-time-savings-for-soc-atpg/

- : je

- :ne

- :kje

- $GOR

- a

- absolutno

- dostop

- doseže

- algoritmi

- vsi

- Prav tako

- an

- in

- kaj

- pristop

- SE

- okoli

- AS

- At

- Avtomatizirano

- Samodejno

- Avtomatizacija

- avtomobilska

- temeljijo

- BE

- postanejo

- postane

- Prednosti

- milijardah

- Bit

- Block

- Bloki

- prinašajo

- Prinaša

- zgrajena

- vendar

- by

- CAN

- knjigovodska

- verige

- izziv

- izzivi

- izziv

- Channel

- čip

- čipi

- v primerjavi z letom

- kompleksna

- kompleksnost

- Konferenca

- konfiguracija

- Core

- strošek

- zajeti

- kritično

- ključnega pomena

- Stranke, ki so

- datum

- namenjen

- poda

- dostavo

- daje

- Oblikovanje

- zasnovan

- modeli

- Podrobnosti

- razvoju

- težko

- neposredno

- raznolikost

- dramatično

- 2

- med

- vsak

- lažje

- enostavno

- lahka

- Učinkovito

- učinkovito

- Učinki

- učinkovite

- učinkovito

- prizadevanje

- vgrajeni

- omogoča

- omogočanje

- Inženiring

- izboljšanje

- Napaka

- zlasti

- izkušnje

- izredno

- napake

- prva

- prilagodljivost

- Pretok

- po

- za

- je pokazala,

- iz

- v celoti

- funkcionalno

- ustvarja

- generacija

- generator

- več

- zelo

- ročaj

- Imajo

- visoka

- njegov

- Vendar

- HTTPS

- IEEE

- if

- Vplivi

- Izvajanje

- in

- vključeno

- vedno

- Infrastruktura

- inovativne

- integrirana

- Intel

- notranji

- v

- IT

- sam

- Ključne

- velika

- vodi

- UČITE

- Stopnja

- Logika

- Long

- Izdelava

- upravljanje

- Način

- proizvodnja

- več

- max širine

- selitev

- minimiziranje

- več

- Najbolj

- več

- Narava

- Nimate

- mreža

- vozlišča

- Običajno

- Številka

- predmet

- opazujejo

- of

- ponujen

- on

- ONE

- samo

- optimalna

- možnosti

- Da

- izhod

- Stran

- vzporedno

- del

- Vzorec

- vzorci

- platon

- Platonova podatkovna inteligenca

- PlatoData

- točke

- Prispevek

- predstavljeni

- Postopek

- obravnavati

- Izdelek

- produktivnost

- Obljublja

- dokazilo

- zagotavlja

- Preberi

- res

- nedavno

- zmanjša

- Zmanjšana

- zmanjšanje

- Zmanjšanje

- ponovi

- Zahteve

- odgovorov

- koren

- Run

- Prihranki

- Prilagodljivost

- razširljive

- skeniranje

- scenariji

- premaknil

- Razstave

- Siemens

- pomemben

- Silicij

- Rešitev

- nekaj

- standardna

- pretakanje

- Podpira

- miza

- Naloga

- skupina

- Test

- Testiranje

- da

- O

- njihove

- Njih

- Tukaj.

- s tem

- te

- ta

- skozi

- čas

- zamudno

- krat

- do

- danes

- orodje

- orodja

- Skupaj za plačilo

- tradicionalna

- posredujejo

- Zaupajte

- uporaba

- Rabljeni

- uporabnik

- Uporabniki

- uporabo

- zelo

- preko

- Obseg

- je

- Kaj

- ki

- medtem

- z

- v

- woo

- besede

- deluje

- zefirnet