Od svojega prvega nastopa v osemdesetih letih prejšnjega stoletja z 1980Mbps skupnimi omrežji LAN prek koaksialnih kablov je Ethernet doživljal dosleden napredek, zdaj pa lahko podpira hitrosti do 10Tbps. Ta napredek je omogočil Ethernetu, da služi širšemu naboru aplikacij, kot so pretakanje v živo, radijska dostopovna omrežja in industrijski nadzor, s poudarkom na pomembnosti zanesljivega prenosa paketov in kakovosti storitev. S trenutno internetno pasovno širino, ki brni pri ~1.6 Tbps, narašča povpraševanje po izboljšanem upravljanju prometa znotraj podatkovnega centra v ozadju. Čeprav posamezni strežniki še ne delujejo na ravneh terabitov na sekundo, se skupni promet podatkovnih centrov približuje temu obsegu, zaradi česar je skupina IEEE 500dj spodbudila k prizadevanjem za standardizacijo in zahteva robustne krmilnike Ethernet in SerDes za upravljanje vse večjega pretoka podatkov. Med tem ozadjem naraščajočih zahtev medprocesorska komunikacija že dosega te hitrosti.

Komunikacija med procesorji vodi do potrebe po stopnjah 1.6T z minimalno zakasnitvijo. Medtem ko so posamezne naprave omejene z lastnimi procesorskimi zmogljivostmi in velikostjo čipov, lahko združevanje čipov znatno poveča te zmogljivosti. Pričakuje se, da bodo prvi generaciji aplikacij sledile povezave med stikali znotraj podatkovnih centrov, ki bodo omogočale združevanje visoko zmogljivih procesorjev in pomnilnika, kar bo povečalo razširljivost in učinkovitost znotraj računalništva v oblaku.

Pobuda IEEE 802.3dj: napredek standardov Ethernet za interoperabilnost 1.6 Tbps

Skladnost z razvijajočimi se prizadevanji za standardizacijo je ključnega pomena za brezhibno interoperabilnost ekosistemov. Skupina IEEE 802.3dj je v procesu oblikovanja prihajajočega standarda Ethernet, ki zajema fizične plasti in parametre upravljanja za hitrosti od 200G do 1.6 terabita na sekundo. Cilj skupine je hitrost prenosa podatkov Ethernet MAC 1.6 Tbps, s ciljem doseči največjo stopnjo bitnih napak ne več kot 10-13 na ravni MAC. Dodatne določbe vključujejo izbirne 16 in 8 pasovne vmesnike priključne enote (AUI), primerne za različne aplikacije čipov, ki izkoriščajo 112G in 224G SerDes. Fizično specifikacija 1.6 Tbps vključuje prenos prek 8 parov bakrenih twinax kablov do enega metra in 8 parov vlaken za razdalje med 500 metri in 2 km. Čeprav je popolna ratifikacija standarda predvidena do pomladi 2026, je glavni nabor funkcij predviden za dokončanje leta 2024.

Preobremenitev pasovne širine in odpravljanje napak v podsistemih 1.6T Ethernet

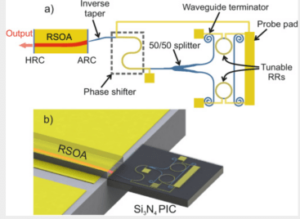

Slika 1: Diagram, ki prikazuje komponente podsistema 1.6T Ethernet.

V prejšnjih ponovitvah Etherneta se je PCS osredotočal predvsem na kodiranje podatkov za zanesljivo zaznavanje paketov. Vendar pa s stopnjevanjem na 1.6T Ethernet hitrosti postane potreba po vnaprejšnjem odpravljanju napak (FEC) očitna, zlasti za preprečevanje poslabšanja signala pri celo kratkih povezavah. V ta namen 1.6T Ethernet še naprej uporablja Reed-Solomon FEC. Ta pristop zgradi kodno besedo, ki obsega 514 10-bitnih simbolov, kodiranih v blok 544 simbolov, kar povzroči 6-odstotno obremenitev pasovne širine. Te kodne besede FEC so porazdeljene po fizičnih povezavah AUI, tako da vsaka fizična povezava (8 za 1.6T Ethernet) ne nosi celotne kodne besede. Ta metoda ne daje samo dodatne zaščite pred izbruhi napak, ampak tudi omogoča paralelizacijo na oddaljenem koncu dekoderja, s čimer se zmanjša zakasnitev.

Physical Medium Attachment (PMA), ki vključuje menjalnik in SerDes, prenaša signal Ethernet na oddane kanale. Za 1.6T Ethernet to vključuje 8 kanalov, od katerih vsak deluje pri 212 Gbps, kar predstavlja 6 % FEC režijske stroške. Uporabljena tehnika modulacije je 4-nivojska amplitudna modulacija impulza (PAM-4), ki kodira dva podatkovna bita za vsak prenosni simbol, s čimer učinkovito podvoji pasovno širino, ko je v nasprotju s tradicionalnim pristopom nepovratne ničle (NRZ). Prenosni mehanizem temelji na digitalno-analogni pretvorbi, medtem ko na sprejemnem koncu analogno-digitalna pretvorba v kombinaciji z DSP-ji zagotavlja natančno ekstrakcijo signala.

Poleg tega je pomembno omeniti, da Ethernet PCS uvaja "zunanji FEC", ki se razteza od konca do konca na Ethernet povezavi. Za okrepitev kanalov z daljšim dosegom je v pripravi dodana plast popravljanja napak za posamezne fizične linije, ki bo verjetno sprejela Hammingovo kodo FEC. Pričakuje se, da bo ta popravek našel primarno uporabo v modulih optičnih oddajnikov, kjer je tak popravek nujen.

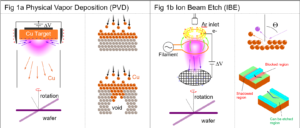

Slika 2: Diagram, ki prikazuje dodatne režijske stroške, dodane pri uporabi povezanega FEC za razširjen doseg.

V primeru sistema, prikazanega na sliki 2, sta MAC in PCS povezana prek optičnega modula in raztezanega vlakna. PCS ima stopnjo bitnih napak 10-5 na povezavi optičnega modula, plus napake same optične povezave. Uporaba edinega RS-FEC od konca do konca ne bi zadostovala za dosego 10-13 Standard Ethernet, zaradi česar je povezava nezanesljiva. Možnost bi bila trojna izvedba ločenega RS FEC na vsakem skoku, kar bi znatno povečalo stroške in zakasnitev. Učinkovitejša rešitev je integracija povezane Hammingove kode FEC posebej za optično povezavo, ki skrbi za tipične naključne napake optičnih povezav. Ta notranja plast FEC ustvari dodatno razširitev linijske hitrosti z 212 Gbps na 226 Gbps, zato je bistveno, da lahko SerDes podpira to linično hitrost.

Izzivi zakasnitve v sistemih 1.6T Ethernet

Slika 3: Pot zakasnitve za podsistem 1.6T Ethernet.

Različne komponente prispevajo k zakasnitvi etherneta: čakalna vrsta prenosa, trajanje prenosa, srednji čas prehoda ter več časov obdelave in sprejema. Za vizualizacijo si oglejte sliko 3, ki prikazuje celovit podsistem 1.6T Ethernet. Medtem ko lahko na zakasnitev vpliva odzivni čas oddaljene aplikacije, je ta dejavnik zunanji za Ethernet in je zato med analizo zakasnitve pogosto izključen. Zmanjšanje zakasnitve na vmesniku Ethernet zahteva razumevanje posebnih okoliščin. Na primer, zakasnitev morda ni glavna skrb za trank povezave med stikali zaradi inherentnih zamud pri počasnejših povezavah odjemalcev. Tudi razdalja igra vlogo; večje dolžine povzročijo večjo zakasnitev. Seveda to ne pomeni, da bi morali spregledati zakasnitev v drugih scenarijih, zmanjšanje zakasnitve je vedno cilj.

Zakasnitev prenosa je sama po sebi povezana s hitrostjo Etherneta in velikostjo okvirja. Natančneje, za sistem 1.6T Ethernet je za prenos paketa najmanjše velikosti potrebno 0.4ns – v bistvu en okvir Ethernet na takt 2.5 GHz. Po drugi strani pa oddajanje standardnega okvirja največje velikosti traja 8 ns, kar se pri Jumbo okvirjih podaljša na 48 ns. Izbrani medij dodatno narekuje latenco. Optična vlakna imajo na primer običajno zakasnitev 5 ns na meter, medtem ko so bakreni kabli nekoliko hitrejši pri 4 ns na meter.

Precejšen del celotne zakasnitve je zakoreninjen v krmilniku sprejemnika. Dekoder RS FEC sam po sebi uvaja zakasnitev. Za začetek odpravljanja napak mora sistem prejeti 4 kodne besede, kar pri 1.6 Tbps znaša 12.8 ns. Poznejše dejavnosti, vključno s popravljanjem napak in medpomnjenjem, povečajo to zakasnitev. Medtem ko trajanje shranjevanja kodne besede FEC ostaja dosledno, je zakasnitev med sprejemom sporočila odvisna od specifične izvedbe. Kljub temu je zakasnitev mogoče optimizirati z uporabo natančnih strategij digitalnega oblikovanja.

V bistvu obstaja inherentna, neizogibna zakasnitev zaradi mehanizma FEC in fizične razdalje ali dolžine kabla. Poleg teh dejavnikov ima strokovno znanje o oblikovanju ključno vlogo pri zmanjševanju zakasnitve krmilnika Ethernet. Izkoriščanje celovite rešitve, ki integrira in optimizira MAC, PCS in PHY, utira pot najučinkovitejši izvedbi z nizko zakasnitvijo.

Povzetek

Slika 4: Uspeh silicija prvega prehoda za Synopsys 224G Ethernet PHY IP v 3nm procesu, ki prikazuje zelo linearne oči PAM-4.

1.6 Tbps Ethernet je prilagojen aplikacijam, ki zahtevajo najbolj pasovno širino in so občutljive na zakasnitve. S pojavom tehnologije 224G SerDes, v povezavi z napredkom v MAC in PCS IP, so zdaj dostopne celovite rešitve, ki se nenehno prilagajajo razvijajočim se standardom 1.6T Ethernet. Poleg tega morajo zaradi zakasnitve, ki je bistvena za protokol in metode odpravljanja napak, digitalno in analogno zasnovo IP vestno oblikovati strokovni oblikovalci, da se izognejo vnašanju nepotrebne zakasnitve v podatkovno pot.

Doseganje vrhunskih zmogljivosti za modele 1.6T SoC zahteva učinkovito optimizirano arhitekturo in natančno načrtovalsko prakso za vsako komponento čipa. To poudarja varčevanje z energijo in minimizira silikonski odtis, s čimer postane hitrost prenosa podatkov 1.6T resničnost. Preizkušen Synopsys 224G Ethernet PHY IP je postavil temelje za krmilnik 1.6T MAC in PCS. Z uporabo vrhunskih tehnik oblikovanja, analize, simulacije in merjenja Synopsys še naprej zagotavlja izjemno celovitost signala in zmogljivost tresenja z popolna rešitev Ethernet, vključno z MAC+PCS+PHY.

- Distribucija vsebine in PR s pomočjo SEO. Okrepite se še danes.

- PlatoData.Network Vertical Generative Ai. Opolnomočite se. Dostopite tukaj.

- PlatoAiStream. Web3 Intelligence. Razširjeno znanje. Dostopite tukaj.

- PlatoESG. Ogljik, CleanTech, Energija, Okolje, sončna energija, Ravnanje z odpadki. Dostopite tukaj.

- PlatoHealth. Obveščanje o biotehnologiji in kliničnih preskušanjih. Dostopite tukaj.

- vir: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :ima

- : je

- :ne

- :kje

- $GOR

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- dostop

- dostopen

- računovodstvo

- natančna

- Doseči

- čez

- dejavnosti

- dodano

- Dodatne

- Poleg tega

- Sprejem

- napredek

- napredovanje

- proti

- Usmerjanje

- dovoljene

- že

- Prav tako

- Čeprav

- vedno

- sredi

- zneski

- okrepiti

- an

- Analiza

- in

- Predvideno

- uporaba

- aplikacije

- pristop

- Arhitektura

- SE

- AS

- At

- izogniti

- Back-end

- ozadje

- pasovna širina

- BE

- postane

- med

- Poleg

- Bit

- Block

- podstavek

- povečanje

- Prinaša

- Gradi

- vendar

- by

- kabel

- kabli

- CAN

- zmogljivosti

- opravlja

- izzivi

- kanali

- čip

- čipi

- izbran

- okoliščinah

- stranke

- Ure

- Cloud

- računalništvo v oblaku

- Koda

- kombinirani

- združevanje

- Komunikacija

- dokončanje

- dokončanje

- komponenta

- deli

- celovito

- obsegajo

- računalništvo

- Skrb

- veznik

- povezane

- povezave

- VAROVANJE

- Razmislite

- premislekov

- dosledno

- se nadaljuje

- stalno

- prispevajo

- nadzor

- krmilnik

- Pretvorba

- Baker

- Core

- stroški

- izenačiti

- Tečaj

- izdelana

- ustvari

- Trenutna

- datum

- Datacenter

- Prvenec

- zamude

- poda

- Povpraševanje

- zahtevno

- zahteve

- upodobitev

- Oblikovanje

- oblikovalci

- modeli

- Odkrivanje

- naprave

- narekuje

- drugačen

- digitalni

- pridno

- prikazovalniki

- razdalja

- porazdeljena

- Ne

- podvojitev

- 2

- trajanje

- med

- vsak

- prej

- ekosistem

- Učinkovito

- učinkovito

- učinkovitosti

- učinkovite

- učinkovito

- prizadevanja

- pojav

- poudarja

- poudarjajo

- zaposleni

- zaposlovanja

- omogoča

- omogočanje

- zajema

- konec

- konec koncev

- zagotavlja

- Celotna

- Napaka

- napake

- Stopnjevanje

- Bistvo

- bistvena

- v bistvu

- Eter (ETH)

- Tudi

- Tudi vsak

- očitno

- razvija

- Primer

- izjemno

- izključena

- širi

- Širitev

- Pričakuje

- strokovnjak

- strokovno znanje

- razširiti

- razširitev

- zunanja

- pridobivanje

- oči

- Faktor

- dejavniki

- daleč

- hitreje

- Lastnosti

- Featuring

- Slika

- Najdi

- prva

- Prva generacija

- Pretok

- osredotočena

- sledili

- Odtis

- za

- oblikovanje

- Naprej

- FRAME

- iz

- nadalje

- generacija

- daje

- več

- skupina

- Skupine

- Pridelovanje

- strani

- Ravnanje

- visoka

- visokozmogljivo

- zelo

- Vendar

- HTML

- HTTPS

- nujno

- Izvajanje

- Pomembnost

- Pomembno

- izboljšalo

- in

- V drugi

- vključujejo

- Vključno

- narašča

- individualna

- industrijske

- vplivali

- inherentno

- inherentno

- sproži

- pobuda

- primer

- Integrira

- integracija

- celovitost

- vmesnik

- vmesniki

- Internet

- Interoperabilnost

- v

- intrinzično

- uvesti

- Predstavlja

- Predstavljamo

- vključuje

- IP

- IT

- ponovitve

- ITS

- sam

- jpg

- Lane

- Latenca

- plast

- plasti

- dolžina

- ravni

- vzvod

- Verjeten

- vrstica

- linije

- LINK

- Povezave

- v živo

- več

- nizka

- mac

- Izdelava

- upravljanje

- upravljanje

- max širine

- največja

- Maj ..

- pomeni

- Merjenje

- Mehanizem

- srednje

- Spomin

- Sporočilo

- Metoda

- Metode

- natančen

- minimalna

- zmanjšajo

- zmanjša

- minimiziranje

- modul

- Moduli

- več

- Najbolj

- morajo

- blizu

- Nimate

- omrežij

- Kljub temu

- št

- Upoštevajte

- zdaj

- Cilj

- of

- pogosto

- on

- ONE

- samo

- deluje

- optimizirana

- Optimizira

- Možnost

- or

- Ostalo

- več

- Splošni

- parov

- parametri

- zlasti

- pot

- računalniki

- za

- performance

- predstave

- fizično

- Fizično

- plinovod

- ključno

- platon

- Platonova podatkovna inteligenca

- PlatoData

- igra

- plus

- potencial

- moč

- vaje

- v prvi vrsti

- primarni

- Postopek

- obravnavati

- procesorji

- napredovanje

- napovedane

- zaščita

- protokol

- impulz

- Namen

- Potiskanje

- kakovost

- radio

- naključno

- območje

- Oceniti

- Cene

- dosežejo

- dosegli

- reakcija

- Reality

- prejeti

- prejema

- sprejem

- zmanjšanje

- zanesljiv

- ostanki

- upodabljanje

- zahteva

- omejeno

- rezultat

- robusten

- vloga

- Zakoreninjen

- tek

- Prilagodljivost

- Lestvica

- scenariji

- brezšivne

- drugi

- videl

- Segment

- občutljiva

- ločena

- služijo

- Storitev

- nastavite

- več

- deli

- Kratke Hlače

- shouldnt

- razstavni

- Signal

- bistveno

- Silicij

- Simulacija

- Velikosti

- So

- Rešitev

- rešitve

- razponi

- prednjači

- specifična

- posebej

- specifikacija

- hitrosti

- pomlad

- Stage

- standardna

- standardizacijo

- standardi

- shranjevanje

- strategije

- pretakanje

- kasneje

- precejšen

- uspeh

- taka

- primerna

- podpora

- Simbol

- sistem

- prilagojene

- meni

- tehnika

- tehnike

- Tehnologija

- kot

- da

- O

- njihove

- Tukaj.

- s tem

- zato

- te

- ta

- skozi

- Tako

- tick

- vezana

- čas

- krat

- do

- vrh

- tradicionalna

- Prometa

- prenos

- posredujejo

- Triple

- dva

- tipičen

- tipično

- neizogibno

- razumevanje

- zavezujeta

- Enota

- prihajajoče

- naprej

- uporabo

- uporabiti

- preko

- vizualizirati

- način..

- we

- kdaj

- ki

- medtem

- širše

- z

- v

- bi

- še

- zefirnet

- nič