V desetletju 2010 so prednosti Moorovega zakona začele propadati. Moorov zakon je navajal, da se gostota tranzistorjev vsaki dve leti podvoji, stroški računanja padejo za ustreznih 50 %. Sprememba Moorovega zakona je posledica povečane zasnove kompleksnosti razvoja tranzistorske strukture od planarnih naprav do Finfetov. Finfeti potrebujejo več vzorcev za litografijo, da dosežejo dimenzije naprav pod 20-nm vozlišča.

Na začetku tega desetletja so se potrebe po računalništvu močno povečale, predvsem zaradi širjenja podatkovnih središč in količine podatkov, ki se generirajo in obdelujejo. Pravzaprav se sprejetje umetne inteligence (AI) in tehnik, kot je strojno učenje (ML), zdaj uporabljajo za obdelavo vedno večjih podatkov in so privedle do tega, da so strežniki znatno povečali svojo računalniško zmogljivost.

Strežniki so dodali veliko več jeder CPU, integrirali večje GPU-je, ki se uporabljajo izključno za ML, ki se ne uporabljajo več za grafiko, in imajo vdelane pospeševalnike umetne inteligence po meri ASIC ali komplementarno obdelavo umetne inteligence, ki temelji na FPGA. Zgodnje zasnove čipov AI so bile izvedene z uporabo večjih monolitnih sistemov na čipu, nekateri med njimi so dosegli omejitev velikosti, ki jo določa namerilni križ, približno 700 mm2.

Na tej točki se zdi prava rešitev razčlenitev na manjši SoC ter različni čipleti za računalništvo in IO. Več izdelovalcev čipov, kot so Intel, AMD ali Xilinx, je izbralo to možnost za izdelke, ki bodo v proizvodnji. V odlični beli knjigi The Linley Group, »Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small«, je bilo prikazano, da ta možnost vodi do nižjih stroškov v primerjavi z monolitnimi SoC-ji zaradi vpliva večjih na donos.

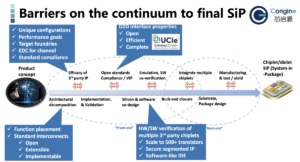

Glavni vpliv tega trenda na prodajalce IP je večinoma na funkcijah medsebojnega povezovanja, ki se uporabljajo za povezovanje SoC-jev in čipletov. Na tej točki (3. četrtletje 2021) se uporablja več protokolov, pri čemer industrija poskuša zgraditi formalizirane standarde za mnoge od njih.

Trenutni vodilni standardi D2D vključujejo i) napredno vmesniško vodilo (AIB, AIB2), ki ga je prvotno določil Intel, zdaj pa ponuja brezplačno uporabo, ii) pomnilnik visoke pasovne širine (HBM), kjer so matrice DRAM zložene ena na drugo na vrhu silikonskega vmesnika in so povezani z uporabo TSV-jev, iii) Podskupina Open Domain-Specific Architecture (ODSA), industrijska skupina, je definirala dva druga vmesnika, Bunch of Wires (BoW) in OpenHBI.

Heterogena zasnova čipletov nam omogoča, da ciljamo na različne aplikacije ali tržne segmente s spreminjanjem ali dodajanjem samo ustreznih čipletov, medtem ko preostali del sistema ostane nespremenjen. Novi razvoj bi lahko hitreje lansirali na trg z bistveno nižjimi naložbami, saj bo preoblikovanje vplivalo samo na substrat paketa, ki se uporablja za namestitev čipletov.

Na primer, računalniški čiplet je mogoče preoblikovati iz TSMC 5nm v TSMC 3nm za integracijo večjega predpomnilnika L1 ali zmogljivejših jeder CPE, medtem ko preostali del sistema ostane nespremenjen. Na nasprotnem koncu spektra je mogoče le čiplet, ki vključuje SerDes, preoblikovati za hitrejše hitrosti na novih procesnih vozliščih, ki ponujajo večjo pasovno širino IO za boljši položaj na trgu.

Intel PVC je odličen primer heterogene integracije (različni funkcionalni čipleti, procesorji, stikala itd.), ki bi jih lahko imenovali vertikalna integracija, ko ima isti proizvajalec čipov v lasti različne komponente čipletov (razen pomnilniških naprav).

Proizvajalci čipov, ki razvijajo sisteme na čipu za vrhunske aplikacije, kot so HPC, podatkovni centri, umetna inteligenca ali mreženje, bodo verjetno prvi uporabniki arhitektur čipletov. Posebne funkcije, kot so SRAM-ji za večji predpomnilnik L3 ali pospeševalniki AI, standardi Ethernet, PCIe ali CXL bi morali biti prvi kandidati za vmesnike za zasnove čipletov.

Ko bodo ti zgodnji uporabniki dokazali veljavnost heterogenih čipletov, ki izkoriščajo več različnih poslovnih modelov, in očitno izvedljivost proizvodnje za testiranje in pakiranje, bo ustvarjen ekosistem, ki je ključnega pomena za podporo tej novi tehnologiji. Na tej točki lahko pričakujemo širšo tržno sprejetje, ne le za visoko zmogljive aplikacije.

Lahko bi si predstavljali, da gredo lahko heterogeni izdelki še dlje, če bo proizvajalec čipov na trg lansiral sistem iz različnih čipletov, ki ciljajo na računalniško in IO funkcionalnost. Zaradi tega pristopa je konvergenca na protokolu D2D obvezna, saj prodajalec IP, ki ponuja čiplete z internim protokolom D2D, ni privlačen za industrijo.

Analogija temu je izgradnja SoC v 2000-ih, kjer polprevodniška podjetja preidejo na integracijo IP-jev različnih oblik, ki prihajajo iz različnih virov. Prodajalci IP iz leta 2000 bodo neizogibno postali prodajalci čipletov iz leta 2020. Za nekatere funkcije, kot so napredni SerDes ali kompleksni protokoli, kot so PCIe, Ethernet ali CXL, imajo ponudniki IP najboljše znanje in izkušnje za njihovo implementacijo na silicij.

Za zapleten IP IP, tudi če je bilo preverjanje simulacije izvedeno pred pošiljanjem strankam, morajo prodajalci potrditi IP na siliciju, da zagotovijo zmogljivost. Za digitalni IP je funkcijo mogoče implementirati v FPGA, ker je hitrejša in veliko cenejša od izdelave testnega čipa. Za IP mešanih signalov, kot je PHY, ki temelji na SerDes, prodajalci izberejo možnost Test Chip (TC), ki omogoča silicij, ki jim omogoča karakterizacijo IP v siliciju pred pošiljanjem stranki.

Čeprav čipplet ni le TC, ker bo pred uporabo na terenu obsežno preizkušen in kvalificiran, je količina postopnega dela, ki ga mora prodajalec opraviti za razvoj proizvodnega čipleta, veliko manjša. Z drugimi besedami, prodajalec IP-jev je v najboljšem položaju, da hitro izda čiplet, zgrajen iz lastnega IP-ja, in ponudi najboljši možni TTM ter zmanjša tveganje.

Poslovni model za heterogeno integracijo je v prid različnim čippletom, ki jih izdeluje ustrezen prodajalec IP (npr. ARM za čiplete CPU, ki temeljijo na ARM, Si-Five za čiplete, ki temeljijo na Risc-V, in Alphawave za čiplete SerDes visoke hitrosti), saj so lastniki Design IP.

Nič od tega ne preprečuje izdelovalcem čipov, da oblikujejo lastne čiplete in IP-je zasnove izvornih kompleksov, da zaščitijo svoje edinstvene arhitekture ali implementirajo doma narejene medsebojne povezave. Podobno kot pri SoC Design IP v 2000-ih bo odločitev o nakupu ali odločitvi za čiplete tehtana med zaščito osrednje kompetence in pridobitvijo nediferencialnih funkcij.

Videli smo, da je bila zgodovinska in sodobna poslovna rast Design IP od leta 2000 naprej podprta z nenehnim sprejemanjem zunanjih virov. Oba modela bosta obstajala sočasno (čiplet, zasnovan v podjetju ali s strani prodajalca IP), vendar je zgodovina pokazala, da odločitev o nakupu sčasoma prevzame odločitev.

Zdaj obstaja soglasje v industriji, da manična osredotočenost na doseganje Moorovega zakona ne velja več za napredna tehnološka vozlišča, npr. 7n in manj. Integracija čipov še vedno poteka, pri čemer je dodanih več tranzistorjev na kvadratni mm v vsakem novem tehnološkem vozlišču. Vendar pa tudi cena na tranzistor narašča z vsakim novim vozliščem.

Tehnologija Chiplet je ključna pobuda za spodbujanje povečane integracije za glavni SoC ob uporabi starejših vozlišč za druge funkcije. Ta hibridna strategija zmanjšuje tako stroške kot tveganje načrtovanja, povezano z integracijo drugih IP-jev za oblikovanje neposredno na glavni sistem na čipu.

IPnest meni, da bo ta trend imel dva glavna učinka v poslovanju vmesnikov IP, eden bo močna rast prihodkov D2D IP kmalu (2021-2025), drugi pa je ustvarjanje trga heterogenih čipletov za povečanje vrhunskega silicija. IP trg.

Pričakuje se, da bo ta trg sestavljen iz funkcij kompleksnih protokolov, kot so PCIe, CXL ali Ethernet. Prodajalci IP, ki ponujajo vmesnik IP, integriran v V/I SoC (USB, HDMI, DP, MIPI itd.), se lahko odločijo, da namesto tega dostavijo V/I čiplete.

Druge kategorije IP, na katere vpliva ta revolucija, bodo ponudniki IP prevajalnika pomnilnika SRAM za predpomnilnik L3. Po naravi se pričakuje, da se velikost predpomnilnika razlikuje glede na procesor. Kljub temu je oblikovanje čipov predpomnilnika L3 lahko način, da prodajalec IP poveča prihodke Design IP s ponudbo nove vrste izdelka.

Prav tako je mogoče pozitivno vplivati na kategorijo NVM IP, saj NVM IP ni več integriran v SoC, zasnovan na naprednih procesnih vozliščih. To bi bil način, da prodajalci NVM IP ustvarijo nove posle s ponudbo čipletov.

Menimo, da bodo čipleti za pospeševanje FPGA in AI nov vir prihodkov za proizvajalce čipov ASSP, vendar menimo, da jih ne moremo strogo uvrstiti med prodajalce IP.

Če bodo prodajalci vmesnikov IP glavni akterji v tej silicijevi revoluciji, bodo imele ključno vlogo tudi livarne silicija, ki obravnavajo najnaprednejša vozlišča, kot sta TSMC in Samsung. Mislimo, da livarne ne bodo oblikovale čipletov, vendar bi se lahko odločile, da bodo podprle prodajalce IP in jih spodbudile k oblikovanju čipletov, ki se bodo uporabljali s sistemi na čipu v 3 nm, kot to počnejo danes, ko podpirajo napredne prodajalce IP za trženje svojih vrhunskih SerDes. kot trdi IP v 7nm in 5nm.

Intelov nedavni prehod na 3rd Pričakuje se, da bo strankarska livarna izkoristila tudi IP-je tretjih oseb, pa tudi sprejemanje heterogenih čipletov s strani težkih proizvajalcev polprevodnikov. V tem primeru ni dvoma, da bodo Hyperscalars, kot so Microsoft, Amazon in Google, prav tako sprejeli arhitekture čipletov ... če pri sprejemanju čipletov ne bodo pred Intelom.

By Eric Esteve (doktorat) Analitik, lastnik IPnest

Delite to objavo prek: Vir: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- plin

- pospeševalniki

- Sprejetje

- Napredna tehnologija

- AI

- Dovoli

- Amazon

- AMD

- Analitik

- aplikacije

- Arhitektura

- ARM

- Umetna inteligenca

- Umetna inteligenca (AI)

- ASIC

- BEST

- izgradnjo

- Building

- Bunch

- avtobus

- poslovni

- poslovni model

- nakup

- klic

- kapaciteta

- spremenite

- čip

- čipi

- prihajajo

- Podjetja

- Izračunajte

- računalništvo

- Soglasje

- stroški

- Stranke, ki so

- datum

- dostavo

- Oblikovanje

- Razvoj

- naprave

- digitalni

- Zgodnje

- zgodnjih posvojiteljev

- ekosistem

- itd

- evolucija

- prva

- Osredotočite

- FPGA

- brezplačno

- funkcija

- Grafične kartice

- skupina

- Pridelovanje

- Rast

- visoka

- zgodovina

- Hiša

- HTTPS

- Hybrid

- vpliv

- Povečajte

- Industrija

- pobuda

- integracija

- Intel

- Intelligence

- naložbe

- IP

- IT

- vzdrževanje

- Ključne

- kosilo

- zakon

- vodi

- učenje

- Led

- Vzvod

- LINK

- strojno učenje

- velika

- avtomat

- Izdelava

- proizvodnja

- Tržna

- Microsoft

- ML

- Model

- mreženje

- Nov izdelek

- vozlišča

- ponudba

- ponujanje

- odprite

- Možnost

- Ostalo

- Lastnik

- embalaža

- Papir

- performance

- Izdelek

- proizvodnja

- Izdelki

- zaščito

- zaščita

- Cene

- preoblikovanje

- REST

- Tveganje

- Run

- Samsung

- polprevodnik

- Dostava

- Simulacija

- Velikosti

- standardi

- Strategija

- podpora

- Preklop

- sistem

- ciljna

- tehnike

- Tehnologija

- Test

- vrh

- us

- usb

- prodajalci

- Preverjanje

- Bela knjiga

- besede

- delo

- let

- donos