В течение десятилетия 2010 года преимущества закона Мура начали разваливаться. Закон Мура гласил, что плотность транзисторов удваивается каждые два года, а стоимость вычислений будет сокращаться на соответствующие 50%. Изменение закона Мура связано с увеличением сложности конструкции и эволюцией структуры транзисторов от плоских устройств до финфетов. Для литографии финфетам требуется многократное нанесение рисунка, чтобы размеры устройств были ниже 20-нм узлов.

В начале этого десятилетия потребности в вычислительных ресурсах резко возросли, в основном из-за распространения центров обработки данных и объема генерируемых и обрабатываемых данных. Фактически, внедрение искусственного интеллекта (ИИ) и таких методов, как машинное обучение (ML), теперь используется для обработки постоянно растущего объема данных и привело к тому, что серверы значительно увеличили свою вычислительную мощность.

На серверах добавлено гораздо больше ядер ЦП, интегрированы более крупные графические процессоры, используемые исключительно для машинного обучения, которые больше не используются для графики, а также встроены специальные ускорители искусственного интеллекта ASIC или дополнительная обработка искусственного интеллекта на основе FPGA. Ранние конструкции чипов искусственного интеллекта были реализованы с использованием более крупных монолитных SoC, некоторые из них достигали ограничения по размеру, налагаемого сеткой, около 700 мм.2.

На данный момент правильным решением кажется разделение на более мелкие SoC плюс различные вычислительные чиплеты и чипсеты ввода-вывода. Некоторые производители чипов, такие как Intel, AMD или Xilinx, выбрали этот вариант для продуктов, поступающих в производство. В превосходном информационном документе The Linley Group «Чиплеты быстро внедряются: почему большие чипы становятся маленькими» было показано, что этот вариант приводит к меньшим затратам по сравнению с монолитными SoC из-за влияния большего размера на доходность.

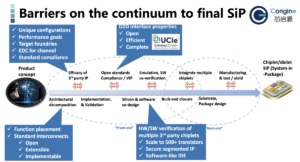

Основное влияние этой тенденции на поставщиков IP-технологий приходится главным образом на функции межсоединения, используемые для связи SoC и чиплетов. На данный момент (третий квартал 3 г.) используется несколько протоколов, и для многих из них отрасль пытается создать формализованные стандарты.

Текущие ведущие стандарты D2D включают в себя: i) расширенную интерфейсную шину (AIB, AIB2), первоначально определённую Intel, а теперь предлагающую бесплатное использование; ii) память с высокой пропускной способностью (HBM), в которой кристаллы DRAM уложены друг на друга поверх кремниевого переходника. и подключаются с помощью TSV. iii) Подгруппа открытой доменной архитектуры (ODSA), отраслевая группа, определила два других интерфейса: Bunch of Wires (BoW) и OpenHBI.

Гетерогенная конструкция микросхем позволяет нам ориентироваться на различные приложения или сегменты рынка, изменяя или добавляя только соответствующие микросхемы, сохраняя при этом остальную часть системы неизменной. Новые разработки можно будет вывести на рынок быстрее и со значительно меньшими инвестициями, поскольку изменение дизайна повлияет только на подложку корпуса, используемую для размещения чиплетов.

Например, вычислительный чиплет можно перепроектировать с 5-нм TSMC на 3-нм TSMC, чтобы интегрировать кэш L1 большего размера или более производительные ядра ЦП, сохранив при этом остальную часть системы без изменений. На противоположном конце спектра только чиплет, интегрирующий SerDes, может быть переработан для более высоких скоростей на новых технологических узлах, предлагая большую пропускную способность ввода-вывода для лучшего позиционирования на рынке.

Intel PVC — прекрасный пример гетерогенной интеграции (различные функциональные чиплеты, процессоры, коммутаторы и т. д.), которую мы могли бы назвать вертикальной интеграцией, когда один и тот же производитель микросхем владеет различными компонентами чиплетов (за исключением устройств памяти).

Производители чипов, разрабатывающие SoC для высокопроизводительных приложений, таких как высокопроизводительные вычисления, центры обработки данных, искусственный интеллект или сети, вероятно, будут одними из первых, кто внедрит архитектуру чиплетов. Конкретные функции, такие как SRAM для большего кэша L3 или ускорители искусственного интеллекта (стандарты Ethernet, PCIe или CXL), должны быть первыми кандидатами на интерфейсы для конструкций чиплетов.

Когда эти первые пользователи продемонстрируют обоснованность гетерогенных чиплетов, использующих множество различных бизнес-моделей, и, очевидно, осуществимость производства для тестирования и упаковки, будет создана экосистема, которая имеет решающее значение для поддержки этой новой технологии. На данный момент мы можем ожидать более широкого распространения на рынке, причем не только для высокопроизводительных приложений.

Мы могли бы представить, что гетерогенные продукты могут пойти дальше, если производитель микросхем выпустит на рынок систему, состоящую из различных чиплетов, предназначенных для вычислений и функций ввода-вывода. Такой подход делает конвергенцию на протоколе D2D обязательной, поскольку поставщик IP, предлагающий чиплеты с собственным протоколом D2D, не привлекателен для отрасли.

Аналогией этому является создание SoC в 2000-х годах, когда полупроводниковые компании перешли к интеграции различных IP-проектов, полученных из разных источников. Поставщики IP 2000-х годов неизбежно станут поставщиками чиплетов 2020-х годов. Для некоторых функций, таких как расширенные SerDes или сложные протоколы, такие как PCIe, Ethernet или CXL, поставщики IP обладают лучшими ноу-хау для реализации их на микросхемах.

Для сложных IP-проектов, даже если проверка моделирования была проведена перед отправкой клиентам, поставщики должны проверить IP-адрес на кристалле, чтобы гарантировать производительность. Для цифрового IP эту функцию можно реализовать в FPGA, поскольку это быстрее и гораздо дешевле, чем создание тестового чипа. Для IP-сигналов со смешанными сигналами, таких как PHY на основе SerDes, поставщики выбирают опцию Test Chip (TC), позволяющую определить характеристики IP в кристалле перед отправкой клиенту.

Несмотря на то, что чиплет — это не просто TC, поскольку он будет тщательно протестирован и сертифицирован перед использованием в полевых условиях, объем дополнительной работы, которую предстоит проделать поставщику для разработки серийного чиплета, гораздо меньше. Другими словами, поставщик IP имеет наилучшие возможности быстро выпустить чиплет, созданный на основе его собственного IP, предложить наилучший возможный TTM и минимизировать риск.

Бизнес-модель гетерогенной интеграции предполагает, что различные чиплеты производятся соответствующим поставщиком IP (например, ARM для чиплетов ЦП на базе ARM, Si-Five для вычислительных чиплетов на базе Risc-V и Alphawave для высокоскоростных чиплетов SerDes), поскольку они являются владельцами Design IP.

Ничто из этого не мешает производителям микросхем разрабатывать свои собственные чиплеты и исходные комплексные IP-проекты для защиты своей уникальной архитектуры или реализовывать межсоединения собственного производства. Подобно SoC Design IP в 2000-х годах, решение о покупке или покупке чиплетов будет взвешиваться между защитой основных компетенций и поиском недифференцирующих функций.

Мы увидели, что исторический и современный рост бизнеса в области интеллектуальной собственности в области дизайна, начиная с 2000-х годов, поддерживается постоянным внедрением внешних источников. Обе модели будут сосуществовать (чипсет, разработанный собственными силами или поставщиком IP), но история показала, что решение о покупке в конечном итоге принимает решение.

В настоящее время в отрасли существует консенсус в отношении того, что маниакальная ориентация на достижение закона Мура больше не актуальна для узлов передовых технологий, например. 7 нм и ниже. Интеграция микросхем все еще происходит: в каждом новом технологическом узле на каждый квадратный миллиметр добавляется больше транзисторов. Однако стоимость транзистора также растет с каждым новым узлом.

Технология чиплетов — это ключевая инициатива, направленная на повышение интеграции основного SoC при использовании старых узлов для других функций. Эта гибридная стратегия снижает как стоимость, так и риск проектирования, связанный с интеграцией других IP-проектов непосредственно в основную SoC.

IPnest полагает, что эта тенденция будет иметь два основных эффекта в бизнесе интерфейсного IP: одним из них станет сильный рост доходов от D2D IP в ближайшее время (2021-2025 гг.), а другим — создание рынка гетерогенных чиплетов для расширения рынка высокопроизводительных кремниевых устройств. Рынок ИП.

Ожидается, что этот рынок будет состоять из сложных функций протоколов, таких как PCIe, CXL или Ethernet. Поставщики IP-интерфейсов, поставляющие IP-интерфейсы, интегрированные в SoC ввода-вывода (USB, HDMI, DP, MIPI и т. д.), могут вместо этого решить поставлять чиплеты ввода-вывода.

Другими категориями IP, на которые повлияет эта революция, будут поставщики IP-адресов компиляторов памяти SRAM для кэша L3. По своей природе ожидается, что размер кэша будет варьироваться в зависимости от процессора. Тем не менее, разработка чиплета кэша L3 может стать для поставщика IP способом увеличить доходы от Design IP за счет предложения нового типа продукта.

Кроме того, это может оказать положительное влияние на категорию NVM IP, поскольку NVM IP больше не интегрированы в SoC, разработанные на узлах расширенных процессов. Для поставщиков NVM IP это будет возможность создать новый бизнес, предлагая чиплеты.

Мы считаем, что чиплеты-ускорители FPGA и искусственного интеллекта станут новым источником доходов для производителей чипов ASSP, но не думаем, что их можно строго причислять к поставщикам IP.

Если поставщики IP-интерфейсов станут основными участниками этой кремниевой революции, ключевую роль также будут играть производители полупроводников, работающие с самыми передовыми узлами, такими как TSMC и Samsung. Мы не думаем, что литейные заводы будут разрабатывать чиплеты, но они могут принять решение поддержать поставщиков IP и подтолкнуть их к разработке чиплетов для использования с SoC на 3-нм техпроцессе, как они делают сегодня, поддерживая передовых поставщиков IP для продвижения на рынок своих высококлассных SerDes. как жесткий IP в 7 нм и 5 нм.

Недавний переход Intel на 3rd Ожидается, что заводы-изготовители также будут использовать сторонние IP-адреса, а также внедрение гетерогенных чиплетов полупроводниковыми тяжеловесами. В этом случае нет никаких сомнений в том, что гиперскаляры, такие как Microsoft, Amazon и Google, также примут архитектуру чиплетов… если они не опередят Intel в принятии чиплетов.

By Эрик Эстев Кандидат наук, аналитик, владелец IPnest

Поделитесь этим постом через: Источник: https://semiwiki.com/semiconductor-services/ipnest/303790-chiplet-are-you-ready-for-next-semiconductor-revolution/

- 2021

- ускоритель

- ускорители

- Принятие

- Передовые технологии

- AI

- Позволяющий

- Amazon

- AMD

- аналитик

- Приложения

- архитектура

- ARM

- искусственный интеллект

- Искусственный интеллект (AI)

- Основныеоперации

- ЛУЧШЕЕ

- строить

- Строительство

- Группа

- автобус

- бизнес

- Бизнес-модель

- купить

- призывают

- Пропускная способность

- изменение

- чип

- чипсы

- приход

- Компании

- Вычисление

- вычисление

- Консенсус

- Расходы

- Клиенты

- данным

- доставки

- Проект

- развивать

- Устройства

- Интернет

- Рано

- ранние участники

- экосистема

- и т.д

- эволюция

- Во-первых,

- Фокус

- FPGA

- Бесплатно

- функция

- Графические процессоры

- группы

- Рост

- Рост

- High

- история

- Вилла / Бунгало

- HTTPS

- Гибридный

- Влияние

- Увеличение

- промышленность

- Инициатива

- интеграции.

- Intel

- Интеллекта

- инвестиций

- IP

- IT

- хранение

- Основные

- запуск

- закон

- ведущий

- изучение

- привело

- Кредитное плечо

- LINK

- обучение с помощью машины

- основной

- производитель

- Создание

- производство

- рынок

- Microsoft

- ML

- модель

- сетей

- новый продукт

- узлы

- предлагают

- предлагающий

- открытый

- Опция

- Другое

- владелец

- коробок

- бумага & картон

- производительность

- Продукт

- Производство

- Продукция

- для защиты

- защиту

- Стоимость

- офиса

- ОТДЫХ

- Снижение

- Run

- Samsung

- полупроводник

- Доставка и оплата

- моделирование

- Размер

- стандартов

- Стратегия

- поддержка

- Коммутатор

- система

- цель

- снижения вреда

- Технологии

- тестXNUMX

- топ

- us

- USB

- поставщики

- проверка

- технический документ

- слова

- Работа

- лет

- Уступать