Эксперты за столом: Semiconductor Engineering сели, чтобы обсудить пути развития памяти во все более гетерогенных системах с Фрэнком Ферро, директором группы по управлению продуктами в компании Каденция; Стивен Ву, коллега и выдающийся изобретатель Rambus; Чонсин Юн, технолог памяти в Сименс ЭДА; Рэнди Уайт, менеджер программы решений для памяти в Кейсайт; и Франк Ширрмайстер, вице-президент по решениям и развитию бизнеса в Артерис. Ниже приводятся выдержки из этого разговора. Первую часть этого обсуждения можно найти здесь.

![[Слева направо]: Фрэнк Ферро, Каденс; Стивен Ву, Rambus; Чонсин Юн, Siemens EDA; Рэнди Уайт, Keysight; и Фрэнк Ширмейстер, Arteris.](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[Слева направо]: Фрэнк Ферро, Каденс; Стивен Ву, Rambus; Чонсин Юн, Siemens EDA; Рэнди Уайт, Keysight; и Фрэнк Ширмейстер, Arteris

СЭ: Поскольку мы боремся с искусственным интеллектом и машинным обучением и требованиями к мощности, какие конфигурации необходимо переосмыслить? Увидим ли мы отход от архитектуры фон Неймана?

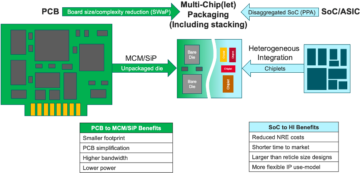

Woo: Что касается системных архитектур, в отрасли происходит раздвоение. Традиционные приложения, являющиеся доминирующими «рабочими лошадками», которые мы запускаем в облаке на серверах на базе x86, не исчезнут. Программное обеспечение создавалось и развивалось десятилетиями, и его хорошая работа будет зависеть от этой архитектуры. Напротив, AI/ML — это новый класс. Люди переосмыслили архитектуру и создали процессоры, ориентированные на конкретную предметную область. Мы видим, что около двух третей энергии тратится на простое перемещение данных между процессором и устройством HBM, и только около трети тратится на фактический доступ к битам в ядрах DRAM. Перемещение данных теперь стало намного сложнее и дороже. Мы не собираемся избавляться от памяти. Нам это нужно, потому что наборы данных становятся больше. Итак, вопрос в том, «Каков правильный путь в дальнейшем?» Было много дискуссий по поводу стекирования. Если бы мы взяли эту память и поместили ее непосредственно поверх процессора, она сделала бы для вас две вещи. Во-первых, пропускная способность сегодня ограничена береговой линией или периметром чипа. Вот куда идут вводы/выводы. Но если бы вы установили его непосредственно поверх процессора, теперь вы могли бы использовать всю площадь чипа для распределенных межсоединений, а также получить большую пропускную способность самой памяти, и она могла бы передаваться непосредственно в процессор. Ссылки становятся намного короче, а энергоэффективность, вероятно, возрастает примерно в 5-6 раз. Во-вторых, пропускная способность, которую вы можете получить за счет соединения массива большей площади с памятью, также увеличивается в несколько целочисленных коэффициентов. Совместное выполнение этих двух действий может обеспечить большую пропускную способность и сделать ее более энергоэффективной. Индустрия развивается в соответствии с потребностями, и это определенно один из способов, которым мы увидим, как системы памяти начнут развиваться в будущем, чтобы стать более энергоэффективными и обеспечить большую пропускную способность.

Железо: Когда я впервые начал работать над HBM примерно в 2016 году, некоторые из наиболее продвинутых клиентов спросили, можно ли его объединить. Они уже давно рассматривают вопрос о том, как разместить DRAM сверху, потому что есть явные преимущества. На физическом уровне PHY становится практически незначительным, что экономит много энергии и эффективности. Но теперь у вас есть процессор мощностью несколько 100 Вт с памятью поверх него. Память не выдерживает жары. Вероятно, это самое слабое звено в тепловой цепочке, что создает еще одну проблему. Плюсы есть, но им еще предстоит придумать, как бороться с термическими потоками. Сейчас появилось больше стимулов для продвижения этого типа архитектуры, потому что она действительно экономит в целом с точки зрения производительности и мощности, а также повышает эффективность вычислений. Но есть некоторые проблемы физического проектирования, которые необходимо решить. Как говорил Стив, мы видим появление всевозможных архитектур. Я полностью согласен с тем, что архитектуры GPU/CPU никуда не денутся, они по-прежнему будут доминировать. В то же время каждая компания на планете пытается придумать лучшую мышеловку для своего ИИ. Мы видим встроенную SRAM и комбинацию памяти с высокой пропускной способностью. В наши дни LPDDR довольно активно поднимает вопрос о том, как использовать преимущества LPDDR в центрах обработки данных из-за мощности. Мы даже видели, как GDDR используется в некоторых приложениях вывода ИИ, а также во всех старых системах памяти. Сейчас они пытаются втиснуть как можно больше модулей DDR5 на занимаемую площадь. Я видел каждую архитектуру, о которой вы только можете подумать, будь то DDR, HBM, GDDR или другие. Это зависит от ядра вашего процессора с точки зрения общей добавленной стоимости, а затем от того, как вы можете преодолеть свою конкретную архитектуру. Система памяти, которая идет вместе с ним, позволяет вам формировать свой процессор и архитектуру памяти в зависимости от того, что доступно.

Юнь: Другой вопрос – энергонезависимость. Например, если ИИ приходится иметь дело с интервалом включения питания между запуском ИИ на основе Интернета вещей, тогда нам нужно много выключений и включений, и вся эта информация для обучения ИИ должна вращаться снова и снова. Если у нас есть какое-то решение, в котором мы можем хранить эти веса в чипе, чтобы нам не приходилось постоянно перемещаться вперед и назад для получения одного и того же веса, то это будет значительная экономия энергии, особенно для искусственного интеллекта на основе Интернета вещей. Будет другое решение, которое поможет этим требованиям власти.

Ширмейстер: Что мне кажется интересным с точки зрения NoC, так это то, что вам нужно оптимизировать эти пути от процессора, проходящего через NoC, до доступа к интерфейсу памяти с контроллером, потенциально проходящим через UCIe, чтобы передать чиплет другому чиплету, в котором затем есть память. это. Дело не в том, что архитектуры фон Неймана мертвы. Но сейчас существует очень много вариантов, в зависимости от рабочей нагрузки, которую вы хотите вычислить. Их необходимо рассматривать в контексте памяти, а память — это только один аспект. Откуда вы берете данные из локальности данных, как они устроены в этой DRAM? Мы работаем над всеми этими вещами, такими как анализ производительности памяти и последующая оптимизация архитектуры системы на ее основе. Это стимулирует множество инноваций в новой архитектуре, о которых я никогда не думал, когда учился в университете, изучая фон Неймана. На другом конце есть такие вещи, как сетки. Сейчас существует гораздо больше архитектур, которые необходимо рассмотреть, и это обусловлено пропускной способностью памяти, вычислительными возможностями и т. д., а не растет такими же темпами.

Белый: Существует тенденция использования дезагрегированных вычислений или распределенных вычислений, а это означает, что архитектору необходимо иметь в своем распоряжении больше инструментов. Иерархия памяти расширилась. Включена семантика, а также CXL и различные гибридные запоминающие устройства, доступные во флэш-памяти и в DRAM. Параллельное приложение к дата-центру — автомобильная промышленность. В автомобилестроении этот датчик всегда взаимодействовал с ЭБУ (электронными блоками управления). Я очарован тем, как это превратилось в центр обработки данных. Перенесемся вперед: сегодня у нас есть распределенные вычислительные узлы, называемые контроллерами домена. Это то же самое. Он пытается решить, что, возможно, мощность не так уж важна, потому что масштаб компьютеров не такой большой, но задержка, безусловно, имеет большое значение в автомобилестроении. ADAS требует сверхвысокой пропускной способности, и у вас есть другие компромиссы. Кроме того, у вас больше механических датчиков, но аналогичные ограничения в центре обработки данных. У вас есть холодное хранилище, которому не обязательно иметь низкую задержку, а также другие приложения с высокой пропускной способностью. Интересно видеть, насколько изменились инструменты и возможности архитектора. Отрасль проделала действительно хорошую работу по реагированию, и все мы предлагаем различные решения, которые пополняют рынок.

СЭ: Как развивались инструменты проектирования памяти?

Ширмейстер: Когда в 90-е годы я начал работать со своими первыми чипами, наиболее часто используемым системным инструментом был Excel. С тех пор я всегда надеялся, что в какой-то момент он может сломаться в том, что мы делаем на уровне системы, памяти, анализе пропускной способности и так далее. Это сильно повлияло на мои команды. В то время это была очень продвинутая вещь. Но, по мнению Рэнди, теперь некоторые сложные вещи необходимо моделировать с таким уровнем точности, который раньше был невозможен без вычислений. В качестве примера можно предположить, что определенная задержка при доступе к DRAM может привести к неправильным архитектурным решениям и потенциально неправильному проектированию архитектур передачи данных на кристалле. Обратная сторона тоже верна. Если вы всегда предполагаете худший вариант, вы перепроектируете архитектуру. Наличие инструментов, выполняющих DRAM и анализ производительности, а также наличие подходящих моделей для контроллеров позволяет архитектору моделировать все это — это увлекательная среда. Инструмент системного уровня действительно может стать реальностью, потому что некоторые динамические воздействия вы больше не можете выполнять в Excel, потому что вам нужно их моделировать — особенно когда вы добавляете комплексный интерфейс с характеристиками PHY, а затем уровень связи. такие характеристики, как проверка правильности всех действий и возможная повторная отправка данных. Отсутствие такого моделирования приведет к неоптимальной архитектуре.

Железо: Первым шагом в большинстве оценок, которые мы проводим, является предоставление им испытательного стенда памяти, чтобы начать оценивать эффективность DRAM. Это огромный шаг, даже если делать такие простые вещи, как запуск локальных инструментов для моделирования DRAM, а затем переходить к полномасштабному моделированию. Мы видим, что все больше клиентов просят о таком типе моделирования. Убедиться, что эффективность вашей DRAM находится на уровне 90, является очень важным первым шагом в любой оценке.

Woo: Популярность инструментов полного системного моделирования частично объясняется тем, что DRAM стали намного сложнее. Сейчас очень сложно справиться с некоторыми из этих сложных рабочих нагрузок, используя простые инструменты, такие как Excel. Если вы посмотрите на таблицу данных DRAM в 90-х годах, эти таблицы данных были примерно на 40 страницах. Теперь это сотни страниц. Это просто говорит о сложности устройства для обеспечения высокой пропускной способности. Вы связываете это с тем фактом, что память является таким фактором стоимости системы, а также пропускной способности и задержки, связанных с производительностью процессора. Это также большой фактор мощности, поэтому теперь вам нужно моделировать на гораздо более детальном уровне. Что касается потока инструментов, системные архитекторы понимают, что память является важным фактором. Таким образом, инструменты должны быть более сложными, и они должны очень хорошо взаимодействовать с другими инструментами, чтобы системный архитектор мог получить лучшее глобальное представление о том, что происходит, особенно о том, как память влияет на систему.

Юнь: По мере того, как мы переходим в эпоху искусственного интеллекта, используется множество многоядерных систем, но мы не знаем, какие данные куда передаются. Он также работает более параллельно с чипом. Объем памяти намного больше. Если мы используем ИИ типа ChatGPT, то для обработки данных для моделей требуется около 350 МБ данных, что представляет собой огромный объем данных только для веса, а фактический ввод/вывод намного больше. Такое увеличение объема необходимых данных означает, что существует множество вероятностных эффектов, которых мы раньше не видели. Это чрезвычайно сложный тест, чтобы увидеть все ошибки, связанные с таким большим объемом памяти. А ECC используется везде, даже в SRAM, которая традиционно не использовала ECC, но сейчас это очень распространено для крупнейших систем. Тестирование всего этого очень сложно и должно поддерживаться решениями EDA для проверки всех этих различных условий.

СЭ: С какими проблемами ежедневно сталкиваются инженерные команды?

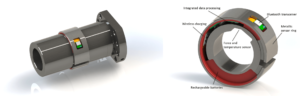

Белый: В любой день вы найдете меня в лаборатории. Я закатываю рукава, и у меня пачкаются руки: тыкаешь провода, паяешь и еще много чего. Я много думаю о пост-кремниевой валидации. Мы говорили о первых инструментах моделирования и встроенных инструментах — BiST и тому подобном. В конце концов, перед отправкой мы хотим провести некоторую форму проверки системы или тестирования на уровне устройства. Мы говорили о том, как преодолеть стену памяти. Мы размещаем память вместе, HBM и тому подобное. Если мы посмотрим на эволюцию упаковочных технологий, то увидим, что мы начали с упаковки со свинцом. Они не очень хорошо обеспечивали целостность сигнала. Десятилетия спустя мы перешли к оптимизированной целостности сигнала, например, к массивам шариковых решеток (BGA). Мы не могли получить к этому доступ, а это означало, что вы не могли это проверить. Итак, мы придумали концепцию, называемую интерпозером устройства — интерпозером BGA — и это позволило нам объединить специальное приспособление, которое маршрутизирует сигналы. Тогда мы могли бы подключить его к испытательному оборудованию. Перенесемся в сегодняшний день: теперь у нас есть HBM и чиплеты. Как мне разместить приспособление между кремниевой прокладкой? Мы не можем, и это борьба. Это вызов, который не дает мне спать по ночам. Как мы проводим анализ отказов в полевых условиях совместно с OEM-клиентом или заказчиком системы, если они не достигают эффективности в 90 %? В ссылке больше ошибок, не могут правильно инициализироваться, не работает обучение. Это проблема целостности системы?

Ширмейстер: Разве вы не предпочли бы делать это дома с помощью виртуального интерфейса, чем идти в лабораторию? Разве ответ не состоит в том, что аналитика встроена в чип? С помощью чиплетов мы интегрируем все еще глубже. Вставить туда паяльник на самом деле невозможно, поэтому должен быть способ встроенной аналитики. У нас та же проблема с NoC. Люди смотрят на NoC, вы отправляете данные, а потом они исчезают. Нам нужна аналитика, чтобы люди могли выполнять отладку, и это распространяется на уровень производства, чтобы вы, наконец, могли работать из дома и делать все это на основе аналитики микросхем.

Железо: Особенно с памятью с высокой пропускной способностью, вы не можете физически попасть туда. Когда мы лицензируем PHY, у нас также есть продукт, который соответствует этому, так что вы можете увидеть каждый из этих 1,024 битов. Вы можете начать чтение и запись DRAM с помощью этого инструмента, поэтому вам не придется физически туда входить. Мне нравится идея с интерпозером. Во время тестирования мы вынимаем некоторые контакты из интерпозера, чего нельзя сделать в системе. Попасть в эти 3D-системы действительно непросто. Даже с точки зрения потока инструментов проектирования кажется, что большинство компаний используют свой собственный индивидуальный поток для многих из этих 2.5D-инструментов. Мы начинаем разрабатывать более стандартизированный способ построения 2.5D-системы, начиная с целостности сигнала, мощности и всего потока.

Белый: Несмотря на то, что все движется вперед, я надеюсь, что мы сможем поддерживать тот же уровень точности. Я состою в группе соответствия форм-фактору UCIe. Я пытаюсь определить, как охарактеризовать заведомо исправный кубик, золотой кубик. В конце концов, это займет гораздо больше времени, но мы найдем золотую середину между необходимой нам производительностью и точностью тестирования и встроенной гибкостью.

Ширмейстер: Если я рассмотрю чиплеты и их внедрение в более открытую производственную среду, тестирование станет одной из самых серьезных проблем на пути к правильной работе. Если я большая компания и контролирую все ее стороны, то я могу соответствующим образом ограничить ситуацию, чтобы тестирование и т. д. стало возможным. Если я хочу следовать лозунгу UCIe о том, что UCI отделяется от PCI всего на одну букву, и представляю себе будущее, в котором сборка UCIe станет, с точки зрения производства, такой же, как слоты PCI в современном ПК, тогда аспекты тестирования для этого действительно будут испытывающий. Нам нужно найти решение. Нам предстоит много работы.

Статьи по теме

Будущее памяти (Часть 1 округления выше)

От попыток решить проблемы с теплом и питанием до роли CXL и UCIe — будущее открывает для памяти ряд возможностей.

- SEO-контент и PR-распределение. Получите усиление сегодня.

- PlatoData.Network Вертикальный генеративный ИИ. Расширьте возможности себя. Доступ здесь.

- ПлатонАйСтрим. Интеллект Web3. Расширение знаний. Доступ здесь.

- ПлатонЭСГ. Углерод, чистые технологии, Энергия, Окружающая среда, Солнечная, Управление отходами. Доступ здесь.

- ПлатонЗдоровье. Биотехнологии и клинические исследования. Доступ здесь.

- Источник: https://semiengineering.com/rethinking-memory/

- :имеет

- :является

- :нет

- :куда

- $UP

- 1

- 2016

- 3d

- 40

- a

- О нас

- выше

- доступ

- доступа

- точность

- фактического соединения

- на самом деле

- АДА

- Добавить

- адрес

- Принятие

- продвинутый

- плюс

- Преимущества

- снова

- AI

- AI обучение

- AI / ML

- Все

- разрешено

- позволяет

- причислены

- всегда

- количество

- an

- анализ

- аналитика

- и

- Другой

- ответ

- любой

- больше не

- откуда угодно

- Применение

- Приложения

- надлежащим образом

- Архитекторы

- архитектура

- МЫ

- ПЛОЩАДЬ

- около

- расположены

- массив

- AS

- спрашивающий

- внешний вид

- аспекты

- сборка

- предполагать

- At

- попытки

- автомобильный

- доступен

- прочь

- назад

- Плохой

- мяч

- Пропускная способность

- бар

- основанный

- в основном

- основа

- BE

- , так как:

- становиться

- становится

- было

- до

- не являетесь

- Преимущества

- ЛУЧШЕЕ

- Лучшая

- между

- большой

- больший

- Немного

- Ломать

- приносить

- строить

- построенный

- бизнес

- развитие бизнеса

- но

- by

- Каденция

- под названием

- пришел

- CAN

- Может получить

- возможности

- случаев

- Центр

- определенный

- конечно

- цепь

- вызов

- проблемы

- сложные

- характеристика

- охарактеризовать

- контроль

- чип

- чипсы

- класс

- Очистить

- облако

- холодный

- хранение в холодильнике

- комбинации

- как

- приход

- Общий

- Компании

- Компания

- комплекс

- сложность

- Соответствие закону

- сложный

- Вычисление

- компьютеры

- вычисление

- сама концепция

- Условия

- Свяжитесь

- считается

- ограничения

- контекст

- контраст

- контроль

- контроллер

- Разговор

- Основные

- исправить

- Цена

- может

- Пара

- ЦП

- создает

- клиент

- Клиенты

- данным

- Центр обработки данных

- Наборы данных

- день

- дня в день

- Дней

- мертвый

- сделка

- десятилетия

- решения

- определенно

- запросы

- в зависимости

- зависит

- Проект

- проектирование

- подробный

- Развитие

- устройство

- Умереть

- различный

- трудный

- непосредственно

- директор

- обсуждение

- распоряжение

- Выдающийся

- распределенный

- распределенных вычислений

- do

- приносит

- не

- дело

- домен

- доминирующий

- сделанный

- Dont

- вниз

- управляемый

- водитель

- в течение

- динамический

- Рано

- эффекты

- затрат

- эффективный

- Электронный

- конец

- энергетика

- Проект и

- Весь

- Окружающая среда

- Оборудование

- Эпоха

- ошибки

- особенно

- Эфир (ETH)

- оценка

- оценки

- Даже

- со временем

- Каждая

- многое

- везде

- эволюция

- развивается

- эволюционировали

- эволюционирует

- пример

- Excel

- расширенный

- дорогим

- продолжается

- экстремальный

- чрезвычайно

- Глаза

- Face

- факт

- фактор

- Ошибка

- увлекательный

- БЫСТРО

- выполнимый

- человек

- верность

- поле

- фигура

- в заключение

- Найдите

- First

- Flash

- Трансформируемость

- кувырок

- поток

- следующим образом

- след

- Что касается

- форма

- вперед

- вперед

- найденный

- откровенный

- от

- полный

- далее

- будущее

- получить

- получающий

- Дайте

- данный

- Глобальный

- Go

- идет

- будет

- Golden

- ушел

- хорошо

- хорошая работа

- есть

- сетка

- группы

- Рост

- было

- Управляемость

- Руки

- счастливый

- Есть

- имеющий

- помощь

- иерархия

- High

- имеет

- Главная

- надежды

- Как

- How To

- HTML

- HTTPS

- огромный

- Сотни

- Гибридный

- i

- идея

- if

- картина

- влияние

- воздействуя

- важную

- улучшать

- in

- стимул

- включены

- неверно

- Увеличение

- все больше и больше

- individual

- промышленность

- информация

- Инновации

- внутри

- интегрировать

- целостность

- межсоединения

- Интерфейс

- в

- с участием

- вопрос

- вопросы

- IT

- ЕГО

- саму трезвость

- работа

- всего

- Знать

- известный

- лаборатория

- большой

- больше

- крупнейших

- Задержка

- новее

- слой

- вести

- изучение

- письмо

- уровень

- Лицензия

- такое как

- Ограниченный

- LINK

- связи

- локальным

- посмотреть

- искать

- серия

- много

- Низкий

- поддерживать

- сделать

- Создание

- управление

- менеджер

- производство

- многих

- рынок

- макс-ширина

- может быть

- me

- означает

- означает,

- механический

- средний

- памяти

- Память

- может быть

- Модели

- БОЛЕЕ

- самых

- двигаться

- переехал

- движение

- перемещение

- много

- my

- Необходимость

- потребности

- никогда

- Новые

- ночь

- узлы

- сейчас

- номер

- of

- от

- Старый

- on

- ONE

- только

- открытый

- Возможности

- Оптимизировать

- оптимизированный

- оптимизирующий

- Опция

- Опции

- or

- заказ

- Другое

- Другое

- внешний

- общий

- Преодолеть

- собственный

- пакеты

- коробок

- страниц

- Параллельные

- часть

- особый

- pass

- путь

- пути

- PC

- Люди

- выполнять

- производительность

- перспектива

- физический

- Физически

- штифты

- планета

- Платон

- Платон Интеллектуальные данные

- ПлатонДанные

- Точка

- возможное

- потенциально

- мощностью

- президент

- предварительно

- вероятно

- Проблема

- процессор

- процессоры

- Продукт

- Управление продуктом

- Производство

- FitPartner™

- правильный

- должным образом

- обеспечивать

- положил

- вопрос

- вполне

- привлечение

- Обменный курс

- скорее

- Reading

- на самом деле

- Связанный

- полагаться

- обязательный

- требуется

- решение

- ответ

- результат

- избавиться

- правую

- Рост

- роли

- Катить

- Run

- Бег

- то же

- Сохранить

- экономия

- поговорка

- Шкала

- Во-вторых

- посмотреть

- видя

- кажется

- видел

- семантика

- полупроводник

- Отправить

- датчик

- датчик

- серверы

- несколько

- простыни

- сдвиг

- судно

- сторона

- Стороны

- Сименс

- сигнал

- сигналы

- кремний

- аналогичный

- просто

- моделирование

- моделирование

- с

- одинарной

- Размер

- слоты

- So

- Software

- Решение

- Решения

- некоторые

- сложный

- Говорит

- особый

- потраченный

- выжимать

- стек

- сложены

- штабелирования

- нормированный

- точка зрения

- Начало

- и политические лидеры

- Начало

- Шаг

- Стив

- Стивен

- По-прежнему

- диск

- магазин

- Бороться

- такие

- Поддержанный

- Убедитесь

- система

- системы

- ТАБЛИЦЫ

- взять

- Говорить

- команды

- технолог

- Технологии

- terms

- тестXNUMX

- Тестирование

- тестов

- чем

- который

- Ассоциация

- Будущее

- их

- Их

- тогда

- Там.

- тепловой

- Эти

- они

- задача

- вещи

- think

- В третьих

- этой

- те

- мысль

- Через

- время

- в

- сегодня

- вместе

- инструментом

- инструменты

- топ

- ПОЛНОСТЬЮ

- компромиссные

- традиционный

- Традиционно

- Обучение

- перевозки

- тенденция

- правда

- пытается

- два

- две трети

- напишите

- понимать

- единиц

- Университет

- us

- использование

- используемый

- через

- Проверка

- ценностное

- изменения

- различный

- очень

- вице

- вице-президент

- Вид

- Виртуальный

- из

- ходьба

- стена

- хотеть

- законопроект

- Путь..

- we

- вес

- ЧТО Ж

- были

- Что

- любой

- когда

- будь то

- который

- в то время как

- белый

- все

- зачем

- будете

- без

- свататься

- Работа

- работать из дома

- работает

- Наихудший

- письмо

- являетесь

- ВАШЕ

- зефирнет