Banias Labs este o companie de semiconductori care dezvoltă soluții de infrastructură pentru comunicații de ultimă generație. Piața sa țintă este piața infrastructurii de calcul de înaltă performanță, inclusiv centru de date hiperscale, rețele, AI, modul optic și SoC-uri de comutare Ethernet pentru proiecte de calcul de înaltă performanță emergente. Aceste SoC-uri necesită design Ethernet de mare viteză și soluții cu latență scăzută pentru a oferi performanțe sporite ale sistemului și pentru a accelera timpul de lansare pe piață. Compania a dezvoltat un SoC DSP optic pe tehnologie de proces de 5 nm pentru a răspunde cerințelor acestei piețe.

![]()

Un SoC DSP optic este un tip specializat de sistem pe cip (SoC) conceput pentru a fi utilizat în sisteme de comunicații optice de mare viteză. În plus față de DSP, SoC DSP optic include de obicei blocuri IP de interfață de mare viteză, cum ar fi Ethernet PHY IP, PCIe IP și controlere de memorie DDR. Aceste tipuri de SoC permit transferuri de date de mare viteză la latențe scăzute pentru procesarea semnalului în timp real. De asemenea, sunt proiectate pentru a minimiza consumul de energie, făcându-le ideale pentru aplicații care necesită o funcționare eficientă cu probleme termice reduse. Odată cu avantajele vin și provocările. Cerințele specializate ale sistemelor de comunicații optice fac proiectarea unui SoC DSP optic mai dificilă decât proiectarea unui SoC obișnuit.

Provocări de implementare

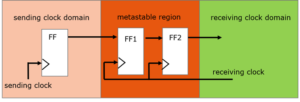

Provocările gravitează în jurul complexității designului, cerințelor stricte de putere și performanță și nevoia de a îndeplini diverse standarde din industrie. Integrarea mai multor blocuri IP, inclusiv procesorul DSP, Ethernet PHY IP și alte blocuri personalizate necesită o proiectare și validare atentă. Interfețele suplimentare de mare viteză, cum ar fi PCIe și DDR, sporesc și mai mult complexitatea designului. Interfețele de mare viteză și blocurile IP multiple din sistem pot crea distorsiuni ale semnalului, diafonie și interferențe electromagnetice, care pot afecta performanța și fiabilitatea sistemului. Analiza și optimizarea integrității semnalului și a puterii trebuie efectuate la începutul ciclului de proiectare pentru a se asigura că sistemul își poate îndeplini cerințele de performanță și fiabilitate. În cele din urmă, îndeplinirea cerințelor de time-to-market poate fi o provocare. Piața infrastructurii de calcul de înaltă performanță evoluează rapid, iar echipele de dezvoltare SoC trebuie să-și livreze rapid design-urile pentru a rămâne în fața concurenței.

A ajunge la First Pass Silicon Success

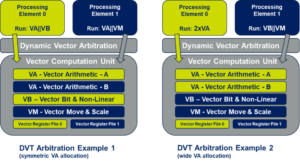

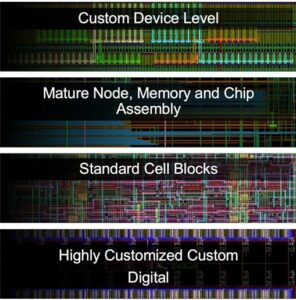

Depășirea provocărilor menționate mai sus necesită o abordare cuprinzătoare. Una dintre componentele critice ale soluțiilor de înaltă performanță, cu latență scăzută este Ethernet PHY IP. Ethernet PHY IP este responsabil pentru interfața stratului fizic dintre SoC și rețeaua Ethernet. IP-ul trebuie să accepte interfețe Ethernet de mare viteză, inclusiv 10G, 25G, 40G, 50G, 100G, 200G, 400G și 800G și să ofere o latență redusă și un consum redus de energie. În plus, IP-ul trebuie să accepte diverse standarde, inclusiv IEEE 802.3 și Ethernet Alliance. O altă componentă importantă este suita de design EDA. Suita de design EDA trebuie să ofere o soluție cuprinzătoare pentru proiectarea și verificarea SoC, inclusiv optimizarea puterii, analiza performanței, optimizarea suprafeței și analiza randamentului. În măsura în care, suita de design EDA include funcții avansate, cum ar fi inteligența artificială (AI) și învățarea automată (ML), cu atât mai bine pentru o productivitate sporită și timp de lansare pe piață redus.

Synopsys accelerează succesul First Pass Silicon

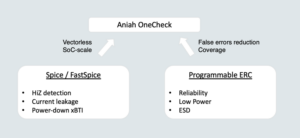

Synopsys oferă soluții care abordează provocările unice ale dezvoltării SoC-urilor pentru piața infrastructurii de calcul de înaltă performanță. Compania oferă o soluție IP cuprinzătoare care include un studiu de fezabilitate a rutării, linii directoare pentru ambalarea substratului, modele de integritate a semnalului și a puterii și analiză amănunțită a diafoniei. Acest lucru este imperativ pentru a aborda provocările privind integritatea semnalului și a puterii cu care se confruntă atunci când se dezvoltă un SoC DSP optic. 112G Ethernet PHY IP de la Synopsys oferă o latență scăzută, lungimi de acoperire flexibile și maturitate pe tehnologia de proces de 5 nm, făcându-l o soluție ideală pentru centre de date hiperscale, rețele, AI, module optic și SoC-uri de comutare Ethernet. În plus, Synopsys oferă o suită de design EDA care oferă rezultate de înaltă calitate cu putere, performanță, suprafață și randament optimizate. EDA Design Suite de la Synopsys, bazată pe inteligență artificială, oferă soluții pentru a crește performanța sistemului și pentru a accelera timpul de lansare pe piață, făcându-l o componentă esențială a unei soluții de succes pentru piața infrastructurii de calcul de înaltă performanță.

Rezumat

Synopsys oferă soluții de înaltă performanță, cu latență scăzută, care accelerează dezvoltarea switch-urilor Ethernet avansate și a SoC-urilor de rețea. Pentru a afla mai multe despre soluțiile IP cuprinzătoare ale Synopsys, suita lor cuprinzătoare de design EDA și suita EDA îmbunătățită AI, vizitați paginile următoare.

Soluțiile IP complete ale Synopsys

Suita EDA cuprinzătoare a Synopsys

Suita de design EDA bazată pe inteligență artificială a Synopsys

Citeste si:

Sisteme cu matrițe multiple: cea mai mare întrerupere în calcul de ani de zile

Hrăniți foamea tot mai mare de lățime de bandă cu Ethernet de mare viteză

Distribuie această postare prin:

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- Platoblockchain. Web3 Metaverse Intelligence. Cunoștințe amplificate. Accesați Aici.

- Mintând viitorul cu Adryenn Ashley. Accesați Aici.

- Sursa: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :are

- :este

- a

- Despre Noi

- mai sus

- accelera

- Accelerează

- plus

- Suplimentar

- În plus,

- adresa

- avansat

- Avantajele

- înainte

- AI

- Alianță

- de asemenea

- an

- analiză

- și

- O alta

- aplicatii

- abordare

- SUNT

- ZONĂ

- în jurul

- artificial

- inteligență artificială

- Inteligența artificială (AI)

- AS

- At

- Lățime de bandă

- BE

- Mai bine

- între

- Cea mai mare

- Blocuri

- a stimula

- CAN

- atent

- Centru

- provocări

- provocare

- cum

- Comunicare

- Comunicații

- companie

- concurs

- complexitate

- component

- componente

- cuprinzător

- tehnica de calcul

- consum

- crea

- critic

- personalizat

- ciclu

- de date

- Data Center

- livra

- Oferă

- Amenajări

- proiectat

- proiect

- modele

- dezvoltat

- în curs de dezvoltare

- Dezvoltare

- dezvoltă

- Ruptură

- Devreme

- eficient

- șmirghel

- permite

- sporită

- asigura

- esenţial

- evoluție

- cu care se confruntă

- FAST

- DESCRIERE

- În cele din urmă

- First

- flexibil

- următor

- Pentru

- din

- mai mult

- În creştere

- orientări

- performanta ridicata

- de înaltă calitate

- HTML

- HTTPS

- foame

- ideal

- IEEE

- imagine

- Impactul

- imperativ

- important

- in

- include

- Inclusiv

- a crescut

- industrie

- standardele industriei

- Infrastructură

- integrare

- integritate

- Inteligență

- interfaţă

- interfeţe

- IP

- probleme de

- IT

- ESTE

- Labs

- Latență

- strat

- AFLAȚI

- învăţare

- Jos

- maşină

- masina de învățare

- face

- Efectuarea

- Piață

- scadență

- max-width

- Întâlni

- Reuniunea

- Memorie

- menționat

- ML

- Modele

- modul

- mai mult

- multiplu

- Nevoie

- reţea

- rețele

- generație următoare

- of

- promoții

- on

- ONE

- operaţie

- optimizare

- optimizate

- Altele

- propriu

- ambalaje

- trece

- performanță

- fizic

- Plato

- Informații despre date Platon

- PlatoData

- Post

- putere

- proces

- prelucrare

- procesor

- productivitate

- furniza

- furnizează

- repede

- repede

- ajunge

- Citeste

- în timp real

- Redus

- regulat

- încredere

- necesita

- Cerinţe

- Necesită

- responsabil

- REZULTATE

- Risc

- semiconductor

- Semnal

- Siliciu

- soluţie

- soluţii

- de specialitate

- standarde

- şedere

- Studiu

- succes

- de succes

- astfel de

- suită

- a sustine

- Intrerupator

- sistem

- sisteme

- Ţintă

- echipe

- Tehnologia

- decât

- acea

- lor

- Lor

- termic

- Acestea

- ei

- acest

- la

- de asemenea

- Transferuri

- Tipuri

- tipic

- unic

- utilizare

- validare

- diverse

- verificarea

- de

- Vizita

- care

- cu

- Randament

- Ta

- zephyrnet