Mai devreme am scris pe blog despre Verificare funcțională IC și ASIC, așa că astăzi este timpul să completăm asta cu starea verificării funcționale FPGA. Wilson Research Group a compilat un raport FPGA la fiecare doi ani din 2018, așa că este a treia oară când se concentrează pe acest segment de design. La 5.8 miliarde de dolari, piața FPGA este considerabilă și se estimează că va crește la 8.1 miliarde de dolari până în 2025. FPGA-urile au început în 1984 cu o capacitate limitată de porți, iar acum au crescut pentru a include milioane de porți, procesoare și protocoale de date standardizate.

Aplicațiile cu volum redus beneficiază de NRE a dispozitivelor FPGA, iar inginerii își pot prototipa rapid design-urile prin verificarea și validarea rapidă. FPGA-urile includ acum procesoare, cum ar fi: Xilinx Zynq UltraSCALE, Intel Stratix, Microcip SmartFusion. Dintre cei 980 de participanți la studiul de verificare funcțională, stilurile de design FPGA și SoC programabile FPGA sunt cele mai populare.

Pe măsură ce dimensiunea FPGA-urilor a crescut recent, șansa unei lansări de producție fără erori a scăzut la doar 17%, ceea ce este chiar mai rău decât 30% din proiectele IC și ASIC pentru primul siliciu corect. În mod clar, avem nevoie de o verificare funcțională mai bună pentru sistemele FPGA complexe.

Tipurile de bug-uri găsite în producție se împart în mai multe categorii:

- 53% – logic sau funcțional

- 31% – Firmware

- 29% – Cronometrare

- 28% – Timing, cale prea lent

- 21% – Timing, cale prea rapidă

- 18% – Interfață cu semnal mixt

- 9% – Caracteristică de siguranță

- 8% – Funcție de securitate

Privind cea mai mare categorie de defecțiuni, logice sau funcționale, există cinci cauze fundamentale.

În mare parte, proiectele FGPA nu s-au finalizat la timp, din cauza încă o dată de dimensiunea mai mare a sistemelor, complexitatea logicii și chiar metodele de verificare utilizate.

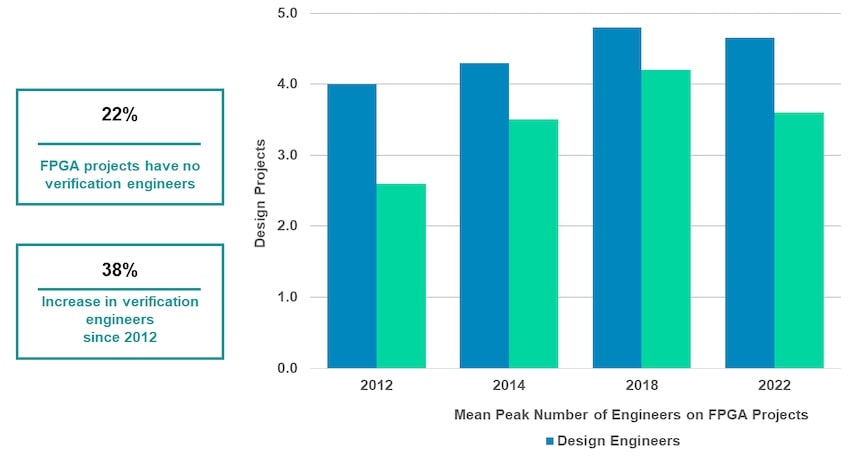

Inginerii dintr-o echipă FPGA pot avea titluri distincte, cum ar fi inginer proiectant sau inginer de verificare, dar în 22% dintre proiecte nu au existat ingineri de verificare – ceea ce înseamnă că inginerii de proiectare au îndeplinit sarcini duble și și-au verificat propria IP. În ultimii 10 ani, a existat o creștere cu 38% a numărului de ingineri de verificare pe un proiect FPGA, așa că acesta este un progres către o producție fără erori.

Inginerii de verificare din proiectele FPGA și-au petrecut cea mai mare parte a timpului pe sarcini de depanare la 47%:

- 47% – Depanare

- 19% – Crearea testului și rularea simulării

- 17% – Dezvoltare testbench

- 11% – Planificarea testelor

- 6% – Altele

Numărul de procesoare încorporate a crescut constant de-a lungul timpului, astfel încât 65% dintre modelele FPGA au unul sau mai multe nuclee de procesor acum, crescând cantitatea de verificare între interfețele hardware și software; și gestionarea rețelelor pe cip.

Procesorul mereu popular RISC-V este încorporat în 22% din FPGA, iar acceleratoarele AI sunt folosite în 23% din proiecte. Există 3-4 un număr mediu de domenii de ceas utilizate pe FPGA-uri și necesită simulări de sincronizare la nivel de poartă pentru verificare, plus utilizarea instrumentelor statice Clock Domain Crossing (CDC) pentru verificare.

Caracteristicile de securitate sunt adăugate la 49% din proiectele FPGA pentru a păstra date sensibile, plus 42% din proiectele FPGA respectă standardele sau liniile directoare critice pentru siguranță. Pe SemiWiki am scris adesea pe blog ISO 26262 și DO-254 standardele. Eforturile de proiectare pentru Siguranța Funcțională (FuSa) necesită între 25% și 50% din timpul total al proiectului.

Primele trei limbi de verificare sunt VHDL, SystemVerilog și Verilog; dar observați și salturile recente în limbajele Python și C/C++.

Cele mai populare metodologii FPGA și biblioteci de teste de bază sunt: Accellera UVM, OSVVM și UVVM. Bazat pe Python cocotb a fost chiar adăugată ca categorie nouă pentru 2022.

Limbile de aserție sunt conduse de SystemVerilog Assertions (SVA) la 45%, urmate de Accellera Open Verification Library (OVL) la 13% și PSL la 11%. Proiectele FPGA pot combina VHDL pentru design RTL împreună cu SVA pentru afirmații.

Verificarea formală a proprietăților este în creștere în cadrul proiectelor FPGA, mai ales că mai multe aplicații formale automate au fost introduse de furnizorii EDA.

Abordările de verificare bazate pe simulare din ultimii 10 ani arată o adoptare constantă, enumerate în ordinea relevanței: acoperire cod, acoperire funcțională, afirmații, aleatoriu constrâns.

Rezumat

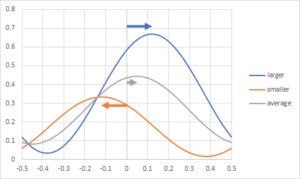

Numărul scăzut de 17% fără erori pentru proiectele FPGA în 2022 care a intrat în producție a fost cel mai surprinzător număr pentru mine, deoarece efortul de a rechema sau reprograma un dispozitiv în domeniu este costisitor și necesită timp de corectat. O abordare mai robustă de verificare funcțională ar trebui să conducă la mai puține scăpări de erori în producție, iar împărțirea participanților la studiu în două grupuri arată beneficiul.

Citiți integral Hârtie albă de 18 pagini aici.

Bloguri înrudite

Distribuie această postare prin:

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- Platoblockchain. Web3 Metaverse Intelligence. Cunoștințe amplificate. Accesați Aici.

- Sursa: https://semiwiki.com/eda/324651-the-state-of-fpga-functional-verification/

- 1

- 10

- 2018

- 2022

- a

- Despre Noi

- acceleratoare

- adăugat

- adera

- Adoptare

- AI

- între

- sumă

- și

- aplicatii

- abordare

- abordari

- Apps

- asic

- Automat

- in medie

- fiind

- beneficia

- Mai bine

- între

- Miliard

- Bug

- gandaci

- Capacitate

- categorii

- Categorii

- Provoca

- cauzată

- cauze

- CDC

- șansă

- control

- clar

- Ceas

- cod

- combina

- Completă

- complex

- complexitate

- acoperire

- Crearea

- critic

- de date

- Amenajări

- modele

- dispozitiv

- Dispozitive

- FĂCUT

- distinct

- domeniu

- domenii

- scăzut

- efort

- Eforturile

- încorporat

- inginer

- inginerii

- mai ales

- Chiar

- Fiecare

- scump

- Eșec

- Cădea

- DESCRIERE

- camp

- First

- concentrat

- a urmat

- formal

- găsit

- fpga

- din

- funcțional

- porti

- grup

- Grupului

- Crește

- În creştere

- crescut

- orientări

- Piese metalice

- deţine

- HTML

- HTTPS

- in

- include

- Crește

- a crescut

- crescând

- Intel

- interfeţe

- introdus

- IP

- IT

- salturi

- Limbă

- mai mare

- cea mai mare

- conduce

- Led

- biblioteci

- Bibliotecă

- Limitat

- listat

- Jos

- făcut

- de conducere

- Piață

- max-width

- sens

- metodologii

- Metode

- milioane

- mai mult

- cele mai multe

- Cel mai popular

- Nevoie

- rețele

- Nou

- număr

- ONE

- deschide

- comandă

- global

- propriu

- Hârtie

- participanţi

- trecut

- cale

- Plato

- Informații despre date Platon

- PlatoData

- la care se adauga

- Popular

- Post

- procesor

- procesoare

- producere

- Progres

- proiect

- Proiecte

- proprietate

- protocoale

- prototip

- Piton

- repede

- aleator

- recent

- recent

- eliberaţi

- relevanţa

- raportează

- necesita

- cercetare

- grup de cercetare

- robust

- rădăcină

- rotund

- funcţionare

- Siguranţă

- securitate

- segment

- sensibil

- câteva

- să

- Arăta

- Emisiuni

- Siemens

- Siliciu

- întrucât

- considerabil

- Mărimea

- So

- Software

- viteză

- uzat

- standarde

- început

- Stat

- constant

- Studiu

- surprinzător

- sisteme

- Lua

- sarcini

- echipă

- tehnici de

- test

- Statul

- lor

- Al treilea

- trei

- timp

- sincronizare

- titluri

- la

- astăzi

- de asemenea

- Unelte

- top

- față de

- Tipuri

- utilizare

- furnizori

- Verificare

- verificat

- verificarea

- de

- volum

- care

- alb

- hartie alba

- Wilson

- ani

- zephyrnet