Rezistivitatea cuprului depinde de structura sa cristalină, volumul golului, limitele de granule și nepotrivirea interfeței materialului, care devine mai semnificativă la scară mai mică. Formarea firelor de cupru (Cu) se realizează în mod tradițional prin gravarea unui model de șanț în dioxid de siliciu cu joasă k, folosind un proces de gravare a șanțului și, ulterior, umplerea șanțului cu Cu printr-un flux de damaschin. Din păcate, această metodă produce structuri multicristaline cu limite semnificative ale granulelor și goluri, ceea ce crește rezistența firului de Cu. Un material de căptușeală TaN foarte rezistiv este, de asemenea, utilizat în acest proces pentru a preveni difuzia Cu în timpul procesului de recoacere a damaschinului.

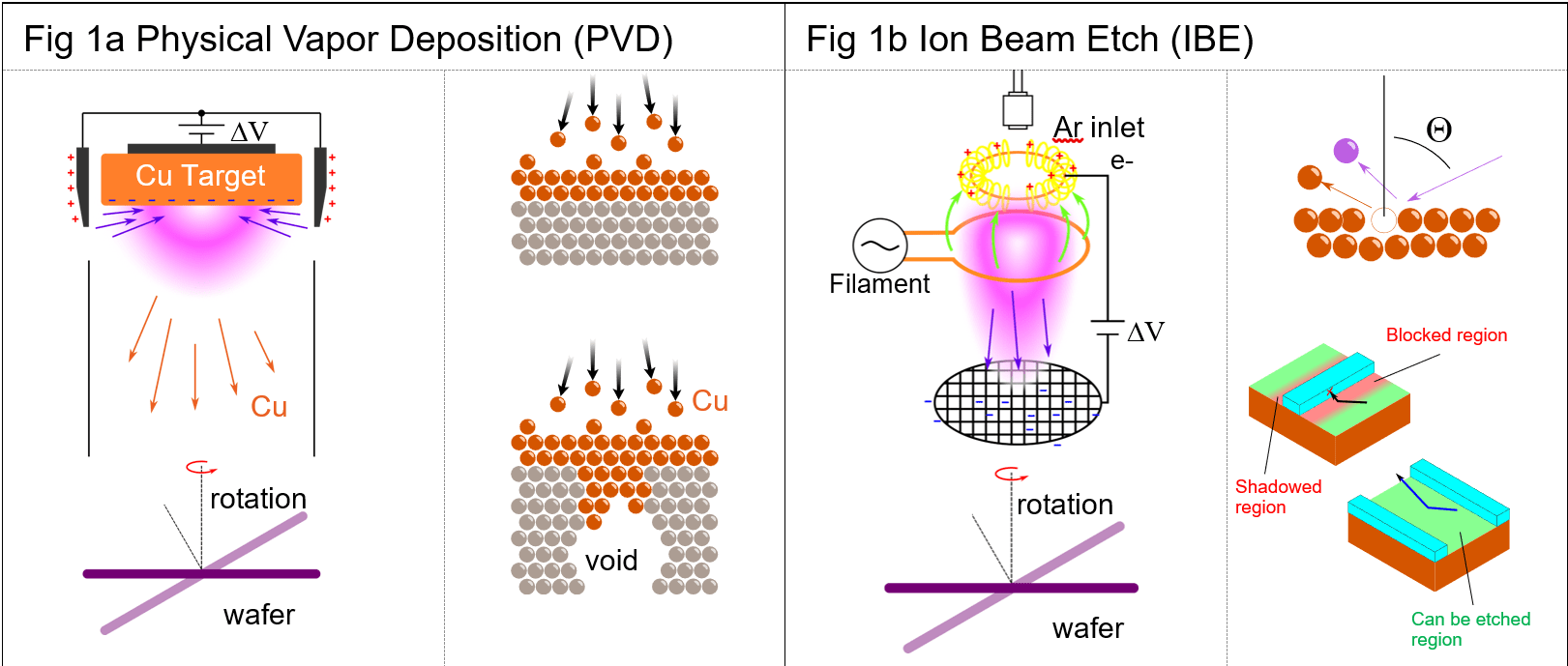

Depunerea fizică în vapori (PVD) poate fi utilizată pentru a depune cuprul la energii cinetice mari (între 10 și 100 eV), formând structuri monocristaline dense, cu rezistență scăzută. Un dezavantaj al PVD este că depunerea PVD are o linie de vedere răspândită și poate fi depusă uniform doar pe suprafețe plane. Nu poate fi folosit pentru umplerea găurilor sau a șanțurilor adânci (figura 1a). Pentru a forma forme izolate de sârmă, un strat uniform de Cu trebuie depus pe o suprafață plană și apoi gravat fizic de fascicule de ioni. Cu nu formează compuși volatili cu gazele reactive, așa că nu poate fi utilizat un proces de gravare cu ioni reactivi. Ionii de Ar accelerați creați în timpul gravarii cu fascicul ionic (IBE) pot elimina Cu dacă unghiul de incident este foarte mare. Din păcate, regiunile gravabile vor fi limitate din cauza efectelor de umbră ale măștii. Figura 1b arată regiunile (în roșu) în care materialul nu poate fi gravat atunci când masca este perpendiculară pe fasciculul de ioni de intrare. Acest eșec de gravare apare din cauza umbririi sau blocării căii atomului ejectat. Când masca este paralelă cu calea ionului, toate regiunile nemascate pot fi gravate. Astfel, gravarea cu fascicul de ioni este limitată la măști în formă de linie de gravare de lungimi arbitrar lungi.

![]()

Fig. 1: (1a) Depunere fizică în vapori (PVD); (1b) Ion Beam Etch (IBE).

Etapele procesului și procesul de fabricație virtuală

Pentru a înțelege efectul depunerii și gravării asupra rezistenței liniei, acum modelăm procesele de gravare PVD și IBE utilizând funcțiile de depunere și gravare cu vizibilitate SEMulator3D. PVD a fost reprodus folosind un proces de depunere a vizibilității unghiulare de 30 de grade în SEMulator3D, care modelează cu exactitate natura aleatorie a atomilor de Cu ejectați în timpul bombardamentului cu ioni AR. IBE a fost reprodus în model folosind o gravare a vizibilității cu o răspândire unghiulară de 2 grade și un unghi polar de înclinare de 60 de grade, pentru a reflecta comportamentul ionilor accelerați în grilă cu divergența fasciculului scurt. Se presupune că ambele plachete au rotație liberă. Alți pași ai procesului au fost ajustați în procesul de fabricație virtuală pentru a se adapta constrângerilor IBE și PVD. Figura 2 afișează aceeași structură creată folosind atât o umplutură de Cu damaschin (figura 2a) cât și un proces PVD/IBE (figura 2b). Au fost incluși pași suplimentari de proces pentru a încorpora anumite limitări ale PVD/IBE și pentru a crea forma echivalentă pentru structurile noastre terminale dorite.

![]()

Fig. 2: (2a) Fabricarea sârmei de Cu de umplutură de damaschin; (2b) Fabricarea firului PVD/IBE Cu.

Apoi demonstrăm că o celulă de circuit SRAM echivalentă de 16 nm poate fi fabricată cu fire PVD/IBE respectând aceste limitări. Deoarece toate straturile metalice de deasupra capătului de mijloc al liniei sunt fabricate dintr-o suprafață plană, acest lucru îl face un candidat ideal pentru firele PVD/IBE, spre deosebire de topologiile complexe de interconectare văzute într-un dispozitiv finFET. Figura 3 prezintă structura izolată a fiecărui strat de metal și pașii necesari pentru a crea o structură finFET cu trei straturi metalice folosind PVD/IBE.

![]()

Fig. 3: (3a) FinFET MEOL de 16 nm și 3 straturi metalice; (3b) Fabricarea pas cu pas a stratului metalic prin PVD/IBE.

Rezistența rezultate și concluzie

Măsurăm apoi rezistența electrică a firelor de la stratul de metal cel mai de sus până la canalele finFET P și N, atât pentru fluxul de damaschin, cât și pentru depunerea fizică de vapori. Figura 4 prezintă punctul de început și punctul final al măsurării rezistenței la canalele P și N (toate celelalte materiale izolatoare sunt transparente). Pentru a compensa rezistența interfeței dintre căptușeala TaN și firul de cupru, rezistivitatea cuprului a fost crescută prin utilizarea unei constante de dezintegrare exponențială de 1 nm în funcție de distanța cea mai apropiată de interfața TaN. Deoarece o depunere de Cu umplutură de damaschin nu este de așteptat să fie complet cristalină, rezistivitatea Cu a fost crescută cu 50%. Procesul de cupru PVD/IBE nu folosește o căptușeală TaN, astfel încât funcția de dezintegrare exponențială nu a fost aplicată, iar rezistivitatea în vrac a cuprului a fost utilizată în acest model. În figura 4 este inclus un tabel de rezistivitate care compară un flux de damaschin față de PVD.

![]()

Fig. 4: Punctul de început și punctul final al măsurării rezistenței la canalele P și N.

Valorile rezistenței calculate din modelul nostru afirmă că putem obține o scădere cu 67% a rezistenței utilizând metoda de fabricație IBE/PVD în comparație cu o gravare convențională în șanț urmată de depunere de damaschin. Acest lucru se întâmplă deoarece nu este necesară nicio căptușeală TaN în IBE/PVD și există o rezistivitate CU mai mică în timpul acestui proces. Rezultatele noastre indică faptul că îmbunătățirile rezistivității pot fi obținute prin utilizarea IBE/PVD în comparație cu umplutura de damaschin în timpul formării liniilor metalice, cu prețul unui proces de fabricație mai complex.

Timothy Yang

(toate postările)

Timothy Yang este inginer de aplicații software la Coventor, o companie de cercetare Lam. Lucrează în dezvoltarea de procese, integrare și aplicații de îmbunătățire a randamentului, cu expertiză în tehnologii de memorie. Înainte de a lucra la Coventor, Yang a lucrat la Tokyo Electron, dezvoltând scheme de gravare, tehnici de îmbunătățire a modelelor post litografie, controlul fluxului de proces pentru aplicații de modelare SADP și SAQP și tehnologie EUV și litografia de imersie fotorezistentă. Yang a primit o diplomă de licență în fizică de la UCLA, o diplomă de master în Știința Materialelor de la Institutul de Tehnologie Chiba și un doctorat. licențiat în Știința Materialelor de la Universitatea Tohoku.

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- Platoblockchain. Web3 Metaverse Intelligence. Cunoștințe amplificate. Accesați Aici.

- Mintând viitorul cu Adryenn Ashley. Accesați Aici.

- Sursa: https://semiengineering.com/a-deposition-and-etch-technique-to-lower-resistance-of-semiconductor-metal-lines/

- :are

- :este

- ][p

- 1

- 10

- 100

- a

- mai sus

- accelerat

- găzdui

- precis

- Obține

- realizat

- Suplimentar

- Ajustat

- TOATE

- Toate mesajele

- și

- Unghiular

- aplicatii

- aplicat

- AR

- SUNT

- AS

- asumat

- At

- atom

- BE

- Grindă

- devine

- fost

- între

- limitele

- by

- calculată

- CAN

- candidat

- nu poti

- sigur

- canale

- companie

- comparație

- compararea

- complex

- constant

- constrângeri

- Control

- convențional

- Cupru

- A costat

- crea

- a creat

- Cristal

- de date

- scădea

- adânc

- Grad

- demonstra

- depinde de

- depozit

- depus

- dorit

- în curs de dezvoltare

- Dezvoltare

- dispozitiv

- difuziune

- afișează

- distanţă

- Divergență

- jos

- în timpul

- fiecare

- efect

- efecte

- oricare

- inginer

- Echivalent

- EV

- de aşteptat

- expertiză

- exponențială

- Eșec

- Figura

- umple

- plat

- debit

- a urmat

- Pentru

- formă

- formare

- formulare

- Gratuit

- din

- complet

- funcţie

- funcții

- Grilă

- Avea

- he

- Înalt

- extrem de

- găuri

- HTTPS

- idee

- imersiune

- îmbunătățire

- îmbunătățiri

- in

- incident

- inclus

- Intrare

- incorpora

- a crescut

- Creșteri

- indica

- Institut

- integrare

- interfaţă

- izolat

- IT

- ESTE

- jpg

- Cotonogi

- strat

- straturi

- limitări

- Limitat

- Linie

- linii

- Lung

- Jos

- FACE

- masca

- Măști

- material

- Materiale

- max-width

- măsura

- Memorie

- metal

- metodă

- De mijloc

- model

- Modele

- mai mult

- Natură

- necesar

- necesar

- of

- on

- comandă

- Altele

- al nostru

- Paralel

- cale

- Model

- fizic

- Fizic

- Fizică

- Plato

- Informații despre date Platon

- PlatoData

- Punct

- polar

- Post

- postări

- împiedica

- anterior

- proces

- procese

- aleator

- primit

- Roșu

- reflecta

- regiuni

- scoate

- cercetare

- Rezistență

- REZULTATE

- s

- acelaşi

- cântare

- scheme

- Ştiinţă

- semiconductor

- Modela

- profilat

- forme

- Emisiuni

- Vedere

- semnificativ

- Siliciu

- întrucât

- singur

- mai mici

- So

- Software

- răspândire

- Pornire

- Stat

- Pas

- paşi

- structura

- Ulterior

- Suprafață

- tabel

- tehnici de

- Tehnologii

- Tehnologia

- acea

- Acestea

- trei

- miniatura

- la

- Tokyo

- cel mai de sus

- tradiţional

- transparent

- UCLAs

- înţelege

- universitate

- utilizare

- utilizat

- utilizate

- Valori

- de

- Virtual

- vizibilitate

- volatil

- volum

- vs

- care

- în timp ce

- voi

- Fire de sârmă

- cu

- Apartamente

- a lucrat

- fabrică

- Randament

- zephyrnet