De la debutul din anii 1980 cu rețele LAN partajate de 10 Mbps prin cabluri coaxiale, Ethernet a cunoscut progrese consistente, acum cu potențialul de a suporta viteze de până la 1.6 Tbps. Această progresie a permis Ethernet să deservească o gamă mai largă de aplicații, cum ar fi streaming live, rețele de acces radio și control industrial, subliniind importanța transferului de pachete fiabil și a calității serviciului. Având în vedere că lățimea de bandă actuală a internetului se ridică la ~500 Tbps, există o cerere din ce în ce mai mare pentru gestionarea îmbunătățită a traficului back-end în interiorul centrului de date. Deși serverele individuale nu funcționează încă la niveluri de Terabit pe secundă, traficul total al centrului de date se apropie de această scară, determinând grupul IEEE 802.3dj să întreprindă eforturi de standardizare și necesitând controlere Ethernet robuste și SerDes pentru a gestiona fluxul de date în expansiune. În mijlocul acestui fundal al cererilor în creștere, comunicarea interprocesor împinge deja la aceste viteze.

Comunicarea interprocesor este vârful de lance a nevoii de rate 1.6T cu latență minimă. În timp ce dispozitivele individuale sunt limitate de capacitățile lor inerente de procesare și de dimensiunea cipului, combinarea cipurilor poate extinde semnificativ aceste capacități. Se așteaptă ca prima generație de aplicații să fie urmată de conexiuni switch-to-switch în interiorul centrului de date, permițând punerea în comun a procesoarelor și memoriei de înaltă performanță, sporind scalabilitatea și eficiența în cloud computing.

Inițiativa IEEE 802.3dj: Avansarea standardelor Ethernet pentru interoperabilitatea de 1.6 Tbps

Respectarea eforturilor de standardizare în evoluție este esențială pentru interoperabilitatea fără întreruperi a ecosistemelor. Grupul IEEE 802.3dj este în proces de formulare a viitorului standard Ethernet, care cuprinde straturi fizice și parametri de management pentru viteze de la 200G până la 1.6 Terabiți pe secundă. Obiectivul grupului este o rată de date MAC Ethernet de 1.6 Tbps, urmărind o rată maximă de eroare de biți de cel mult 10-13 la nivelul MAC. Alte prevederi includ interfețe opționale pentru unități de atașare pe 16 și 8 benzi (AUI) potrivite pentru diferite aplicații de cip, utilizând SerDes 112G și 224G. Din punct de vedere fizic, specificația de 1.6 Tbps presupune transmisie prin 8 perechi de cabluri twinax de cupru de până la un metru și 8 perechi de fibră pentru distanțe cuprinse între 500 de metri și 2 km. Deși ratificarea completă a standardului este anticipată până în primăvara anului 2026, setul de bază de caracteristici este proiectat pentru finalizarea în 2024.

Supraîncărcarea lățimii de bandă și corectarea erorilor într-un subsisteme Ethernet 1.6T

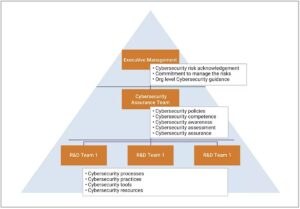

Fig. 1: Diagramă care prezintă componentele unui subsistem Ethernet 1.6T.

În iterațiile Ethernet anterioare, PCS s-a concentrat în primul rând pe codificarea datelor pentru detectarea fiabilă a pachetelor. Cu toate acestea, odată cu escaladarea la viteze Ethernet 1.6T, necesitatea corectării erorilor directe (FEC) devine evidentă, în special pentru a contracara degradarea semnalului chiar și pe legăturile scurte. În acest scop, 1.6T Ethernet continuă să utilizeze Reed-Solomon FEC. Această abordare construiește un cuvânt de cod care cuprinde 514 simboluri pe 10 biți codificate într-un bloc de 544 simboluri, rezultând o supraîncărcare a lățimii de bandă de 6%. Aceste cuvinte de cod FEC sunt distribuite pe legăturile fizice AUI, astfel încât fiecare legătură fizică (8 pentru Ethernet 1.6T) să nu poarte un întreg cuvânt de cod. Această metodă nu numai că oferă protecție suplimentară împotriva exploziilor de eroare, dar permite și paralelizarea la decodorul de la capătul îndepărtat, reducând astfel latența.

Atașamentul pentru mediu fizic (PMA), cu o cutie de viteze și SerDes, aduce semnalul Ethernet pe canalele transmise. Pentru Ethernet 1.6T, aceasta implică 8 canale care rulează fiecare la 212 Gbps, reprezentând o supraîncărcare FEC de 6%. Tehnica de modulație folosită este modularea de amplitudine a impulsurilor pe 4 niveluri (PAM-4), care codifică doi biți de date pentru fiecare simbol de transmisie, dublând astfel efectiv lățimea de bandă atunci când este juxtapusă cu abordarea tradițională Non-Return Zero (NRZ). Mecanismul de transmisie se bazează pe conversia digital-analogic, în timp ce la capătul receptor o conversie analog-digitală combinată cu DSP-uri asigură extragerea precisă a semnalului.

În plus, este important de reținut că Ethernet PCS introduce un „FEC exterior” care se întinde de la capăt la capăt pe o legătură Ethernet. Pentru a spori canalele de acoperire mai lungă, un strat suplimentar de corectare a erorilor pentru liniile fizice individuale este în curs de dezvoltare, adoptând probabil un cod de hamming FEC. Se anticipează că această corecție își va găsi aplicația principală în modulele emițător-receptoare optice unde o astfel de corecție este imperativă.

Fig. 2: Diagramă care prezintă supraîncărcarea suplimentară adăugată atunci când se utilizează un FEC concatenat pentru o rază extinsă.

În exemplul de sistem prezentat în figura 2, MAC și PCS sunt conectate printr-un modul optic și o fibră extensibilă. PCS are o rată de eroare de biți de 10-5 la legătura modulului optic, plus erori de la legătura optică în sine. Folosirea unui singur RS-FEC end-to-end nu ar fi suficientă pentru a atinge 10-13 Standard Ethernet, făcând legătura nesigură. O opțiune ar fi o implementare triplă a RS FEC separat la fiecare hop, crescând semnificativ costurile și latența. O soluție mai eficientă este integrarea unui cod Hamming FEC concatenat special pentru legătura optică, care răspunde erorilor tipice aleatorii ale conexiunilor optice. Acest strat FEC interior creează o extindere suplimentară a ratei de linie de la 212 Gbps la 226 Gbps, prin urmare este esențial ca SerDes să poată suporta această rată de linie.

Provocări de latență în sistemele Ethernet 1.6T

Fig. 3: Calea de latență pentru subsistemul Ethernet 1.6T.

Diverse componente contribuie la latența Ethernet: coada de transmisie, durata transmisiei, timpul mediu de parcurgere și mai mulți timpi de procesare și recepție. Pentru a vizualiza acest lucru, luați în considerare figura 3, care afișează un subsistem Ethernet 1.6T complet. În timp ce latența poate fi influențată de timpul de reacție al aplicației de la distanță, acest factor este extern Ethernet și, prin urmare, adesea exclus în timpul analizei latenței. Minimizarea latenței la interfața Ethernet necesită înțelegerea circumstanțelor specifice. De exemplu, latența poate să nu fie o preocupare principală pentru conexiunile trunchiului dintre comutatoare din cauza întârzierilor inerente ale legăturilor client mai lente. Distanța joacă și ea un rol; lungimi mai mari introduc mai multă latență. Desigur, asta nu înseamnă că ar trebui să trecem cu vederea latența în alte scenarii, reducerea latenței este întotdeauna un obiectiv.

Latența de transmisie este legată în mod inerent de rata Ethernet și de dimensiunea cadrului. Mai exact, pentru un sistem Ethernet 1.6T, transmiterea unui pachet de dimensiuni minime necesită 0.4 ns - în esență, un cadru Ethernet per tick de ceas de 2.5 GHz. Pe de altă parte, transmiterea unui cadru standard de dimensiune maximă durează 8ns, extinzându-se la 48ns pentru cadrele Jumbo. Mediul ales dictează în continuare latența. De exemplu, fibra optică are de obicei o latență de 5 ns pe metru, în timp ce cablurile de cupru sunt puțin mai rapide la 4 ns pe metru.

Un segment substanțial al latenței generale este înrădăcinat în controlerul receptorului. Decodorul RS FEC introduce în mod inerent latența. Pentru a iniția corectarea erorilor, sistemul trebuie să primească 4 cuvinte de cod, care, la 1.6 Tbps, se ridică la 12.8 ns. Activitățile ulterioare, inclusiv corectarea erorilor și tamponarea, amplifică această latență. În timp ce durata de stocare a cuvântului de cod FEC rămâne consecventă, latența în timpul recepționării mesajului este condiționată de implementarea specifică. Cu toate acestea, latența poate fi optimizată prin utilizarea unor strategii meticuloase de proiectare digitală.

În esență, există o latență inerentă, inevitabil, din cauza mecanismului FEC și a distanței fizice sau a lungimii cablului. Dincolo de acești factori, expertiza în proiectare joacă un rol esențial pentru a minimiza latența controlerului Ethernet. Folosirea unei soluții complete care integrează și optimizează MAC, PCS și PHY, deschide calea pentru cea mai eficientă implementare cu latență scăzută.

Rezumat

Fig. 4: Succesul siliciului de primă trecere pentru Synopsys 224G Ethernet PHY IP în proces de 3 nm, prezentând ochi PAM-4 extrem de lineari.

Ethernet de 1.6 Tbps este adaptat pentru cele mai solicitante lățimi de bandă și aplicații sensibile la latență. Odată cu apariția tehnologiei 224G SerDes, împreună cu progresele în MAC și PCS IP, sunt acum accesibile soluții cuprinzătoare care se conformează continuu standardelor Ethernet 1.6T în evoluție. În plus, datorită latenței intrinsece protocolului și metodelor de corectare a erorilor, designul IP digital și analogic trebuie să fie elaborat cu sârguință de către designeri experți pentru a evita introducerea latenței inutile în calea de date.

Obținerea performanțelor de top pentru proiectele SoC 1.6T necesită o arhitectură optimizată eficient și practici de proiectare meticuloase pentru fiecare componentă de cip. Acest lucru accentuează conservarea energiei și minimizează amprenta de siliciu, făcând ca ratele de date de 1.6 T să devină realitate. IP Synopsys 224G Ethernet PHY, dovedit de silicon a pregătit scena pentru controlerul 1.6T MAC și PCS. Folosind tehnici de proiectare, analiză, simulare și măsurare de vârf, Synopsys continuă să ofere o integritate a semnalului și o performanță de fluctuație excepțională, cu un soluție Ethernet completă, inclusiv MAC+PCS+PHY.

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- PlatoData.Network Vertical Generative Ai. Împuterniciți-vă. Accesați Aici.

- PlatoAiStream. Web3 Intelligence. Cunoștințe amplificate. Accesați Aici.

- PlatoESG. carbon, CleanTech, Energie, Mediu inconjurator, Solar, Managementul deșeurilor. Accesați Aici.

- PlatoHealth. Biotehnologie și Inteligență pentru studii clinice. Accesați Aici.

- Sursa: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :are

- :este

- :nu

- :Unde

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- acces

- accesibil

- Contabilitate

- precis

- Obține

- peste

- activităţi de

- adăugat

- Suplimentar

- În plus,

- Adoptarea

- progresele

- înaintând

- împotriva

- Urmarind

- permis

- deja

- de asemenea

- Cu toate ca

- mereu

- în mijlocul

- Sume

- amplifica

- an

- analiză

- și

- Anticipat

- aplicație

- aplicatii

- abordare

- arhitectură

- SUNT

- AS

- At

- evita

- Back-end

- fundal

- Lățime de bandă

- BE

- devine

- între

- Dincolo de

- Pic

- Bloca

- susține

- stimularea

- Aduce

- construiește

- dar

- by

- cablu

- cabluri

- CAN

- capacități

- transporta

- provocări

- canale

- cip

- Chips

- ales

- împrejurări

- client

- Ceas

- Cloud

- cloud computing

- cod

- combinate

- combinând

- Comunicare

- Completă

- completare

- component

- componente

- cuprinzător

- care cuprinde

- tehnica de calcul

- Îngrijorare

- conjuncție

- legat

- Conexiuni

- CONSERVARE

- Lua în considerare

- Considerații

- consistent

- continuă

- continuu

- a contribui

- Control

- controlor

- Convertire

- Cupru

- Nucleu

- Cheltuieli

- contracara

- înscrie-te la cursul

- fabricat

- creează

- Curent

- de date

- Datacenter

- debut

- întârzieri

- livra

- Cerere

- cerând

- cererile

- ilustrând

- Amenajări

- Designerii

- modele

- Detectare

- Dispozitive

- dicteaza

- diferit

- digital

- sârguință

- afișează

- distanţă

- distribuite

- Nu

- dublare

- două

- durată

- în timpul

- fiecare

- Mai devreme

- ecosistem

- Eficace

- în mod eficient

- eficiență

- eficient

- eficient

- Eforturile

- apariție

- subliniază

- subliniind

- angajat

- angajarea

- permite

- permițând

- , acoperă

- capăt

- un capăt la altul

- asigură

- Întreg

- eroare

- Erori

- Escaladarea

- esenţă

- esenţial

- În esență,

- Eter (ETH)

- Chiar

- Fiecare

- evident

- evoluție

- exemplu

- excepțional

- exclus

- extinderea

- expansiune

- de aşteptat

- expert

- expertiză

- extinde

- extindere

- extern

- extracţie

- Ochi

- factor

- factori

- departe

- mai repede

- DESCRIERE

- Dispunând

- Figura

- Găsi

- First

- Prima generatie

- debit

- concentrat

- a urmat

- urmă

- Pentru

- formulând

- Înainte

- FRAME

- din

- mai mult

- generaţie

- oferă

- mai mare

- grup

- Grupului

- În creştere

- mână

- Manipularea

- Înalt

- performanta ridicata

- extrem de

- Totuși

- HTML

- HTTPS

- imperativ

- implementarea

- importanță

- important

- îmbunătățit

- in

- În altele

- include

- Inclusiv

- crescând

- individ

- industrial

- influențat

- inerent

- în mod inerent

- iniția

- Inițiativă

- instanță

- integreaza

- integrare

- integritate

- interfaţă

- interfeţe

- Internet

- Interoperabilitate

- în

- intrinsec

- introduce

- Prezintă

- introducerea

- implică

- IP

- IT

- iterații

- ESTE

- în sine

- jpg

- Bandă

- Latență

- strat

- straturi

- Lungime

- nivelurile de

- efectului de pârghie

- Probabil

- Linie

- linii

- LINK

- Link-uri

- trăi

- mai lung

- Jos

- mac

- Efectuarea

- administra

- administrare

- max-width

- maxim

- Mai..

- însemna

- măsurare

- mecanism

- mediu

- Memorie

- mesaj

- metodă

- Metode

- meticulos

- minim

- minimaliza

- minimizează

- minimizând

- modul

- Module

- mai mult

- cele mai multe

- trebuie sa

- Nearing

- Nevoie

- rețele

- cu toate acestea

- Nu.

- nota

- acum

- obiectiv

- of

- de multe ori

- on

- ONE

- afară

- de operare

- optimizate

- Optimizează

- Opțiune

- or

- Altele

- peste

- global

- perechi

- parametrii

- în special

- cale

- PC-uri

- pentru

- performanță

- spectacole

- fizic

- Fizic

- conducte

- pivot

- Plato

- Informații despre date Platon

- PlatoData

- joacă

- la care se adauga

- potenţial

- putere

- practicile

- în primul rând

- primar

- proces

- prelucrare

- procesoare

- progresie

- proiectat

- protecţie

- protocol

- puls

- scop

- împingerea

- calitate

- radio

- aleator

- gamă

- rată

- tarife

- ajunge

- ajungând

- reacţie

- Realitate

- a primi

- primire

- recepție

- reducerea

- de încredere

- rămășițe

- tencuială

- Necesită

- limitat

- rezultând

- robust

- Rol

- înrădăcinat

- funcţionare

- scalabilitate

- Scară

- scenarii

- fără sudură

- Al doilea

- văzut

- segment

- sensibil

- distinct

- servi

- serviciu

- set

- câteva

- comun

- Pantaloni scurți

- să

- simbolizeazã

- Semnal

- semnificativ

- Siliciu

- simulare

- Mărimea

- So

- soluţie

- soluţii

- se întinde

- varful de lance

- specific

- specific

- specificație

- viteze

- primăvară

- Etapă

- standard

- standardizare

- standarde

- depozitare

- strategii

- de streaming

- ulterior

- substanțial

- succes

- astfel de

- potrivit

- a sustine

- simbol

- sistem

- adaptate

- ia

- tehnică

- tehnici de

- Tehnologia

- decât

- acea

- lor

- Acolo.

- astfel

- prin urmare

- Acestea

- acest

- Prin

- Prin urmare

- căpușă

- legat

- timp

- ori

- la

- top

- tradiţional

- trafic

- transfer

- transmite

- triplu

- Două

- tipic

- tipic

- inevitabil

- înţelegere

- întreprinde

- unitate

- viitoare

- pe

- folosind

- folosi

- de

- imagina

- Cale..

- we

- cand

- care

- în timp ce

- mai larg

- cu

- în

- ar

- încă

- zephyrnet

- zero