Chiplets au simplificat o zonă a designului, dar au deschis cutia Pandorei pe un alt front. Complexitatea simulării fiecăruia chiplet este mai mică, dar acum interconectarea chiplet-to-chiplet a devenit complexă. Oamenii experimentează cu diferite protocoale de interconectare, variații ale UCIe, modificând setările UCIe, vitezele interfeței, numărul de straturi fizice și așa ceva. Acum adăugați standarde vechi precum AXI, protocoale noi precum PICe6.0 și coerența cache la amestec.

În total, acest lucru creează un set complet nou de experimente. Unul pentru care emularea tradițională și modelarea RTL nu vor funcționa. Mai întâi trebuie să depui un efort pe compromisul arhitecturii, nu doar în selectarea componentelor. Aceasta va însemna că va trebui să efectuați analize de trafic, partiționarea aplicațiilor, dimensionarea sistemului și impactul diferitelor tipuri de strat fizic. De asemenea, în funcție de aplicație, benchmark-ul va fi foarte diferit.

Specificația UCIe este nouă și nu există criterii de referință clare. De asemenea, specificația UCIe oferă doar îndrumări privind latența și puterea. Ambele sunt cerințe stricte. Aceasta înseamnă că un studiu Putere-Performanță-Zona este evitabil. Deoarece aveți conversie protocol-protocol-protocol, cum ar fi PCIe 6.0 la UCIe la AXI, configurația de modelare este complexă.

O soluție este să te uiți la modelarea sistemului folosind VisualSim din mirabilis Proiecta. Aceștia au lansat recent un model IP la nivel de sistem UCIe și vor demonstra o serie de cazuri de utilizare a interconectării la Summit-ul Chiplet. Pentru a ghida designerii, aceștia au publicat un ghid cu o mulțime de cazuri de utilizare, rezultate așteptate de performanță energetică și opțiuni de optimizare. Au atât o prezentare de hârtie, cât și un stand la Summit. Sper să ne vedem acolo!

De asemenea, aici este linkul pentru o lucrare pe care oamenii o pot obține: Modelarea performanței unui sistem de calcul eterogen bazat pe arhitectura de interconectare UCIe

Rezumat:

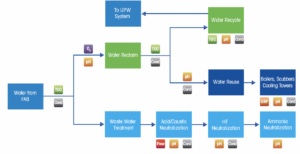

Modelele complexe de cip de astăzi la nodurile de vârf constau, în general, din mai multe matrițe (sau chipleturi). Abordarea permite matrițe de la diferiți producători sau procese, precum și IP reutilizabil. Designerii au nevoie de un model la nivel de sistem pentru a evalua diferite implementări ale unor astfel de situații complexe.

Un exemplu de sistem constă dintr-un chiplet I/O, chiplet de bază de putere redusă, chiplet de bază de înaltă performanță, chiplet audio-video și chiplet analog, interconectate folosind standardul Universal Chiplet Interconnect Express (UCIe).

Echipa noastră a luat în considerare mai multe scenarii și configurații, inclusiv pachete avansate și standard, profiluri și resurse variate de trafic și un temporizator pentru a extinde acoperirea și a evalua evenimentele la expirarea timpului. Identificarea punctelor forte și a punctelor slabe ale interconexiunii UCIe pentru aplicațiile de misiune ne-a ajutat să obținem configurația optimă pentru fiecare subsistem pentru a îndeplini cerințele de performanță, putere și funcționare.

Despre Mirabilis Design Inc.

Mirabilis Design este o companie de software din Silicon Valley, care furnizează soluții software și de instruire pentru a identifica și elimina riscurile din specificațiile produsului, prezicând cu acuratețe resursele umane și de timp necesare dezvoltării produsului și îmbunătățirea comunicării între diverse inginerie.

echipe.

VisualSim Architect combină proprietatea intelectuală, modelarea la nivel de sistem, simularea, analiza mediului și șabloanele de aplicație pentru a îmbunătăți semnificativ construcția modelului, simularea, analiza și verificarea RTL. Mediul permite proiectanților să converge rapid către un design care îndeplinește un set divers de cerințe interdependente de timp și putere. Este utilizat foarte devreme în procesul de proiectare în paralel cu (și ca ajutor pentru) specificația scrisă și înainte de implementarea (de exemplu, RTL, cod software sau schematică) a produsului.

Citeste si:

WEBINAR: Cum să obțineți o măsurare precisă a puterii cu peste 95% în timpul explorării arhitecturii

Maparea SysML la arhitectura hardware

Cursuri de design bazat pe modele pentru studenți

Distribuie această postare prin:

- Distribuție de conținut bazat pe SEO și PR. Amplifică-te astăzi.

- PlatoData.Network Vertical Generative Ai. Împuterniciți-vă. Accesați Aici.

- PlatoAiStream. Web3 Intelligence. Cunoștințe amplificate. Accesați Aici.

- PlatoESG. carbon, CleanTech, Energie, Mediu inconjurator, Solar, Managementul deșeurilor. Accesați Aici.

- PlatoHealth. Biotehnologie și Inteligență pentru studii clinice. Accesați Aici.

- Sursa: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :are

- :este

- :nu

- a

- precis

- precis

- Obține

- adăuga

- avansat

- Ajutorul

- permite

- de-a lungul

- de asemenea

- an

- analiză

- și

- O alta

- aplicație

- aplicatii

- abordare

- arhitectură

- SUNT

- ZONĂ

- AS

- At

- bazat

- BE

- deveni

- înainte

- Benchmark

- valori de referință

- între

- atât

- Cutie

- dar

- cache

- CAN

- Poate obține

- cazuri

- cip

- clar

- cod

- combină

- Comunicare

- companie

- complet

- complex

- complexitate

- componente

- tehnica de calcul

- Conduce

- Configuraţie

- luate în considerare

- constă

- construcţie

- converg

- Convertire

- Nucleu

- cursuri

- creează

- demonstrând

- În funcție

- Amenajări

- proces de design

- Designerii

- modele

- dezvolta

- diferit

- diferit

- în timpul

- fiecare

- Devreme

- efort

- elimina

- emulație

- permite

- Mediu inconjurator

- evalua

- evenimente

- exemplu

- de aşteptat

- experimentarea

- experimente

- expres

- extinde

- First

- Pentru

- din

- faţă

- funcțional

- în general

- obține

- îndrumare

- ghida

- Piese metalice

- Avea

- a ajutat

- aici

- performanta ridicata

- speranţă

- Cum

- Cum Pentru a

- HTTPS

- uman

- i

- identifica

- identificarea

- Impactul

- implementarea

- implementările

- îmbunătăţi

- in

- Inclusiv

- intelectual

- de proprietate intelectuală

- interconectate

- interfaţă

- IP

- IT

- jpg

- doar

- Latență

- a lansat

- strat

- straturi

- Moştenire

- Nivel

- ca

- LINK

- Uite

- loturi

- Jos

- LOWER

- Producătorii

- max-width

- însemna

- mijloace

- măsurare

- Întâlni

- se intalneste

- Misiune

- amesteca

- model

- modelare

- modelare

- multiplu

- Nevoie

- Nou

- Nu.

- noduri

- acum

- număr

- obține

- of

- on

- ONE

- afară

- deschide

- deschis

- optimă

- optimizare

- Opţiuni

- or

- ofertele

- Hârtie

- Paralel

- performanță

- fizic

- Plato

- Informații despre date Platon

- PlatoData

- Post

- putere

- estimarea

- prezentare

- proces

- procese

- Produs

- Profiluri

- proprietate

- protocoale

- furnizează

- furnizarea

- publicat

- repede

- ajunge

- Citeste

- recent

- necesar

- Cerinţe

- Resurse

- REZULTATE

- reutilizabile

- Risc

- scenarii

- vedea

- selectarea

- set

- setări

- configurarea

- câteva

- semnificativ

- Siliciu

- Silicon Valley

- simplificată

- simulare

- situații

- So

- Software

- soluţie

- soluţii

- specificație

- viteze

- petrece

- standard

- standarde

- puncte forte

- stringent

- Studiu

- astfel de

- Summit-ul

- sistem

- echipă

- şabloane

- acea

- Acolo.

- ei

- acest

- timp

- la

- tradiţional

- trafic

- Pregătire

- Tipuri

- Universal

- us

- utilizare

- utilizat

- folosind

- Vale

- variații

- Verificare

- foarte

- de

- puncte slabe

- BINE

- care

- voi

- cu

- Apartamente

- scris

- tu

- zephyrnet