A integração de múltiplas matrizes heterogêneas em um pacote é fundamental para estender a Lei de Moore e melhorar o desempenho, a eficiência energética e a funcionalidade, mas também está levantando questões significativas sobre como gerenciar a carga térmica.

Embalagem avançada fornece uma maneira de incluir mais recursos e funções em um dispositivo, cada vez mais empilhando vários componentes verticalmente, em vez de apenas encolher os circuitos digitais para amontoar mais funcionalidades em um SoC do tamanho de um retículo. Isso levanta questões sobre como otimizar o desempenho e a potência. Em uma única matriz, os caminhos do sinal podem ser tão curtos quanto necessário e o substrato é eficaz na dissipação do calor. Mas com múltiplas matrizes em um pacote, os substratos e os dielétricos precisam ser mais finos para reduzir a distância que os sinais precisam percorrer, e isso limita a dissipação térmica.

Isso pode levar a pontos críticos, que podem ser difíceis de prever, especialmente sob diversas cargas de trabalho e casos de uso. E isso pode ser piorado ao integrar vários chips ou chips com propriedades térmicas variadas em um único pacote.

“Sempre que você coloca várias matrizes em um substrato ou interpositor, é um desafio”, diz Vik Chaudhry, diretor sênior de marketing de produto e desenvolvimento de negócios da Tecnologia Amkor. “Estamos vendo fornecedores colocando não apenas 3 ou 4, mas 8, 10 ou 12 dados. Como você distribui esse calor por toda parte?”

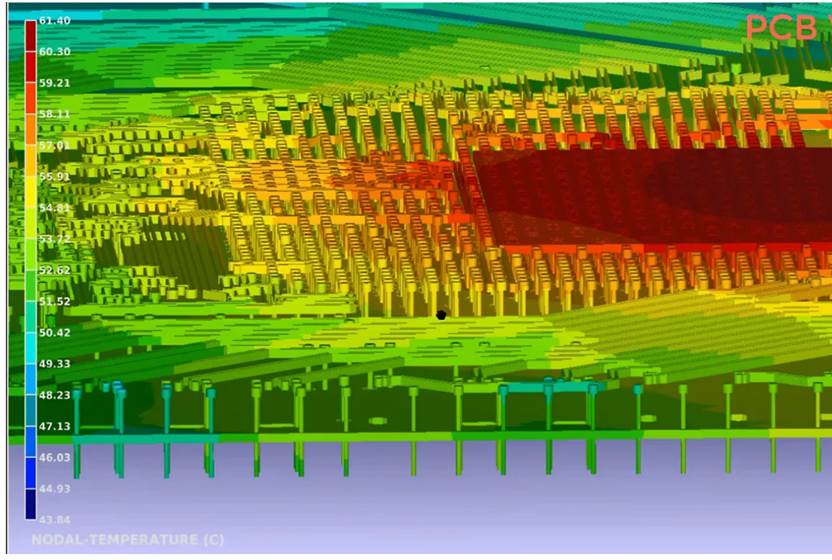

Figura 1: Simulação de dissipação de calor em pares térmicos. Fonte: Ansys

Integração heterogênea depende da capacidade de remover efetivamente o calor, garantindo que as matrizes densamente compactadas dentro de um módulo mantenham temperaturas aceitáveis para uma operação confiável. O Roteiro de Integração Heterogênea do IEEE identifica diversas áreas de necessidade de desenvolvimento, incluindo técnicas avançadas de modelagem para prever e gerenciar o fluxo de calor, novos materiais com alta condutividade térmica e baixa condutividade elétrica e novas soluções de resfriamento que podem ser perfeitamente integradas em pacotes complexos.

Incompatibilidade térmica

As escolhas de materiais são críticas para o gerenciamento térmico na integração heterogênea. À medida que componentes com diferentes coeficientes de expansão térmica (CTE) aquecem e esfriam, esses materiais se expandem e contraem em taxas diferentes. Isso pode causar tensões mecânicas que comprometem a integridade dos chips, enfraquecer as ligações que os conectam aos intermediários ou outros substratos e afetar a funcionalidade geral de um dispositivo.

O emprego de materiais com CTEs semelhantes ajuda a reduzir essas tensões, mitigando alguns dos riscos de falha prematura, bem como outros efeitos induzidos termicamente, como envelhecimento acelerado, mobilidade reduzida de elétrons ou desvio em sinais analógicos ou ópticos.

“CTE é provavelmente o desafio número um para embalagens avançadas, e não acho que alguém tenha realmente entendido isso completamente”, diz David Fromm, COO e vice-presidente de engenharia da Indústrias Promex. “Estamos lidando com CTE em uma escala tridimensional de uma forma que nunca vimos antes, e esses problemas com empenamento ou quebra de peças são realmente desafiadores. Algumas empresas podem descobrir isso para um determinado processo e, então, os materiais mudam, os tamanhos dos dispositivos mudam e a equação muda. E então você tem que descobrir de novo.”

Simplificando, a integração heterogênea requer uma compreensão fundamental das propriedades de expansão térmica de cada material que poderia, em última análise, moldar a confiabilidade e o rendimento do dispositivo embalado. E isso é apenas parte do problema. O empacotamento avançado requer uma compreensão do que mais existe na vizinhança de um chip ou chiplet, como esses outros elementos estão sendo usados, e tudo isso precisa ser modelado e simulado em conjunto usando o que se espera ser uma carga de trabalho realista. Este problema torna-se muito mais difícil quando as necessidades de computação mudam, como em centros de dados onde a IA generativa aumentou significativamente a quantidade de dados que precisam de ser processados, resultando numa maior utilização de processadores e memórias.

“Sempre houve algum nível de análise térmica, mas ela foi feita no final apenas para verificar se nada saía do controle”, diz Marc Swinnen, diretor de marketing de produto da Ansys. “Você poderia atingir uma determinada temperatura de junção e, se fosse compatível, era simples assim. Mas agora, com sistemas multi-matrizes, você terá que fazer isso na fase de planejamento do RTL. Você precisará ter uma ideia de qual é a potência de saída de cada um desses chips, para que dois chips que esquentam no mesmo modo de operação não sejam colocados um ao lado do outro ou um em cima do outro. . Isso condenará seu projeto.

De volta à prancheta

À medida que a indústria enfrenta vários desafios no roteiro de integração heterogêneo, o gerenciamento térmico não é mais uma reflexão tardia. Ele mudou para a esquerda no fluxo do projeto até a fabricação e para o campo onde os monitores no circuito podem avaliar e ajustar tudo, desde o particionamento até a priorização de diferentes chips e chips.

“O diabo está nos detalhes”, diz Fromm. “Essas decisões aparentemente menores de design e integração podem ter um impacto tremendo sobre se você pode construir o que deseja, muito menos construí-lo com rendimento e confiabilidade do produto downstream. Escolher os materiais certos, pensar nos empilhamentos e pensar no fluxo do processo são fundamentais.”

Isto representa uma mudança fundamental num número crescente de designs, desde centros de dados até produtos eletrónicos de consumo e veículos cada vez mais autónomos. Como elementos heterogêneos são empacotados juntos em fan-outs com pilares, 2.5D, e especialmente em IC 3D projetos, os caminhos térmicos precisam ser mapeados com detalhes cada vez maiores. Feito de maneira errada, isso pode causar danos a um pacote inteiro cheio de vários chips/chiplets, onde até mesmo encontrar a origem do problema pode custar caro.

“Há uma necessidade de projetar restrições termomecânicas, bem como o substrato e a tecnologia de montagem”, diz George Orji, cientista pesquisador do CHIPS National Advanced Packaging Manufacturing Program (NAPMP). “As embalagens avançadas não permitem retrabalho, portanto, metodologias monolíticas de design de chips para embalagens avançadas são algo que precisamos fazer.”

A complexidade inerente aos sistemas heterogeneamente integrados exige uma abordagem multidisciplinar ao design. Isso é complicado e as tentativas de fazer essa abordagem funcionar não são novas e falharam diante do dimensionamento planar. David Fried, vice-presidente corporativo da Lam Research, disse durante um painel de discussão recente que a IBM tentou a integração heterogênea 3D há 25 anos, quando ele estava lá. “Pensamos que poderíamos juntar muitos dos componentes do processo”, disse ele. “Mas alguns dos maiores desafios estavam no lado do design e da EDA, dividindo qual tecnologia usar, como segmentar os diferentes componentes do sistema em chips diferentes e depois voltar e integrá-los. O design e a otimização do design precisam estar presentes para que isso funcione.”

O que mudou desde então é que a indústria de chips ficou sem opções. Está se tornando muito caro desenvolver chips nos nós mais avançados e muito limitado pelo tamanho do retículo. Mas este ainda é um trabalho difícil.

Para aliviar a carga sobre os projetistas, técnicas sinérgicas que envolvem ciências avançadas de materiais e ferramentas de projeto auxiliadas por computador são cada vez mais cruciais, especialmente à medida que as configurações dos chips se tornam mais complexas e a funcionalidade integrada aumenta. “É aqui que ainda temos trabalho a fazer”, acrescenta Swinnen, da Ansys. “Como podemos resolver isso de uma forma que não exija que todo projetista seja um especialista em térmica, um especialista em interferência eletromagnética e um especialista em mecânica? Não é realista esperar isso da nossa comunidade de design.”

Com estas restrições surge a necessidade de inovação em vários aspectos-chave do processo de design. Reconhecendo a natureza multifacetada da geração de calor em chips densamente integrados, é imperativo abordar não apenas eventos térmicos de estado estacionário, mas também transitórios, que são amplamente baseados em casos de uso ou cargas de trabalho. O roteiro para integração heterogênea inclui estratégias como materiais de interface térmica 3D e dissipadores de calor compatíveis com CTE para garantir uma distribuição uniforme de calor.

“Com múltiplas matrizes, você tem múltiplas fontes de efeitos térmicos, múltiplos gradientes mecânicos e gradientes de temperatura”, diz Manuel Mota, gerente sênior de marketing de produto da Synopsys. “Tudo isso deve ser abordado na fase de design.”

Integrar considerações térmicas no processo de design é um requisito para a realização prática de qualquer dispositivo semicondutor complexo. Não se trata apenas de identificar os materiais ou componentes certos. Também está prevendo como todos funcionarão coletivamente em campo.

À medida que os engenheiros reduzem o formato dos dispositivos eletrônicos e aumentam seu desempenho, o envelope térmico fica significativamente mais rígido. O gerenciamento abrangente de perfis térmicos em diferentes estados operacionais, aproveitando os mais recentes materiais de dissipação de calor e de interface térmica, torna-se essencial para manter a integridade e o desempenho do dispositivo durante o ciclo de vida pretendido.

“A térmica é a limitação número um para a densidade de integração”, diz Swinnen. “É fácil empilhar as fichas. Você pode fabricá-lo e projetá-lo, mas nunca funcionará porque ficará muito quente. Portanto, a térmica tornou-se uma parte central da preocupação de todo projetista de chips 3D-IC.”

Resolver o desafio térmico na integração heterogênea requer a união de diferentes materiais, como semicondutores com CTEs mais baixos, como o silício, com metais como cobre ou alumínio, para dissipar efetivamente o calor. Infelizmente, essa mistura de materiais geralmente leva a empenamentos, rachaduras, levantamento de solda e falha dos dispositivos antes do esperado. São necessários novos materiais que tenham propriedades compatíveis para superar esses problemas.

“Esses materiais de substrato provavelmente se desenvolverão mais lentamente do que os materiais de interface, adesivos, epóxis e assim por diante”, diz Fromm. “Tudo se resume às condições do processo e como você as gerencia. Onde podemos ser melhores no lado do processamento é trabalhar com os fabricantes de adesivos para entender as mudanças na temperatura e, em seguida, no nível do projeto, para entender como todas essas pilhas podem evoluir, considerando essas mudanças na temperatura.”

Inovações de materiais

As preocupações térmicas vão muito além da operação do chip. O calor também é um problema do lado da fabricação. Os chips dentro de um pacote avançado precisam sobreviver à montagem e à fabricação, onde alguns dos mesmos problemas de CTE podem se tornar problemáticos.

Considere a matriz coletiva para wafer (CoD2W), por exemplo, que usa ligação por termocompressão para anexar uma matriz a um wafer. “No processo CoD2W, há situações em que matrizes diferentes vêm de fontes diferentes e podem ter alturas ou espessuras diferentes”, diz Rama Puligadda, diretor executivo de P&D de tecnologias avançadas da Ciência cervejeira. “Quando você preenche um transportador com essas matrizes, é muito difícil saber se todas as matrizes entrarão em contato com o alvo durante a ligação. As propriedades mecânicas do adesivo de fixação à matriz são projetadas para permitir que a matriz mais alta fique levemente incorporada durante a colagem, o que permite um bom contato de todas as matrizes com o wafer alvo.”

Isso levanta questões diferentes. “Os desafios para nossos materiais incluem limitações de temperatura de diferentes matrizes”, disse Puligadda. “Temos que garantir que as temperaturas usadas para unir os materiais não excedam as limitações térmicas de nenhum dos chips que estão sendo integrados na embalagem. Além disso, pode haver alguns processos subsequentes, como formação de camada de redistribuição ou moldagem. Nossos materiais precisam sobreviver a esses processos. Eles têm que sobreviver aos produtos químicos com os quais entram em contato durante todo o esquema do processo de embalagem. As tensões mecânicas na embalagem acrescentam desafios adicionais para a colagem de materiais.”

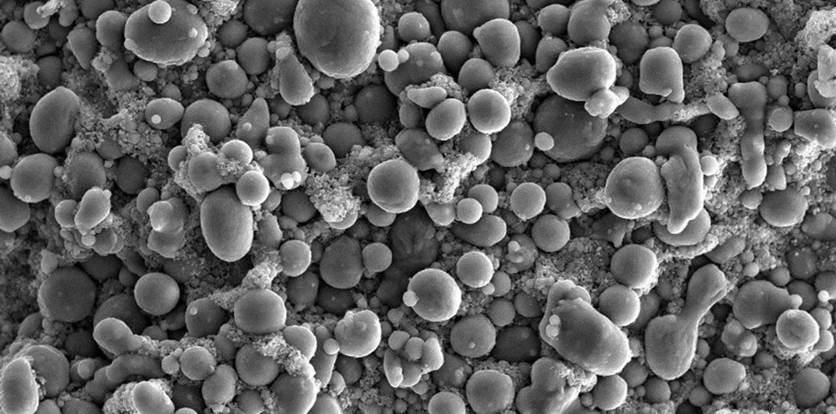

Está em desenvolvimento uma variedade de materiais que oferecem condutividade térmica superior, bem como isolamento elétrico. Esses materiais de interface térmica (TIMs) recém-projetados fornecem caminhos eficientes de condução de calor entre um chip e seu cooler sem interferir no desempenho do chip. Os TIMs não apenas apresentam melhor condutividade térmica, mas também atendem às pequenas variações induzidas pela geração desigual de calor na superfície do chip.

“O gerenciamento térmico exigirá novos materiais térmicos, bem como novas topologias de circuito que empreguem substratos avançados e integração heterogênea”, diz Orji. “Como os chips são embalados tão próximos uns dos outros, a capacidade de espalhar o excesso de calor é muito limitada.”

Fig 2: Vista detalhada de um material de interface térmica de polímero carregado de partículas. Fonte: Amkor

Idealmente, estes novos materiais apresentarão fortes ligações covalentes e massas equilibradas de aniões-cátions, semelhantes à estrutura atómica descomplicada encontrada no diamante. Os materiais reconhecidos nesta categoria incluem o diamante, juntamente com compostos como óxido de berílio, nitreto de alumínio, nitreto de boro e, até certo ponto, nitreto de silício. Apesar de suas capacidades de condução térmica, esses materiais apresentam desafios de fabricação devido às próprias ligações que proporcionam sua resistência, necessitando de processos de sinterização em alta temperatura, por exemplo, para atingir a densidade desejada. Uma exceção é o diamante, que não pode ser sinterizado.

Uma abordagem para aproveitar os benefícios desses materiais, apesar dos desafios de processamento, inclui a utilização de compósitos. Por exemplo, a incorporação de nitreto de alumínio em um compósito epóxi captura parcialmente as vantagens do manuseio térmico, embora não corresponda aos níveis de condutividade de um equivalente cerâmico sólido. Essa combinação de propriedades de materiais é crucial em embalagens eletrônicas, onde é desejável ter um excelente condutor elétrico que retire calor suficiente dos núcleos do chip para evitar comprometimentos no desempenho do sinal.

O diamante, celebrado por sua extrema dureza, destaca-se como exemplar condutor térmico e isolante. Materiais poliméricos como o Teflon (politetrafluoroetileno ou PTFE), embora menos condutores que a cerâmica ou o diamante, ainda superam muitos plásticos na sua capacidade de conduzir calor e oferecer isolamento elétrico confiável. O PTFE é eficaz o suficiente para ser empregado como material de revestimento em aplicações de uso intensivo de calor, como utensílios de cozinha.

Vidro, porcelana e outras cerâmicas densas compartilham essas propriedades de isolamento e condução de calor. Eles representam soluções práticas, principalmente nos casos em que também é necessário um excelente isolante elétrico para gerenciar o calor. O nitreto de alumínio (AlN) é utilizado como isolante em dispositivos semicondutores, preenchendo a lacuna entre as matrizes e os componentes de transferência de calor. Apesar de não ser tão condutor termicamente quanto o óxido de berílio, o AlN oferece uma alternativa mais segura e econômica. Além disso, o AlN supera mais isolantes padrão como mica, poliimida e alumina no que diz respeito ao gerenciamento térmico.

A safira sintética também merece atenção devido à sua acessibilidade e maleabilidade em diversas formas, tornando-a outro player valioso no espaço de embalagens de semicondutores. Cada um desses materiais apresenta vantagens únicas no projeto de embalagens onde o controle do calor sem prejudicar o desempenho eletrônico é fundamental.

Embora materiais avançados como diamante e nitreto de alumínio estejam na vanguarda do enfrentamento dos desafios térmicos em dispositivos semicondutores, nem todas as soluções exigem componentes exóticos ou rígidos. Graxas térmicas e adesivos servem como tecido conjuntivo em embalagens eletrônicas, preenchendo pequenas lacunas ou irregularidades superficiais e facilitando a transferência de calor entre componentes com topografias variadas. A sua capacidade de adaptação às superfícies proporciona um complemento crucial às soluções de gestão térmica mais sólidas, formando uma abordagem abrangente à dissipação de calor. Com foco na melhoria destes materiais, os investigadores pretendem melhorar as suas propriedades de condutividade térmica, tornando-os parceiros mais eficazes no paradigma da gestão de calor.

“As graxas térmicas e os adesivos térmicos são termicamente condutivos”, acrescenta Fromm, “mas comparados a materiais como uma cerâmica típica que são termicamente condutivos, eles são péssimos condutores por um fator de dez. Esses materiais não são tão bons e há razões físicas e químicas para isso. Há muitas vantagens a serem alcançadas e há muito trabalho acontecendo nesse espaço.”

Olhando para o futuro

À medida que novos materiais abrem caminho para o alívio térmico, novas técnicas inovadoras de resfriamento também estão em desenvolvimento. Microcanais de silício, que são caminhos em microescala gravados em substratos, podem direcionar refrigerantes diretamente para o coração dos pontos críticos. Este método de resfriamento direto é superior aos dissipadores de calor tradicionais, mas oferece desafios em design, montagem e confiabilidade.

Da mesma forma, o desenvolvimento de sistemas de refrigeração líquida em circuito fechado poderia permitir que os componentes permanecessem frios sem as restrições impostas pelos métodos de fluxo de ar. Esses sistemas oferecem a promessa de uma temperatura operacional mais baixa sem a ameaça de estrangulamento térmico, mas há muita pesquisa a ser feita tanto no projeto quanto no manuseio de processos para sistemas de refrigeração líquida.

Outra opção é simplesmente inverter a estrutura do dado empilhado, de modo que, em vez de colocar a memória em cima da lógica, a lógica seja colocada em cima da memória com um dissipador de calor em cima. Winbond, por exemplo, sugeriu isso com sua tecnologia de elementos de ultra-largura de banda personalizados (CUBE), uma abordagem de alto desempenho que empilha a matriz superior do SoC diretamente na memória, que é então anexada ao substrato usando vias de silício. A abordagem, segundo CS Lin, executivo de marketing da winbond, usa menos energia, o que por sua vez reduz o calor. Além disso, permite que o calor seja removido diretamente, em vez de canalizá-lo através de algum labirinto de componentes heterogêneos.

Outra opção é usar o gerenciamento térmico em tempo real, alimentado por IA. Os algoritmos agora podem monitorar temperaturas em vários locais no chip, direcionando os recursos de resfriamento de forma dinâmica, garantindo desempenho ideal sem cruzar a linha vermelha térmica. A ProteanTecs, por exemplo, acaba de lançar uma solução voltada para data centers que, segundo ela, pode reduzir a energia dos servidores, reduzindo a quantidade de faixas de proteção necessárias para proteger os chips contra superaquecimento. Essa abordagem depende do monitoramento das alterações dentro de um chip e do fornecimento de ajustes conforme necessário.

A Synopsys e a Siemens EDA também possuem soluções para monitorar diferentes atividades e mudanças de temperatura usando sensores internos. Ser capaz de obter leituras de dentro de uma embalagem usando telemetria é um componente cada vez mais importante no gerenciamento de calor.

“Você tem a construção mecânica de chips em chips e interposers com milhares ou milhões de micro-saliências, e todos eles se expandem e contraem à medida que o chip aquece”, acrescenta Swinnen. “Dependendo do seu mapa térmico, a integridade da sua energia terá que se adaptar ao perfil de temperatura local em tempo real. Você pode calcular quanta energia um chip está emitindo, mas a temperatura que isso o leva depende. Está em um prato frio ou ao sol no Saara? O mesmo chip e a mesma atividade podem levar a temperaturas muito diferentes dependendo do ambiente.”

Além disso, a investigação em materiais de mudança de fase, que absorvem calor alterando o seu estado, promete uma regulação de temperatura passiva mas potente. Mais ainda, a exploração de sistemas de refrigeração biológicos, tentando imitar a resposta do corpo humano ao calor, prenuncia um futuro onde os nossos dispositivos poderão dissipar o calor tão intuitivamente como transpiramos.

Conclusão

À medida que a indústria de semicondutores continua a ultrapassar os limites do desempenho e da integração, a gestão térmica dentro de embalagens avançadas continua a ser um desafio. De um lado do espectro, surgem crescentes complexidades térmicas à medida que as empresas avançam para módulos multichip mais densamente compactados. Pelo contrário, os avanços nas ciências dos materiais e nas tecnologias inovadoras de arrefecimento esforçam-se por aliviar a tensão térmica resultante. Ambos são necessários para enfrentar desafios térmicos complexos, mas ainda há muito trabalho pela frente para resolver isto de forma consistente e previsível.

- Ed Sperling contribuiu para este relatório.

Leitura relacionada

Gerenciando estresse induzido por calor em cavacos

A integração heterogênea e o aumento da densidade em nós avançados estão criando alguns desafios complexos e difíceis para a fabricação e embalagem de IC.

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiengineering.com/navigating-heat-in-advanced-packaging/

- :tem

- :é

- :não

- :onde

- $UP

- 1

- 10

- 12

- 25

- 3d

- 8

- a

- habilidade

- Capaz

- Sobre

- acelerado

- aceitável

- Segundo

- Alcançar

- alcançado

- em

- atividade

- adaptar

- adicionar

- Adição

- Adicional

- Adicionalmente

- endereço

- endereçado

- Adiciona

- Adesivos

- ajustar

- ajustes

- avançado

- Materiais avançados

- avanços

- vantagens

- afetar

- novamente

- Envelhecendo

- atrás

- à frente

- AI

- visar

- Destinado

- AR

- aparentado

- algoritmos

- Todos os Produtos

- aliviar

- permitir

- permite

- ALN

- juntamente

- tb

- alternativa

- Apesar

- sempre

- quantidade

- an

- análise

- e

- Outro

- qualquer

- aplicações

- abordagem

- SOMOS

- áreas

- por aí

- AS

- aspectos

- Montagem

- avaliar

- At

- atômico

- anexar

- Tentativas

- por WhatsApp.

- Autônomo

- veículos autônomos

- longe

- em caminho duplo

- Equilibrado

- baseado

- BE

- Porque

- tornam-se

- torna-se

- tornando-se

- sido

- antes

- ser

- Benefícios

- Melhor

- entre

- Pós

- O maior

- Blend

- Obrigações

- ambos

- limites

- Quebra

- ponte

- Traz

- construir

- carga

- negócio

- desenvolvimento de negócios

- mas a

- by

- calcular

- CAN

- capacidades

- capturas

- casos

- Categoria

- fornecer

- Causar

- celebrado

- Centralização de

- Centros

- central

- certo

- desafiar

- desafios

- desafiante

- alterar

- mudado

- Alterações

- mudança

- verificar

- químico

- produtos químicos

- lasca

- Chips

- escolhas

- escolha

- Fechar

- frio

- Collective

- coletivamente

- como

- vem

- comunidade

- Empresas

- comparado

- compatível

- Complemento

- integrações

- complexidades

- complexidade

- compatível

- complicado

- componente

- componentes

- compreensivo

- compromisso

- Computar

- Interesse

- Preocupações

- condições

- Conduzir

- condutividade

- condutor

- Contato

- Considerações

- considerando

- consistente

- restrições

- formação

- consumidor

- Eletrônicos de consumo

- Contacto

- continua

- contract

- contribuiu

- controle

- Coo

- Legal

- Cobre

- Responsabilidade

- relação custo-benefício

- dispendioso

- poderia

- Contrapartida

- COVALENTE

- Criar

- crítico

- cruzamento

- crucial

- personalizado

- dano

- dados,

- Data Center

- centros de dados

- David

- lidar

- decisões

- demandas

- denso

- densidade

- Dependendo

- depende

- Design

- processo de design

- projetado

- Designer

- desenhadores

- projetos

- desejado

- Apesar de

- detalhe

- detalhado

- detalhes

- desenvolver

- Desenvolvimento

- desenvolvimento

- dispositivo

- Dispositivos/Instrumentos

- diabo

- Diamante

- morrem

- diferente

- difícil

- digital

- diretamente

- dirigindo

- diretamente

- Diretor

- discussão

- distância

- distribuir

- distribuição

- do

- parece

- Não faz

- feito

- não

- condenação

- down

- desenho

- desenha

- distância

- dois

- durante

- dinamicamente

- cada

- Mais cedo

- fácil

- ed

- Eficaz

- efetivamente

- efeitos

- eficiência

- eficiente

- Eletrônico

- Eletrônicos

- elementos

- outro

- incorporado

- emergem

- empregada

- permite

- final

- engenharia

- Engenharia

- Engenheiros

- aumentar

- aprimorando

- suficiente

- garantir

- assegurando

- Todo

- envelope

- especialmente

- essencial

- Mesmo

- eventos

- Cada

- tudo

- evolui

- exemplo

- excedem

- excelente

- exceção

- excesso

- executivo

- Diretora Executiva

- apresentar

- Exótico

- Expandir

- expansão

- esperar

- esperado

- caro

- especialista

- exploração

- estender

- estendendo

- extensão

- extremo

- Rosto

- facilitando

- fator

- fracassado

- falta

- Falha

- longe

- Funcionalidades

- campo

- Figo

- Figura

- figurado

- preenchida

- o preenchimento

- descoberta

- fluxo

- Foco

- Escolha

- Frente

- formulário

- treinamento

- formas

- adiante

- encontrado

- da

- totalmente

- função

- funcionalidade

- funções

- fundamental

- futuro

- lacuna

- lacunas

- geração

- generativo

- IA generativa

- George

- ter

- dado

- Go

- vai

- Bom estado, com sinais de uso

- tem

- gradientes

- mão

- Manipulação

- Acontecimento

- Queijos duros

- Aproveitamento

- Ter

- he

- Coração

- alturas

- ajuda

- Alta

- alta performance

- superior

- dobradiças

- HOT

- Como funciona o dobrador de carta de canal

- Como Negociar

- HTTPS

- humano

- i

- IBM

- idéia

- identifica

- identificar

- if

- Impacto

- imperativo

- importante

- Imposta

- melhorado

- melhorar

- in

- incluir

- inclui

- Incluindo

- incorporando

- aumentou

- aumentando

- cada vez mais

- indústria

- inerente

- Inovação

- inovadores

- dentro

- instância

- em vez disso

- integrado

- Integração

- integração

- integridade

- Pretendido

- Interface

- interferência

- interferente

- interno

- para dentro

- intricado

- envolvendo

- emitem

- questões

- IT

- ESTÁ

- se

- jpg

- apenas por

- Chave

- Saber

- labirinto

- largamente

- mais recente

- Escritórios de

- camada

- conduzir

- Leads

- esquerda

- EMPRESTAR

- menos

- Nível

- níveis

- aproveitando

- wifecycwe

- facelift

- como

- limitação

- limitações

- Limitado

- limites

- lin

- Line

- Líquido

- carregar

- local

- locais

- lógica

- mais

- lote

- Baixo

- diminuir

- moldadas

- a manter

- fazer

- Fazendo

- gerencia

- de grupos

- Gerente

- gestão

- Fabricantes

- fabrica

- muitos

- mapa,

- Marketing

- massas

- Match

- material

- materiais

- max-width

- Posso..

- mecânico

- Memórias

- Memória

- Metais

- método

- metodologias

- métodos

- Mica

- poder

- milhões

- menor

- minuto

- mitigando

- misturar

- mobilidade

- Moda

- modelagem

- módulo

- Módulos

- Monitore

- monitoração

- monitores

- Monolítico

- mais

- a maioria

- muito

- multidisciplinar

- múltiplo

- devo

- Nacional

- Natureza

- navegação

- necessidade

- você merece...

- necessário

- Cria

- nunca

- Novo

- recentemente

- Próximo

- não

- nós

- nada

- romance

- agora

- número

- of

- oferecer

- Oferece

- frequentemente

- on

- ONE

- só

- operação

- operacional

- oposto

- otimização

- Otimize

- ótimo

- Opção

- Opções

- or

- Outros

- A Nossa

- Fora

- saída

- Acima de

- global

- Superar

- Pack

- pacote

- empacotado

- pacotes

- acondicionamento

- embalado

- painel

- painel de discussão

- paradigma

- Supremo

- parte

- particularmente

- Parceiros

- peças

- passiva

- caminhos

- vias

- pavimentar

- atuação

- fase

- físico

- peça

- pilares

- essencial

- Lugar

- colocado

- plásticos

- platão

- Inteligência de Dados Platão

- PlatãoData

- jogador

- polímero

- potente

- poder

- alimentado

- Prática

- predizer

- Previsível

- Prematuro

- presentes

- presidente

- evitar

- priorização

- provavelmente

- Problema

- processo

- processado

- processos

- em processamento

- processadores

- Produto

- Perfil

- Perfis

- Agenda

- promessa

- promessas

- Propriedades

- proteger

- fornecer

- fornece

- fornecendo

- Empurrar

- colocar

- Colocar

- R & D

- raises

- elevando

- rampa

- alcance

- Preços

- em vez

- reais

- em tempo real

- realista

- realização

- clientes

- razões

- recentemente

- reconhecido

- reconhecendo

- Vermelho

- reduzir

- Reduzido

- reduz

- redução

- em relação a

- Regulamento

- confiabilidade

- confiável

- alívio

- permanece

- remover

- Removido

- Denunciar

- representa

- requerer

- requeridos

- requerimento

- exige

- pesquisa

- pesquisadores

- resolver

- Recursos

- resposta

- resultante

- resultando

- reverso

- certo

- rígido

- Sobe

- Risco

- roadmap

- Enrolado

- Rota

- Execute

- s

- mais segura

- Dito

- mesmo

- diz

- Escala

- dimensionamento

- esquema

- CIÊNCIAS

- Cientista

- sem problemas

- visto

- visto

- segmento

- Semicondutor

- Semicondutores

- senior

- sensor

- servir

- Servidores

- vários

- Shape

- Partilhar

- mudança

- deslocado

- Baixo

- lado

- Siemens

- Signal

- sinais

- periodo

- de forma considerável

- Silício

- semelhante

- simples

- simplesmente

- desde

- solteiro

- Sentado

- situações

- Tamanho

- tamanhos

- Lentamente

- pequeno

- So

- sólido

- solução

- Soluções

- RESOLVER

- alguns

- algo

- fonte

- Fontes

- Espaço

- Espectro

- propagação

- pilha

- empilhado

- empilhamento

- Pilhas

- Etapa

- padrão

- fica

- Estado

- Unidos

- ficar

- Ainda

- estratégias

- força

- estresse

- lutar

- mais forte,

- estrutura

- subseqüente

- tal

- Espreguiçadeiras

- topo

- superfície

- ultrapassar

- supera

- sobreviver

- sinérgico

- .

- sistemas

- abordando

- Target

- técnicas

- Tecnologias

- Tecnologia

- dez

- terrível

- do que

- que

- A

- A fonte

- deles

- Eles

- então

- Lá.

- térmico

- Este

- deles

- think

- Pensando

- isto

- aqueles

- Apesar?

- pensamento

- milhares

- ameaça

- tridimensional

- Através da

- todo

- tempo

- tecido

- para

- juntos

- também

- ferramentas

- topo

- para

- tradicional

- transferência

- viagens

- tremendo

- experimentado

- tentando

- VIRAR

- dois

- típico

- Em última análise

- para

- compreender

- compreensão

- infelizmente

- único

- UPS

- upside

- usar

- casos de uso

- usava

- usos

- utilização

- utilizado

- Utilizando

- Valioso

- vário

- variando

- Veículos

- fornecedores

- verticalmente

- muito

- vício

- Vice-Presidente

- Ver

- queremos

- Aquece

- foi

- Caminho..

- maneiras

- we

- BEM

- foram

- O Quê

- O que é a

- quando

- se

- qual

- enquanto

- porque

- precisarão

- de

- dentro

- sem

- Atividades:

- trabalhar

- pior

- Errado

- anos

- ainda

- Produção

- Você

- investimentos

- zefirnet