Um artigo técnico intitulado “Memristores de junção de túnel ferroelétrico para aceleradores de computação em memória” foi publicado por pesquisadores da Universidade de Lund.

Abstrato:

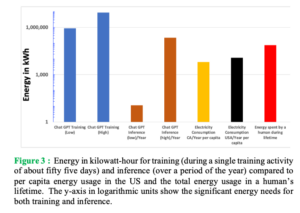

“A computação neuromórfica tem despertado grande interesse à medida que os avanços nas aplicações de inteligência artificial (IA) expuseram limitações devido ao acesso intenso à memória, com a arquitetura de computação von Neumann. A computação paralela na memória fornecida pela computação neuromórfica tem o potencial de melhorar significativamente a latência e o consumo de energia. A chave para o hardware de computação neuromórfica analógica são os memristores, que fornecem níveis de condutância multiestado não voláteis, alta velocidade de comutação e eficiência energética. Os memristores de junção de túnel ferroelétrico (FTJ) são os principais candidatos para esse propósito, mas o impacto das características específicas em seu desempenho na integração em grandes matrizes de barra transversal, o elemento central de computação para inferência e treinamento em redes neurais profundas, requer uma investigação minuciosa. Neste trabalho, um W/Hf x Zr1-x O2/TiN FTJ com 60 estados de condutância programáveis, faixa dinâmica (DR) de até 10, densidade de corrente >3 A m-2 at V ler = 0.3 V e corrente-tensão altamente não linear (4) características (> 1100) são demonstradas experimentalmente. Usando um macromodelo de circuito, o desempenho em nível de sistema de uma matriz de barra transversal verdadeira é avaliado e uma precisão de classificação de 92% do conjunto de dados do instituto nacional modificado de ciência e tecnologia (MNIST) é alcançada. Finalmente, a baixa condutância em combinação com a alta não linearidade 4 características permitem a realização de grandes matrizes de barra cruzada sem seletor para aceleradores de hardware neuromórficos.

Encontre o artigo técnico aqui. Publicado em dezembro de 2023.

Athle, R. e Borg, M. (2023), Memristores de junção de túnel ferroelétrico para aceleradores de computação em memória. Av. Intel. Sist. 2300554. https://doi.org/10.1002/aisy.202300554

Leitura relacionada

Aumentando a eficiência energética da IA com computação na memória

Como processar cargas de trabalho em escala zeta e permanecer dentro de um orçamento de energia fixo.

Modelagem de computação em memória com eficiência biológica

A IA generativa força os fabricantes de chips a usar recursos computacionais de forma mais inteligente.

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiengineering.com/ferroelectric-tunnel-junctions-in-crossbar-array-analog-in-memory-compute-accelerators/

- :tem

- :é

- $UP

- 10

- 1100

- 2023

- 60

- a

- aceleradores

- Acesso

- precisão

- alcançado

- AI

- e

- aplicações

- arquitetura

- SOMOS

- Ordem

- artificial

- inteligência artificial

- Inteligência artificial (AI)

- AS

- At

- ambos

- orçamento

- mas a

- by

- candidatos

- características

- classificação

- Fechar

- combinação

- Computar

- computação

- consumo

- núcleo

- Atual

- Dezembro

- profundo

- redes neurais profundas

- demonstraram

- densidade

- digital

- dr

- dois

- dinâmico

- eficiência

- elemento

- permitir

- energia

- eficiência energética

- avaliadas

- exposto

- Finalmente

- fixado

- Escolha

- Forças

- ótimo

- Hardware

- Ter

- pesado

- SUA PARTICIPAÇÃO FAZ A DIFERENÇA

- Alta

- altamente

- HTTPS

- identificador

- Impacto

- melhorar

- in

- Instituto

- integração

- Inteligência

- interesse

- para dentro

- investigação

- Chave

- grande

- Latência

- saltos

- Nível

- níveis

- limitações

- Baixo

- Memória

- modificada

- mais

- nação

- redes

- Neural

- redes neurais

- Novo

- objeto

- of

- on

- aberto

- Papel

- Paralelo

- particular

- atuação

- platão

- Inteligência de Dados Platão

- PlatãoData

- potencial

- poder

- Prime

- processo

- programável

- fornecido

- fornecendo

- publicado

- propósito

- R

- alcance

- realização

- exige

- pesquisadores

- Recursos

- Ciência

- Ciência e Tecnologia

- visto

- de forma considerável

- velocidade

- Unidos

- ficar

- .

- Dados Técnicos:

- Tecnologia

- A

- deles

- isto

- intitulado

- para

- Training

- verdadeiro

- túnel

- universidade

- sobre

- usar

- utilização

- de

- foi

- de

- dentro

- Atividades:

- zefirnet