Um artigo técnico intitulado “WWW: What, When, Where to Compute-in-Memory” foi publicado por pesquisadores da Purdue University.

Abstrato:

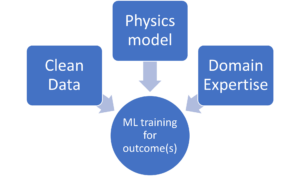

“A computação na memória (CiM) surgiu como uma solução atraente para aliviar os altos custos de movimentação de dados em máquinas von Neumann. CiM pode realizar operações de multiplicação geral de matrizes massivamente paralelas (GEMM) na memória, a computação dominante na inferência de aprendizado de máquina (ML). No entanto, redirecionar a memória para computação levanta questões importantes sobre 1) Que tipo de CiM usar: Dada uma infinidade de CiMs analógicos e digitais, é necessário determinar sua adequação do ponto de vista dos sistemas. 2) Quando usar CiM: a inferência de ML inclui cargas de trabalho com uma variedade de requisitos de memória e computação, tornando difícil identificar quando o CiM é mais benéfico do que os núcleos de processamento padrão. 3) Onde integrar CiM: Cada nível de memória tem largura de banda e capacidade diferentes, o que afeta a movimentação de dados e os benefícios de localidade da integração CiM.

Neste artigo, exploramos as respostas a essas perguntas sobre a integração CiM para aceleração de inferência de ML. Usamos o Timeloop-Accelergy para avaliação inicial em nível de sistema de protótipos CiM, incluindo primitivos analógicos e digitais. Integramos CiM em diferentes níveis de memória cache em uma arquitetura de linha de base semelhante à Nvidia A100 e adaptamos o fluxo de dados para várias cargas de trabalho de ML. Nossos experimentos mostram que as arquiteturas CiM melhoram a eficiência energética, alcançando até 0.12x menos energia do que a linha de base estabelecida com precisão INT-8 e ganhos de desempenho de até 4x com intercalação e duplicação de peso. O trabalho proposto fornece insights sobre que tipo de CiM usar e quando e onde integrá-lo de maneira ideal na hierarquia de cache para aceleração GEMM.”

Encontre o artigo técnico aqui. Publicado em dezembro de 2023 (pré-impressão).

Sharma, Tanvi, Mustafa Ali, Indranil Chakraborty e Kaushik Roy. “WWW: O quê, quando, onde calcular na memória.” Pré-impressão arXiv arXiv:2312.15896 (2023).

Leitura relacionada

Aumentando a eficiência energética da IA com computação na memória

Como processar cargas de trabalho em escala zeta e permanecer dentro de um orçamento de energia fixo.

Modelagem de computação em memória com eficiência biológica

A IA generativa força os fabricantes de chips a usar recursos computacionais de forma mais inteligente.

SRAM em IA: o futuro da memória

Por que a SRAM é vista como um elemento crítico em arquiteturas de computação novas e tradicionais.

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiengineering.com/cim-integration-for-ml-inference-acceleration/

- :tem

- :é

- :onde

- $UP

- 1

- 2023

- a

- aceleração

- alcançar

- AI

- aliviar

- an

- e

- respostas

- arquitetura

- AS

- At

- Largura de Banda

- Linha de Base

- benéfico

- Benefícios

- ambos

- orçamento

- by

- esconderijo

- CAN

- Capacidade

- atraente

- computação

- Computar

- custos

- crítico

- dados,

- Dezembro

- determinando

- diferente

- difícil

- digital

- dominante

- cada

- Cedo

- eficiência

- elemento

- emergiu

- energia

- eficiência energética

- estabelecido

- avaliação

- experimentos

- explorar

- fixado

- Escolha

- Forças

- da

- futuro

- Ganhos

- Geral

- dado

- SUA PARTICIPAÇÃO FAZ A DIFERENÇA

- hierarquia

- Alta

- Contudo

- HTTPS

- identificar

- melhorar

- in

- inclui

- Incluindo

- insights

- integrar

- integração

- para dentro

- IT

- jpg

- Chave

- aprendizagem

- Nível

- níveis

- diminuir

- máquina

- aprendizado de máquina

- máquinas

- Fazendo

- massivamente

- Matriz

- Memória

- ML

- mais

- movimento

- multidão

- necessário

- Novo

- Nvidia

- of

- on

- aberto

- Operações

- A Nossa

- Papel

- Paralelo

- realizar

- atuação

- perspectiva

- platão

- Inteligência de Dados Platão

- PlatãoData

- coloca

- poder

- Precisão

- processo

- em processamento

- proposto

- protótipos

- fornece

- publicado

- Frequentes

- em relação a

- Requisitos

- pesquisadores

- Recursos

- roy

- mostrar

- solução

- padrão

- ficar

- aptidão

- sistemas

- Dados Técnicos:

- do que

- que

- A

- O Futuro

- deles

- Este

- isto

- intitulado

- para

- tradicional

- tipo

- universidade

- usar

- variedade

- vário

- visto

- de

- foi

- we

- peso

- O Quê

- quando

- de

- dentro

- Atividades:

- zefirnet