Prevenir a propagação de defeitos sistemáticos no processo atual de projeto até fabricação de semicondutores requer muitas etapas de validação, análise e otimização. As ferramentas envolvidas neste processo podem incluir verificação de regras de projeto (DRC), verificação de correção de proximidade óptica (OPC), escrita de máscara e metrologia/inspeção de impressão de wafer (para avaliar o processo), metrologia/inspeção de impressão de wafer e análise de falha física para confirmar a falha. diagnóstico. A troca de informações e a co-otimização entre essas etapas é um processo complexo, com muitos ciclos de feed-forward e feedback. A comunicação é muitas vezes dificultada por “paredes” entre várias partes da tecnologia de processo, retardando a inovação. Na recente conferência SPIE, a Siemens EDA apresentou um discurso que propôs uma série de abordagens para derrubar essas barreiras e melhorar o design do chip para o processo de fabricação. Continue lendo para ver como a Siemens pretende quebrar as barreiras da inovação, ampliando a co-otimização da tecnologia de design.

Sobre a palestra

SPIE é a sociedade internacional de óptica e fotônica. A organização remonta a 1955 e sua conferência tornou-se um evento importante para tópicos avançados de design e fabricação. No evento deste ano, a Siemens apresentou a palestra que é o tema deste post. Houve muitos colaboradores na apresentação, incluindo Le Hong, Fan Jiang, Yuansheng Ma, Srividya Jayaram, Joe Kwan, Siemens EDA (Estados Unidos); Doohwan Kwak, Siemens EDA (República da Coreia); Sankaranarayanan Paninjath Ayyappan, Siemens EDA (Índia). O título da palestra foi Estendendo a cootimização da tecnologia de design desde o lançamento da tecnologia até HVM.

A palestra fez parte de uma sessão sobre co-otimização de tecnologia de design (DTCO). Este conceito não é novo, mas a Siemens analisou a sua aplicação num âmbito mais amplo do processo, desde o design até à produção em grande escala (HVM). As ideias e resultados apresentados têm implicações significativas. Vamos olhar mais de perto.

O que foi apresentado

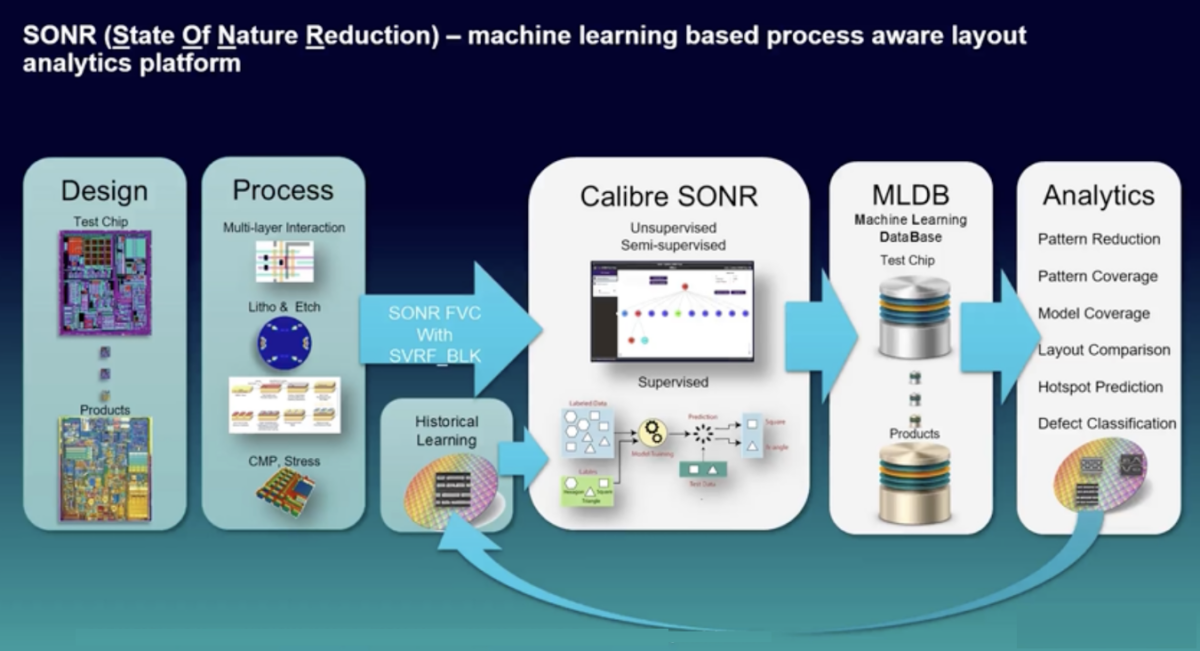

Primeiro, foi apresentada uma análise do estado atual do uso do DTCO nas principais partes do ecossistema. Do ponto de vista do design, muitas empresas avançadas sem fábrica têm uma equipe de DFM que está vendo os limites de uma abordagem baseada em padrões. O que é realmente necessário é uma nova tecnologia que facilite a aprendizagem do rendimento sem dependência da fundição.

As fundições estão usando abordagens de aprendizado de máquina baseadas em padrões de força bruta, que são caras, mas não totalmente eficazes. Eles também buscam uma mineração eficiente de informações dos enormes dados de produção que criam. Os fornecedores de equipamentos e os fornecedores de EDA têm trabalhado em conjunto e estão criando soluções de aprendizado de máquina mais eficientes.

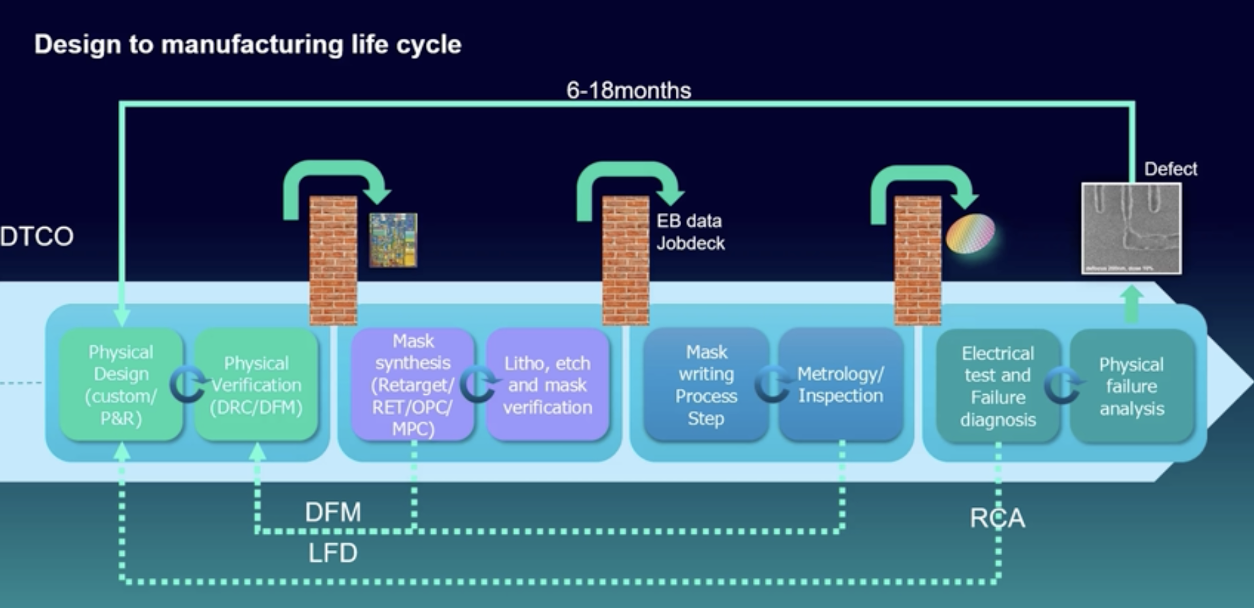

Recuando um pouco, foi apontado que existem paredes entre as fases de projeto e fabricação do processo. As empresas Fabless criam o projeto, executam o DRC e o projeto para fabricação (DFM) e, em seguida, lançam-no por cima do muro para a equipe OPC/RET dentro da fundição ou IDM. O projeto realiza tarefas como OPC e verificação e, em seguida, os dados são jogados sobre outra parede para escrita de máscara e metrologia/inspeção. A parede final é para fabricação. Aqui serão feitos testes elétricos e análise de falhas. No momento em que a causa raiz da falha é encontrada, já se passaram de 6 a 18 meses. Esse é um ciclo de feedback muito longo. O gráfico no topo desta postagem descreve esse processo.

O DTCO tenta derrubar os muros, mas as metodologias disponíveis são incompletas. O DTCO tradicional começa bem cedo no desenvolvimento do processo. Começando com uma necessidade de escala, uma célula padrão é definida e síntese, local e rota são realizados para chegar a padrões básicos e medir o desempenho e a potência. A produção de SRAM também é feita e os dados retornam ao design de célula padrão.

O que foi apresentado na palestra da SPIE foi uma forma de estender este conceito de co-otimização a todo o processo, desde a concepção até à produção. A abordagem envolve permitir um fluxo mais fácil de informações desde o projeto até o processo final e análise física, criando um canal de informações.

Embora isso pareça simples, não é. Muitos desafios foram discutidos com abordagens concretas para mitigar os problemas. Por exemplo, projetos iniciais podem ser criados com geradores sintéticos de layout para ajudar a calibrar o processo para questões reais de projeto à medida que o processo é desenvolvido. Isso pode aliviar muitas das surpresas enfrentadas atualmente com as interrupções iniciais do processo.

Lidar com grandes volumes de dados é outro desafio. Usando novas técnicas de compressão sofisticadas, é possível uma melhoria de 30X. Isso melhora bastante as tarefas de manipulação e análise de dados. Um conceito chamado IA explicável pode ajudar a encontrar as causas dos problemas com muito mais rapidez. A capacidade de treinar novamente modelos de IA posteriormente no processo de fabricação sem invalidar resultados anteriores é outra área a ser melhorada. Também na área de análise de dados estão técnicas para lidar com “dados desequilibrados”. Por exemplo, pode haver um ponto quente encontrado em 100,000,000 milhões de padrões.

Juntar tudo isso pode criar um fluxo de design ponta a ponta muito mais eficiente, conforme mostrado na figura abaixo.

Aprender mais

O impacto das abordagens descritas nesta apresentação é substancial. Você pode veja a apresentação e acesse um white paper sobre o processo aqui. Há muitas informações úteis a serem obtidas. E é assim que a Siemens pretende quebrar as barreiras à inovação, ampliando a co-otimização da tecnologia de design.

Compartilhe esta postagem via:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiwiki.com/events/339386-spie-2023-buzz-siemens-aims-to-break-down-innovation-barriers-by-extending-design-technology-co-optimization/

- :tem

- :é

- :não

- $UP

- 000

- 100

- 2023

- a

- habilidade

- Acesso

- em

- endereço

- avançado

- AI

- Modelos de IA

- visa

- Todos os Produtos

- aliviar

- tb

- an

- análise

- e

- Outro

- Aplicação

- abordagem

- se aproxima

- SOMOS

- ÁREA

- AS

- At

- Tentativas

- disponível

- em caminho duplo

- barreiras

- basic

- BE

- tornam-se

- sido

- abaixo

- entre

- Pouco

- Break

- mais amplo

- mas a

- by

- chamado

- CAN

- Causar

- causas

- célula

- desafiar

- desafios

- Canal

- a verificação

- lasca

- mais próximo

- CO

- como

- vinda

- Comunicação

- Empresas

- completamente

- integrações

- conceito

- concreto

- Conferência

- Confirmar

- contribuintes

- dispendioso

- crio

- criado

- Criar

- Atual

- Estado atual

- Atualmente

- dados,

- análise de dados

- Datas

- acordo

- definido

- dependência

- Design

- projetos

- detalhes

- desenvolvido

- Desenvolvimento

- diagnóstico

- discutido

- feito

- down

- drc

- Mais cedo

- Cedo

- mais fácil

- ecossistema

- Eficaz

- eficiente

- permitindo

- end-to-end

- Todo

- equipamento

- Evento

- exemplo

- exchange

- estender

- estendendo

- enfrentou

- facilitar

- Falha

- ventilador

- mais rápido

- retornos

- Figura

- final

- Encontre

- fluxo

- Escolha

- encontrado

- Fundição

- da

- ganhou

- calibre

- geradores

- gráfico

- Manipulação

- Ter

- ajudar

- SUA PARTICIPAÇÃO FAZ A DIFERENÇA

- Hong

- HOT

- Como funciona o dobrador de carta de canal

- HTTPS

- idéias

- Impacto

- implicações

- melhorar

- melhoria

- melhora

- in

- incluir

- Incluindo

- Índia

- INFORMAÇÕES

- Inovação

- Internacionais

- envolvido

- envolve

- questões

- IT

- ESTÁ

- joe

- Chave

- Principal

- Coréia

- mais tarde

- lançamento

- traçado

- APRENDER

- aprendizagem

- limites

- longo

- olhar

- olhou

- lote

- máquina

- aprendizado de máquina

- fabrica

- muitos

- máscara

- maciço

- max-width

- Posso..

- a medida

- metodologias

- Mineração

- Mitigar

- modelos

- mês

- mais

- mais eficiente

- muito

- você merece...

- necessário

- Novo

- of

- frequentemente

- on

- ONE

- ótica

- Óptica e fotônica

- otimização

- or

- organização

- Fora

- delineado

- Acima de

- Papel

- parte

- peças

- passou

- padrões

- realizar

- atuação

- realizada

- perspectiva

- físico

- Lugar

- plataforma

- platão

- Inteligência de Dados Platão

- PlatãoData

- possível

- Publique

- poder

- premier

- apresentação de negócios

- apresentado

- impressão

- problemas

- processo

- propagação

- proposto

- bastante

- Leia

- reais

- clientes

- recentemente

- República

- exige

- Resultados

- raiz

- Rota

- Regra

- dimensionamento

- escopo

- Vejo

- visto

- busca

- Semicondutor

- Série

- Sessão

- mostrando

- Siemens

- periodo

- Retardando

- Sociedade

- Soluções

- sofisticado

- Spot

- padrão

- Comece

- começa

- Estado

- Unidos

- Passos

- substancial

- tal

- surpresas

- síntese

- sintético

- Tire

- Converse

- tarefas

- Profissionais

- técnicas

- Tecnologia

- teste

- que

- A

- então

- Lá.

- Este

- deles

- isto

- tempo

- Título

- para

- hoje

- juntos

- ferramentas

- topo

- tópico

- Temas

- lançar

- jogado

- tradicional

- Unido

- Estados Unidos

- Uso

- informação útil

- utilização

- validação

- vário

- fornecedores

- Verificação

- muito

- via

- volumes

- parede

- foi

- Caminho..

- foram

- O Quê

- O que é a

- qual

- branco

- artigo:

- precisarão

- de

- dentro

- sem

- trabalhar

- escrita

- Produção

- produzindo

- Você

- zefirnet