Designers have many paths for differentiating RISC-V solutions. One path launches into various RISC-V core customizations and extensions per the specification. Another focuses on selecting and assembling IP blocks in a complete system-on-chip (SoC) design around one or more RISC-V cores. A third is emerging: interconnecting RISC-V cores and other IP blocks with a network-on-chip (NoC) instead of a simple bus structure. And it’s not just at the high end – pairing RISC-V cores with NoCs answers many SoC design challenges where data must flow efficiently in any workload using any on-chip protocol.

Performance tiers changing with advanced interconnect schemes

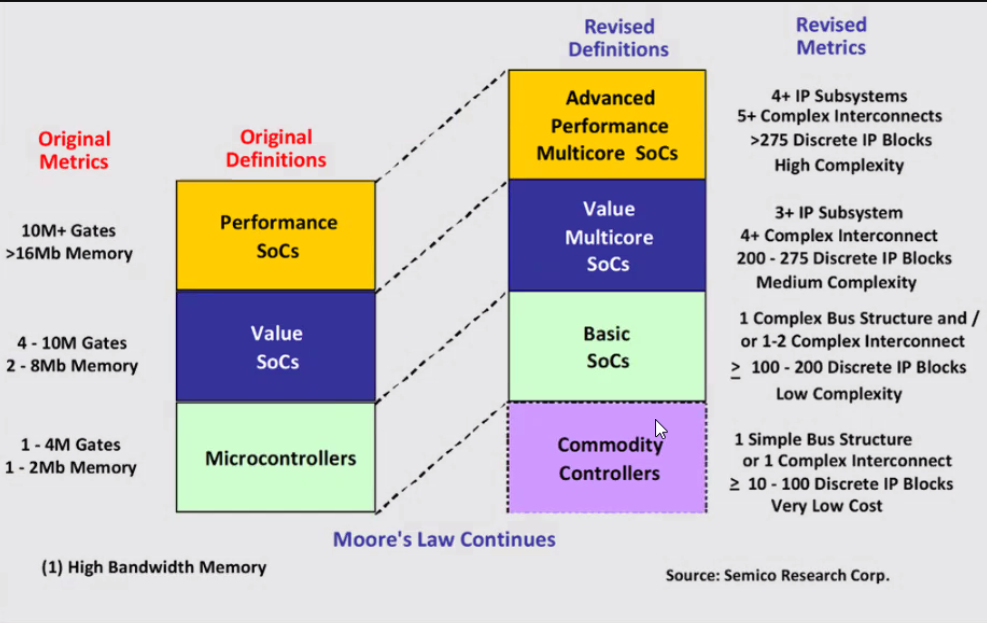

Simply counting gates, cores, and peripheral blocks no longer describes the performance potential of an SoC design. Interconnect schemes now define the lines between SoC performance tiers, according to Semico Research, and a new tier has opened where interconnects change from simple bus structures to more sophisticated schemes.

Semico’s updated definition recognizes three forces at work: the pervasiveness of multicore designs, a higher bar for what is considered a complex design, and the subsequent blurring line between “microcontroller” and “SoC.” In Semico’s latest view, the notion of gate counts as a metric disappears since one modern processor core can drag many gates with it. Complexity becomes a function of interconnects, varying with subsystems and diverse IP blocks.

SoC performance tiers, image courtesy Semico Research Corp.

Where a simple bus will do, likely a part with a single processor core and low-duty-cycle peripherals that aren’t continuously contending for the bus, Semico sees a commodity controller tier. Anything above that becomes an SoC, presumably with at least some peripherals fighting for on-chip bandwidth and attention from the processor core(s). Higher SoC tiers have multiple cores and multiple IP subsystems, each with tuned interconnect technology.

NoCs pick up more protocols and subsystems

RISC-V has quickly moved up these performance tiers as more powerful cores appear, with no less applicability at the lower end of the Semico scale. However, RISC-V designers may have less experience in complex interconnect schemes seen in the higher tiers. “TileLink may be the first thought for RISC-V interconnect, but it can be difficult to use in more complex scenarios,” says Frank Schirrmeister, VP of Solutions and Business Development for Arteris.

A NoC’s superpower is its ability to connect subsystems using different protocols, and SoC designers are likely to run into several protocols at even moderate complexity. AXI leveled the playing field for simple IP block connections. Multicore solutions with co-processing blocks demand cache-coherence, giving rise to the CHI protocol. I/O memory sharing helped shape the faster CXL interconnect. “When it’s time to co-optimize compute and transport with various subsystems and protocols in play, a NoC is a better solution,” continues Schirrmeister.

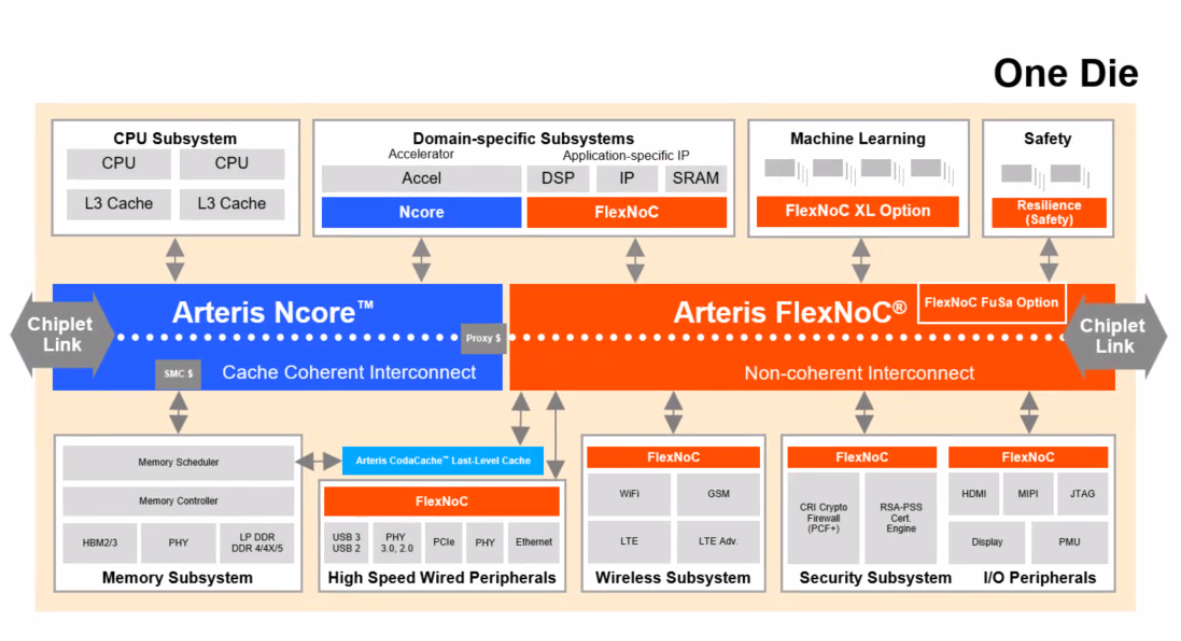

What can pairing RISC-V cores with NoCs look like? Arteris customer Tenstorrent provides a glimpse into the possibilities. Their recent focus is creating a reusable chiplet combining RISC-V cores, machine-learning acceleration IP, and standard peripherals found in many edge AI applications. At scale, a single-die implementation could look like the following diagram, using the Arteris Ncore cache-coherent interconnect and several segments of the Arteris FlexNoC non-coherent interconnect.

image courtesy Arteris

A Smart Memory Controller (SMC) provides a high-performance, server-grade memory connection in memory-intensive applications. The unnamed “chiplet link” could be UCIe, a relatively new specification optimized for tighter chiplet integration. When new subsystem interconnects emerge, adapting a section of the NoC is more manageable than ripping up the entire chip-wide structure.

Pairing RISC-V cores with NoCs lowers risk and time-to-market

If that diagram looks complex, and granted, maybe most RISC-V applications aren’t that complex right now, consider this: chiplets are already driving integration much higher. Today’s advanced RISC-V multicore part will be next year’s value SoC as innovation picks up pace.

Arteris Ncore and Arteris FlexNoC development tools output RTL for implementation, providing several advantages. Physical NoC estimation is straightforward in an EDA workflow. NoC parameter adjustments, such as the number of pipeline stages, are also a few clicks away in EDA tools. The modifications mentioned above for adding a subsystem protocol are also readily accomplished. “At the high end, users gain immediate access to our NoC expertise,” says Schirrmeister. “At the low end, our tools are easy to use for first-pass success and provide a growth path for more ambitious future projects with complex interconnects.”

Pairing RISC-V cores with NoCs lowers the risk of one more IP block entering a design and triggering a ripple of interconnect redesign across the chip. It also reduces time-to-market for complex SoC designs compared to do-it-yourself interconnect structures. We haven’t discussed the other benefits of NoCs here, such as bandwidth and power management, but the case for NoCs in RISC-V designs is strong just considering a diverse protocol mix.

Visit the Arteris website for more information on NoCs and other products.

Share this post via:- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://semiwiki.com/ip/arteris/336086-pairing-risc-v-cores-with-nocs-ties-soc-protocols-together/

- :has

- :is

- :not

- :where

- $UP

- a

- ability

- above

- acceleration

- access

- accomplished

- According

- across

- adding

- adjustments

- advanced

- advantages

- AI

- already

- also

- ambitious

- an

- and

- Another

- answers

- any

- anything

- appear

- applications

- ARE

- around

- AS

- At

- attention

- away

- Bandwidth

- bar

- BE

- becomes

- benefits

- Better

- between

- Block

- Blocks

- bus

- business

- business development

- but

- CAN

- case

- challenges

- change

- changing

- chip

- combining

- commodity

- compared

- complete

- complex

- complexity

- Compute

- Connect

- connection

- Connections

- Consider

- considered

- considering

- continues

- continuously

- controller

- Core

- Corp

- could

- counting

- Creating

- customer

- data

- define

- definition

- Demand

- Design

- designers

- designs

- Development

- development tools

- different

- difficult

- discussed

- diverse

- do

- driving

- each

- easy

- Edge

- efficiently

- emerge

- emerging

- end

- entering

- Entire

- Even

- experience

- expertise

- extensions

- faster

- few

- field

- fighting

- First

- flow

- Focus

- focuses

- following

- For

- Forces

- found

- frank

- from

- function

- future

- Gain

- Gates

- Giving

- Glimpse

- granted

- Growth

- Have

- helped

- here

- High

- high-performance

- higher

- However

- HTTPS

- image

- immediate

- implementation

- in

- information

- Innovation

- instead

- integration

- interconnecting

- interconnects

- into

- IP

- IT

- ITS

- just

- latest

- launches

- least

- less

- like

- likely

- Line

- lines

- longer

- Look

- look like

- LOOKS

- Low

- lower

- management

- many

- max-width

- May..

- maybe

- Memory

- mentioned

- metric

- mix

- moderate

- Modern

- Modifications

- more

- most

- moved

- much

- multiple

- must

- New

- next

- no

- Notion

- now

- number

- of

- on

- ONE

- opened

- optimized

- or

- Other

- our

- output

- Pace

- pairing

- parameter

- part

- path

- per

- performance

- peripheral

- peripherals

- physical

- pick

- Picks

- pipeline

- plato

- Plato Data Intelligence

- PlatoData

- Play

- playing

- possibilities

- Post

- potential

- power

- powerful

- Processor

- Products

- projects

- protocol

- protocols

- provide

- provides

- providing

- quickly

- readily

- recent

- recognizes

- redesign

- reduces

- relatively

- research

- reusable

- right

- Ripple

- Rise

- Risk

- Run

- s

- says

- Scale

- scenarios

- schemes

- Section

- seen

- sees

- segments

- selecting

- several

- Shape

- sharing

- Simple

- since

- single

- smart

- solution

- Solutions

- some

- sophisticated

- specification

- stages

- standard

- straightforward

- strong

- structure

- structures

- subsequent

- success

- such

- superpower

- Technology

- than

- that

- The

- their

- These

- Third

- this

- thought

- three

- tier

- Ties

- tighter

- time

- to

- today’s

- together

- tools

- transport

- triggering

- UNNAMED

- updated

- use

- users

- using

- value

- various

- varying

- via

- View

- vp

- we

- Website

- What

- What is

- when

- will

- with

- Work

- workflow

- zephyrnet