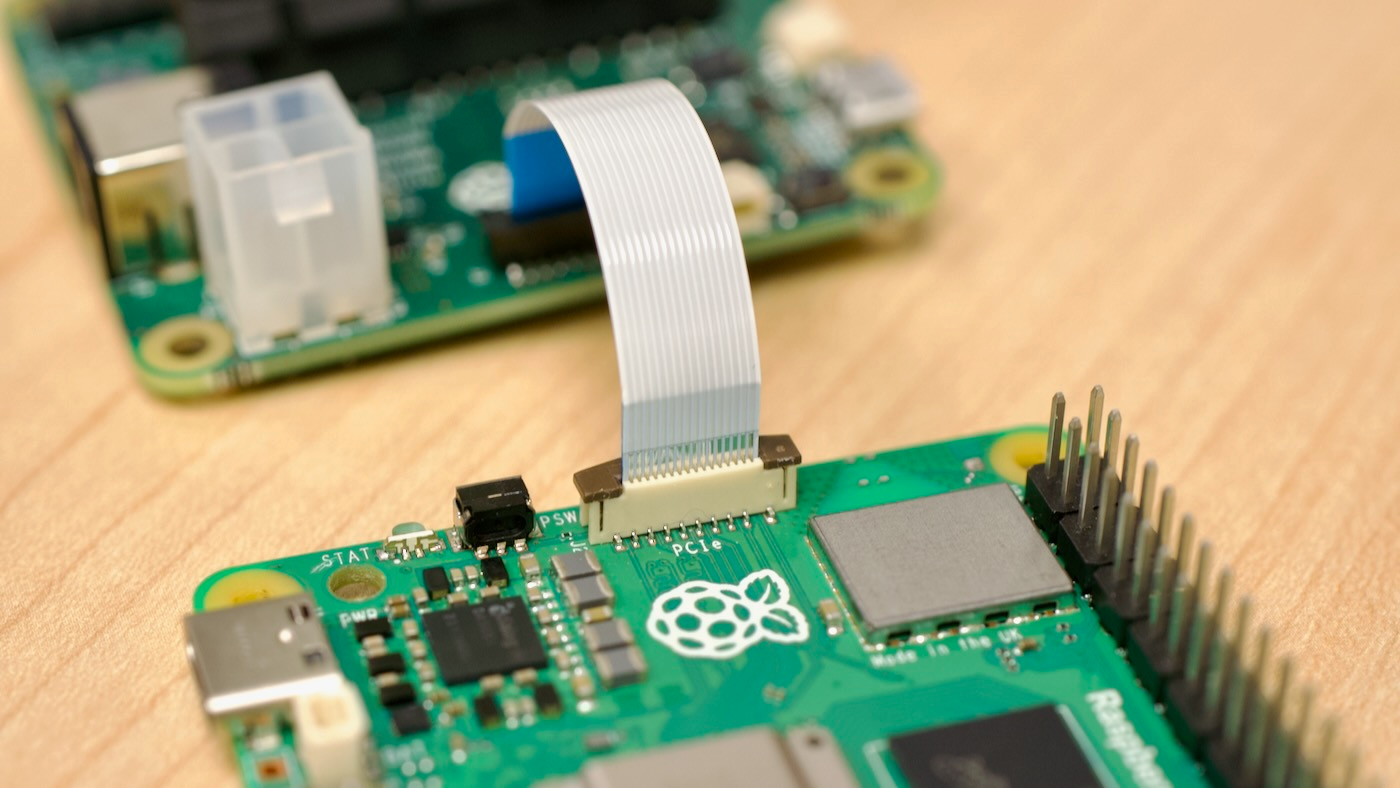

Jeff Geerling has been exploring the PCIe bus on the new Raspberry Pi 5 and has documented some interesting things, some rather unexpected like the ability to change the speed of the PCIe bus.

In my recent Adafruit Blog article PCIe Bandwidth, I discuss the generations the specification has gone through and with each one comes an increase in bus speed. Gen 1.0 was the original and defined a 2.5 gigatransfers per second (GT/s) speed. Gen 2.0 defined 5 GT/s and 3.0 8 GT/s on a single lane (which scales up linearly per number of lanes). The bus is backwards compatible, re. a Gen 1.0 device can work in a Gen 2.0 slot. But a Gen 3.0 device may or may not like that it is in a Gen 2.0 slot, depending on it’s function and driver.

There are 5 active PCIe lanes on the Raspberry Pi 5 with four going to the RP1 chip and one is broken out to the new PCIe connector. Jeff states:

By default, all PCIe lanes operate at Gen 2.0 speeds, or about 5 GT/sec per lane. Currently there’s no way to change that default for the RP1 chip’s ‘internal’ lanes, but on the external connector, you can add the following lines inside

/boot/config.txt(and reboot) to upgrade the connection to Gen 3.0 (8 GT/sec, almost double the speed):dtparam=pciex1 dtparam=pciex1_gen=3And yes, you can also downgrade the connection to Gen 1.0 speeds (2.5 GT/sec) if you like.

Why default to PCIe Gen 2.0?

Why is it defaulted to Gen 2.0? Because that’s the speed at which the board could be certified for PCI Express. Even older standards like 2.0 and 3.0 are considered ‘high speed’ interconnects. And with any connection on a board, interference and signal issues can cause problems with higher bandwidth.

Read much more in Jeff’s article here.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- PlatoData.Network Vertical Generative Ai. Empower Yourself. Access Here.

- PlatoAiStream. Web3 Intelligence. Knowledge Amplified. Access Here.

- PlatoESG. Carbon, CleanTech, Energy, Environment, Solar, Waste Management. Access Here.

- PlatoHealth. Biotech and Clinical Trials Intelligence. Access Here.

- Source: https://blog.adafruit.com/2023/10/13/forcing-pci-express-gen-3-0-speeds-on-the-pi-5-piday-raspberrypi-geerlingguy-raspberry_pi/

- :has

- :is

- :not

- $UP

- 1

- 8

- a

- ability

- About

- active

- add

- All

- almost

- an

- and

- any

- ARE

- article

- At

- Bandwidth

- BE

- because

- been

- Blog

- board

- Broken

- bus

- but

- CAN

- Cause

- Certified

- change

- chip

- comes

- compatible

- connection

- considered

- could

- Currently

- Default

- defined

- Depending

- device

- discuss

- documented

- double

- driver

- each

- Even

- Exploring

- express

- external

- following

- For

- forcing

- four

- function

- Gen

- generations

- going

- gone

- High

- higher

- HTTPS

- i

- if

- in

- Increase

- interconnects

- interesting

- interference

- issues

- IT

- Lane

- like

- lines

- max-width

- May..

- more

- much

- my

- New

- no

- number

- of

- older

- on

- ONE

- operate

- or

- original

- out

- per

- plato

- Plato Data Intelligence

- PlatoData

- problems

- Raspberry

- Raspberry Pi

- rather

- RE

- recent

- scales

- Second

- Signal

- single

- slot

- some

- specification

- speed

- speeds

- standards

- States

- that

- The

- things

- Through

- to

- Unexpected

- upgrade

- was

- Way..

- which

- with

- Work

- yes

- you

- zephyrnet