Non-trivial bug escapes; ML drives domain-specific architectures; 3D-IC thermal analysis.

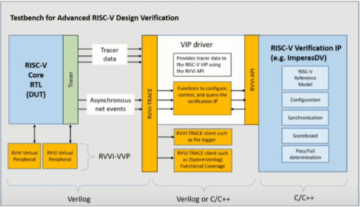

Siemens EDA’s Harry Foster examines the relationship between verification maturity and non-trivial bug escapes into production, as well as whether safety critical development processes yield higher quality in terms of preventing bugs and achieving silicon success.

Synopsys’ Shankar Krishnamoorthy finds that the rapid progress of machine learning models is driving demand for more domain-specific architectures and highlighting how the co-optimization of software and hardware is critical for delivering the future of scalable AI systems.

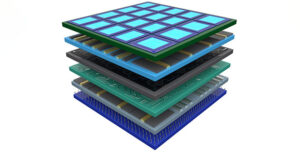

Cadence’s Paul McLellan considers the importance of thermal analysis in 3D-IC designs and the tradeoffs between the power and performance improvements brought by wirelength shortening versus temperature increases due to heat confinement between the two dies.

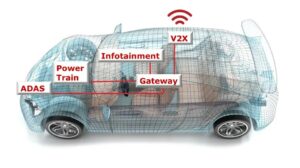

Renesas’ Omer Cheema checks out how the Matter protocol abstracts the underlying connectivity technologies to connect various smart devices with each other, regardless of the brand of the manufacturer and ecosystem.

Ansys’ Edward Carman finds out how multiphysics simulation is being used to design smaller, flexible, collaborative robot arms for industrial equipment that can handle more tasks and assist in more environments.

In a blog for SEMI, Lynceus’ David Meyer argues that AI has largely failed to deliver on its potential to streamline semiconductor manufacturing, despite significant investments in data infrastructure and talent, and what needs to change.

And don’t miss the blogs featured in the latest Low Power-High Performance newsletter:

Quadric’s Steve Roddy questions which silicon market segment machine learning will disrupt in 2023.

Rambus’ Joseph Rodriguez and Simon Bussières explain why using visually lossless video compression cuts the number of MIPI transport lanes required for displays.

Siemens EDA’s Darron May finds that data from regression runs can suggest starting points for debug.

Synopsys’ Charlie Matar, Rita Horner, and Pawini Mahajan show how silicon lifecycle management can be used to ensure data center system uptime.

Ansys’ Arien Sligar looks at augmenting neural network training with artificially generated data that mimics the behavior of real-world systems.

Arm’s Nicolas Devillard digs into how smart home devices and servers communicate about, validate, and apply new firmware versions using Matter.

Cadence’s Anika Sunda examines simulation regression optimization while preserving coverage with AI.

Jesse Allen

(all posts)

Jesse Allen is the Knowledge Center administrator and a senior editor at Semiconductor Engineering.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Source: https://semiengineering.com/blog-review-feb-15-2/

- 2023

- 28

- 7

- a

- About

- abstracts

- achieving

- AI

- AI systems

- All

- All Posts

- analysis

- and

- Apply

- Argues

- assist

- being

- between

- Blog

- blogs

- brand

- brought

- Bug

- bugs

- Cadence

- Center

- change

- Checks

- collaborative

- communicate

- Connect

- Connectivity

- considers

- coverage

- critical

- cuts

- data

- Data Center

- data infrastructure

- deliver

- delivering

- Demand

- Design

- designs

- Despite

- Development

- Devices

- displays

- Disrupt

- Dont

- driving

- each

- ecosystem

- editor

- Engineering

- ensure

- environments

- equipment

- Ether (ETH)

- Examines

- Explain

- Failed

- featured

- finds

- flexible

- from

- future

- generated

- handle

- Hardware

- higher

- highlighting

- Home

- How

- HTTPS

- importance

- improvements

- in

- Increases

- industrial

- industrial equipment

- Infrastructure

- Investments

- knowledge

- largely

- latest

- learning

- LOOKS

- machine

- machine learning

- management

- Manufacturer

- manufacturing

- Market

- Matter

- maturity

- ML

- models

- more

- needs

- network

- Neural

- neural network

- New

- number

- optimization

- Other

- performance

- plato

- Plato Data Intelligence

- PlatoData

- points

- popularity

- Posts

- potential

- power

- preventing

- processes

- Production

- Progress

- protocol

- quality

- Questions

- rapid

- real world

- Regardless

- regression

- relationship

- required

- review

- robot

- ROW

- Safety

- scalable

- segment

- Semi

- semiconductor

- senior

- show

- Siemens

- significant

- Silicon

- Simon

- simulation

- smaller

- smart

- Smart home

- smart home devices

- Software

- Starting

- streamline

- success

- system

- Systems

- Talent

- tasks

- Technologies

- terms

- The

- The Future

- thermal

- thumbnail

- to

- Training

- transport

- underlying

- uptime

- VALIDATE

- various

- Verification

- Versus

- Video

- What

- whether

- which

- while

- will

- Yield

- zephyrnet