Transformers for vision; digital twins and PCBs; formal for RISC-V; smaller smartphone cameras.

Synopsys’s Gordon Cooper argues that AI transformer models, initially developed for natural language processing such as translation and question answering, are starting to make inroads in the computer vision application landscape and changing the direction of deep-learning architectures.

Siemens’ Patrick Hope shows how to identify opportunities to optimize a PCB design through the creation of a digital twin simulation that leverages data from across the supply chain.

Cadence’s Veena Parthan checks out how aerodynamic simulation was used in designing solar-powered cars for a race across the Australian outback.

Codasip’s Laurent Arditi explains why and how to use formal verification with RISC-V to verify the architectural compliance of a processor, identify corner cases, and find bugs that depend on precise timing conditions.

Ansys’ Kerry Herbert checks out using diffractive gratings in place of certain lenses to help meet the performance challenges of miniaturized smartphone camera systems and how optical simulation software works together with parallel manufacturing advancements in precision tooling.

Renesas’ Roger Wendelken discusses discuss the evolving MCU market and shares thoughts on nurturing a user-friendly customer design ecosystem and the impact of AI on MCU component selection and design flows.

Arm’s Eric Sondhi shows how virtual hardware prototyping and a remote access and management platform for IoT devices allows developers to test and debug applications in a virtual environment, while also remotely controlling and monitoring devices.

Keysight’s Elizabeth Fei points to key aspects of testing USB Type-C cables as the increased bit rates of 40 Gbps to support the USB4 protocol brings additional signal integrity challenges and introduces more stringent requirements.

SEMI’s John Cooney explains some of the national security guardrails included in the CHIPS Act that aim to prevent funding from passing to foreign entities of concern and establish agreements with funded companies limiting their expansion into certain countries.

For a change from reading, check out a recent video:

Configurable security strategies need to be designed into devices and monitored throughout their lifetimes, in Adding Security Into Test.

Factors that need to be considered to improve reliability at higher speeds and the Impact Of Increased IC Performance On Memory.

How to build a better network on chip with Physically Aware NoCs.

Why Zero Trust Security In Chip Manufacturing is becoming so critical.

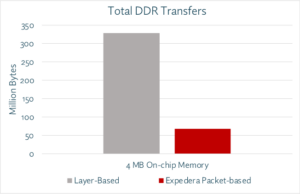

Where Power Is Spent In HBM and what really happens when you shorten the distance to memory.

Different memory options for different devices and how to Choose The Right Memory At The Edge.

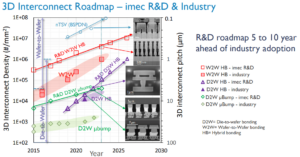

Advantages and challenges for heterogeneous integration in advanced packaging and Multi-Die Integration.

How to work with the new RISC-V debug standard for Efficient Trace In RISC-V.

Increased Photomask Density And Its Impact On EDA, plus why curvilinear shapes can simplify design rules for chip manufacturing.

Understanding Silent Data Corruption is necessary to prevent defects that can cause errors.

Advantages of bridging different ecosystems in the smart home and Why Matter 1.0 Really Matters.

Jesse Allen

(all posts)

Jesse Allen is the Knowledge Center administrator and a senior editor at Semiconductor Engineering.

- SEO Powered Content & PR Distribution. Get Amplified Today.

- Platoblockchain. Web3 Metaverse Intelligence. Knowledge Amplified. Access Here.

- Source: https://semiengineering.com/blog-review-april-5-2/

- :is

- 1

- 28

- 7

- a

- access

- across

- Act

- Additional

- advanced

- advancements

- agreements

- AI

- All

- All Posts

- allows

- and

- Application

- applications

- April

- architectural

- ARE

- Argues

- ARM

- AS

- aspects

- At

- Australian

- BE

- becoming

- Better

- Bit

- Blog

- bridging

- Brings

- bugs

- build

- cables

- Cadence

- camera

- cameras

- CAN

- cars

- cases

- Cause

- Center

- certain

- chain

- challenges

- change

- changing

- check

- Checks

- chip

- Chips

- CHIPS Act

- Companies

- compliance

- component

- computer

- Computer Vision

- Concern

- conditions

- considered

- controlling

- Corner

- countries

- creation

- critical

- customer

- data

- density

- Design

- designed

- designing

- developed

- developers

- Devices

- different

- digital

- digital twin

- Digital twins

- direction

- discuss

- distance

- ecosystem

- Ecosystems

- editor

- Engineering

- entities

- entry

- Environment

- Errors

- establish

- Ether (ETH)

- evolving

- expansion

- Explains

- Find

- Flows

- For

- foreign

- formal

- from

- funded

- funding

- happens

- Hardware

- help

- higher

- Home

- How

- How To

- HTML

- HTTPS

- identify

- Impact

- improve

- in

- included

- increased

- initially

- integration

- integrity

- Introduces

- iot

- iot devices

- ITS

- jpg

- Key

- knowledge

- landscape

- language

- lenses

- leverages

- make

- management

- manufacturing

- Market

- Matter

- MCU

- Meet

- Memory

- models

- monitored

- monitoring

- more

- National

- national security

- Natural

- Natural Language

- Natural Language Processing

- necessary

- Need

- network

- New

- of

- on

- opportunities

- Optimize

- Options

- packaging

- Parallel

- Passing

- PCBs

- performance

- Place

- platform

- plato

- Plato Data Intelligence

- PlatoData

- plus

- points

- popularity

- Posts

- power

- precise

- Precision

- prevent

- processing

- Processor

- protocol

- prototyping

- question

- Race

- Rates

- Reading

- reliability

- remote

- remote access

- Requirements

- review

- ROW

- rules

- security

- selection

- Semi

- semiconductor

- senior

- shapes

- Shares

- Shows

- Siemens

- Signal

- simplify

- simulation

- smaller

- smart

- Smart home

- smartphone

- So

- Software

- solar-powered

- some

- speeds

- spent

- standard

- Starting

- strategies

- such

- supply

- supply chain

- support

- Systems

- test

- Testing

- that

- The

- their

- Through

- throughout

- thumbnail

- timing

- to

- together

- trace

- Translation

- Trust

- Twins

- usb

- use

- user-friendly

- Verification

- verify

- Virtual

- vision

- What

- while

- with

- Work

- works

- zephyrnet