Ostatnią sesją podczas niedawnego szczytu RISC-V był panel poświęcony chipletom Chiplety w ekosystemie RISC-V. Moderatorką była Calista Redmond, dyrektor generalna RISC-V International. Panelistami byli:

- Laurent Moll, dyrektor operacyjny Arteris

- Aniket Saha, wiceprezes ds. zarządzania produktami w Tenstorrent

- Dale Greenley, wiceprezes ds. inżynierii w firmie Ventana Microsystems

- Rob Aitken, wybitny architekt Synopsys

Dla mnie to trochę dziwne połączenie tematów. Oczywiście można umieścić procesor RISC-V na chiplecie, ale wyzwania nie różnią się tak naprawdę od innych procesorów. Ale RISC-V jest popularny, podobnie jak chiplety, i firmy takie jak Ventana je łączą.

Pozwólcie, że przedstawię wam trochę tła na temat firm, aby umieścić je w kontekście:

- Jak zapewne wiesz, Arteris tworzy sieci na chipie (NoC). Jest firmą neutralną wśród dostawców chipletów (i dostawców IP).

- Tenstorrent projektuje portfolio bardzo wydajnych wielordzeniowych chipów RISC-V

- Ventana ma protokół IP RISC-V, ale dostarcza go również w postaci chipletów

- Synopsys jest oczywiście firmą należącą do EDA, ale wcześniej na szczycie zapowiedziała rdzenie RISC-V

]

Rzeczywista dyskusja

Pierwszym pytaniem zadanym przez Calistę był softball z pytaniem, jaka jest wartość chipsetów.

Dale powiedział, że nie ma nic konkretnego na temat RISC-V dla chipletów, ale to rynek decyduje, kiedy robisz duże, monolityczne rzeczy lub chiplety. To zależy od tego, za co klient zapłaci. „Dostarczamy zarówno IP, jak i chiplety, jest miejsce na jedno i drugie.”

Aniket powiedział, że „robienie chipsetów nie jest tanie, ale robienie chipsetów i RISC-V jest elastyczne i można szybko wymyślić gotowe produkty”.

Laurent poszedł w stronę kosztów produkcji. Bardzo ważne jest, aby NRE było pod kontrolą, ponieważ niewiele osób buduje 100 milionów części. Zatem zaangażowanych jest więcej dostawców i skomplikowany łańcuch dostaw. SoC jest złożony, ale chiplety są gorsze.

Rob zwrócił uwagę na heterogeniczność, taką jak dodanie chipletów dla RF i analogowych, posiadanie opcjonalnego akceleratora i tak dalej. To potencjalnie otwiera nowe rynki.

Calista zapytała dalej, na jakim etapie rozwoju motoryzacji jesteśmy.

Aniket zwrócił uwagę, że branża motoryzacyjna jest bardzo konserwatywna i obecnie agresywnie podchodzi do platform, które można skalować od samochodów z niższej półki do samochodów z najwyższej półki. W przypadku chipletów nikt tak naprawdę nie wziął pod uwagę bezpieczeństwa funkcjonalnego.

Rob zajmował się lotnictwem (nie do końca motoryzacyjnym) i omawiał, w jaki sposób istnieje zwykle stała objętość fizyczna zdefiniowana kilkadziesiąt lat temu. Ciężko jest coś dopasować.

Laurent: Firmy motoryzacyjne to najchętniej kupcy katalogowi, a chiplety pozwalają im korzystać z tego, co najlepsze w zakresie sztucznej inteligencji, radarów, rozwiązań informacyjno-rozrywkowych i tak dalej.

Jak uruchomić oprogramowanie?

Rob: Jeśli sprawisz, że system będzie mały, to w porządku. Ale zakupy w katalogu motoryzacyjnym utrudniają to.

Aniket: Powiązał ze stwierdzeniem „jeśli to dodasz, nie będziemy go używać”. Stosy oprogramowania motoryzacyjnego będą obsługiwać RISC-V za 5 lat, czyli szybko. Dotarcie tam zajęło Armowi 15 lat.

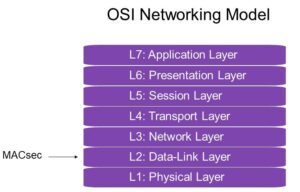

P: Czego potrzebujemy do łączności?

Laurent: Jest to bardzo skomplikowane, szczególnie w przypadku ludzi kupujących chipsety. Fizyki PHY od różnych dostawców mogą być interoperacyjne. Wszyscy są zainteresowani UCIe. Ludzie chcą standardów, dzięki którym chiplety będą lepiej dopasowane.

Aniket skarżył się, że nie ma standardowych przepływów projektowych dla chipletów. Duży brak standardów.

Rob uważa, że możemy wymyślić standardowy przepływ, ale w przypadku różnych chipletów nie chcemy N różnych przepływów projektowych.

P: Jak widzisz sytuację za 3-5 lat?

Rob: Będziemy dalej, razem z innymi

„Zakupy katalogowe mogą zależeć od producentów OEM z branży motoryzacyjnej. Będzie to wymagało dużego wysiłku branży. Wszelkie heterogeniczne rzeczy będą trwać dłużej.

Aniket powiedział, że chiplety będą najpierw dostępne w centrach danych, a następnie w motoryzacji. Ale pierwsza fala będzie dotyczyć jednego dostawcy.

Podsumowanie

Jest to połączenie tego, co powiedzieli uczestnicy i moich własnych opinii.

Myślę, że na razie projekty RISC-V oparte na chipletach będą dziełem jednej firmy (być może z wyjątkiem pamięci o dużej przepustowości (HBM). Tworzenie projektów z wieloma chipletami różnych firm, interposerami jest zbyt skomplikowane. oraz sieć łączącą je wszystkie, zwykle nazywaną RDL.

W dającej się przewidzieć przyszłości projekty będą wykonane w technologii 2.5D, a nie w prawdziwym 3D (gdzie matryce są ułożone jedna na drugiej i komunikują się z przelotkami krzemowymi lub TSV).

Motoryzacja ma swój własny zestaw wyzwań, w szczególności zapewnienie niezawodności projektów opartych na chipletach w środowisku o dużych wibracjach. Będzie to wymagało szeroko zakrojonych testów. Kolejną kwestią jest zapewnienie bezpieczeństwa funkcjonalnego w środowisku wielu matryc.

UCIe jest obiecujący i w pewnym stopniu opiera się na PCIe. Firmy PCIe zapewniły niezawodność poprzez plugfesty. Nie rozumiem, w jaki sposób można ekonomicznie zapewnić interoperacyjność UCIe w chipletach za pomocą podobnego mechanizmu.

Wreszcie, oprócz wyzwań technicznych, istnieją wyzwania komercyjne, jeśli mamy osiągnąć nirwanę polegającą na możliwości zakupu gotowych chipletów i montażu ich w systemy po rozsądnych kosztach. Największym wyzwaniem jest to, kto zapłaci i będzie utrzymywał zapasy chipletów. Jeżeli wszystkie chiplety będą musiały być produkowane na żądanie, wówczas wiele zalet związanych z krótkim czasem cyklu zostanie utraconych.

Jednak chiplety RISC-V z pewnością będą pojawiać się szybko w postaci projektów z wieloma matrycami i wstawkami 2.5D zbudowanymi przez jedną firmę.

Przeczytaj także:

NoC zapewniają architektom elastyczność w projektowaniu systemów RISC-V

Parowanie rdzeni RISC-V z NoC łączy protokoły SoC

Aktualizacja #60DAC od Arteris

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/arteris/338888-risc-v-and-chiplets-a-panel-discussion/

- :ma

- :Jest

- :nie

- :Gdzie

- $W GÓRĘ

- 100M

- 15 roku

- 15%

- 167

- 200

- 300

- 3d

- a

- Zdolny

- O nas

- akcelerator

- rzeczywisty

- Dodaj

- dodanie

- dodatek

- Zalety

- Lotnictwo

- agresywny

- temu

- AI

- Wszystkie kategorie

- wzdłuż

- również

- wśród

- an

- i

- ogłosił

- Inne

- każdy

- architekci

- SĄ

- ARM

- na około

- AS

- zapytać

- pytanie

- At

- motoryzacyjny

- tło

- na podstawie

- BE

- jest

- BEST

- Ulepsz Swój

- Duży

- Najwyższa

- Bit

- obie

- budować

- Budowanie

- wybudowany

- ale

- by

- nazywa

- CAN

- samochody

- katalog

- ceo

- na pewno

- łańcuch

- wyzwanie

- wyzwania

- tani

- kolor

- połączenie

- łączenie

- jak

- przyjście

- handlowy

- komunikować

- Firmy

- sukcesy firma

- kompleks

- skomplikowane

- Skontaktuj się

- Łączność

- konserwatywny

- za

- kontekst

- kontrola

- gruchanie

- Koszty:

- Koszty:

- klient

- cykl

- Datacenter

- lat

- zdefiniowane

- dostarcza

- W zależności

- zależy

- Wnętrze

- projektowanie

- projekty

- Umierać

- różne

- omówione

- dyskusja

- Wybitny

- do

- robi

- nie

- każdy

- Wcześniej

- wysiłek

- zakończenia

- Inżynieria

- zapewnić

- zapewnione

- zapewnienie

- Środowisko

- szczególnie

- wszyscy

- Z wyjątkiem

- rozległy

- FAST

- w porządku

- i terminów, a

- dopasować

- ustalony

- Elastyczność

- elastyczne

- pływ

- Przepływy

- W razie zamówieenia projektu

- przewidywalny

- Nasz formularz

- od

- funkcjonalny

- dalej

- przyszłość

- otrzymać

- Dać

- Ciężko

- trudniej

- Have

- mający

- Wysoki

- wysoka wydajność

- przytrzymaj

- HOT

- W jaki sposób

- HTTPS

- i

- if

- ważny

- in

- przemysł

- na świecie

- Interoperacyjność

- interoperacyjne

- najnowszych

- inwentarz

- zaangażowany

- IP

- problem

- IT

- JEGO

- jpg

- Zapalony

- Trzymać

- Wiedzieć

- znany

- Brak

- Nazwisko

- niech

- lubić

- dłużej

- stracił

- Partia

- niski

- robić

- WYKONUJE

- i konserwacjami

- zrobiony fabrycznie

- wiele

- wielu ludzi

- rynek

- rynki

- Maksymalna szerokość

- Może..

- może

- me

- mechanizm

- Monolityczny

- jeszcze

- wielokrotność

- my

- Potrzebować

- sieć

- Neutralny

- Nowości

- Nie

- nic

- już dziś

- of

- on

- Na żądanie

- ONE

- otwiera

- Opinie

- or

- Inne

- na zewnątrz

- własny

- płyta

- panel dyskusyjny

- Uczestnicy

- szczególny

- strony

- Zapłacić

- Ludzie

- może

- fizyczny

- Platformy

- plato

- Analiza danych Platona

- PlatoDane

- teczka

- Post

- potencjalnie

- prawdopodobnie

- Procesor

- Produkt

- zarządzanie produktem

- Produkcja

- Produkty

- obiecujący

- protokoły

- zapewniać

- zakup

- położyć

- pytanie

- całkiem

- radar

- Czytaj

- naprawdę

- rozsądny

- niedawny

- związane z

- niezawodność

- rzetelny

- wymagać

- Pokój

- run

- Bezpieczeństwo

- Powiedział

- Skala

- widzieć

- Sesja

- zestaw

- Kupujący

- Zakupy

- podobny

- ponieważ

- pojedynczy

- mały

- So

- Tworzenie

- nieco

- specyficzny

- ułożone w stos

- Półki na książki

- standard

- standardy

- Zestawienie sprzedaży

- Szczyt

- Dostawa

- łańcuch dostaw

- wsparcie

- system

- systemy

- Brać

- rozmawiać

- Techniczny

- Testowanie

- że

- Połączenia

- Im

- następnie

- Tam.

- one

- rzeczy

- myśleć

- Myśli

- to

- Przez

- Krawaty

- czas

- do

- także

- wziął

- Top

- tematy

- prawdziwy

- ostateczny

- dla

- Aktualizacja

- posługiwać się

- zazwyczaj

- wartość

- sprzedawca

- sprzedawców

- początku.

- przez

- Tom

- vp

- chcieć

- była

- fala

- we

- poszedł

- były

- Co

- jeśli chodzi o komunikację i motywację

- który

- KIM

- będzie

- w

- gorzej

- lat

- ty

- zefirnet