Chiplety zaczynają mieć wpływ na projektowanie chipów, mimo że nie są jeszcze głównym nurtem i nie istnieje żaden komercyjny rynek dla tego rodzaju wzmocnionych własności intelektualnej.

Trwają dyskusje na temat zarządzania cyklem życia krzemu, najlepszego sposobu charakteryzowania i łączenia tych urządzeń oraz radzenia sobie z takimi problemami, jak nierównomierne starzenie się i niedopasowanie termiczne. Ponadto trwają intensywne prace nad poprawą obserwowalności chiplety z biegiem czasu jest to szczególnie ważne, ponieważ urządzenia te są wykorzystywane w zastosowaniach o krytycznym znaczeniu dla bezpieczeństwa i działalności firmy.

Wszystkie te problemy muszą zostać rozwiązane, aby umożliwić powszechne przyjęcie, a branża chipów zdała sobie sprawę, że spowolnienie prawa Moore'a w połączeniu ze stałymi rozmiarami siatki będzie wymagało zmian w sposobie projektowania, wytwarzania i pakowania chipów. Fizycznie niemożliwe jest zmieszczenie wszystkich funkcji wymaganych w wielu aplikacjach w jednym SoC, a obecnie celem jest uporządkowane, przewidywalne i powtarzalne podejście do dezagregacji wielu z tych komponentów. Teoretycznie umożliwi to łatwiejsze dostosowywanie urządzeń, skróci czas wprowadzenia produktu na rynek i pozwoli uniknąć kosztownego skalowania komponentów, które tego nie wymagają, takich jak funkcje analogowe.

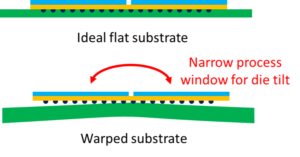

Osiągnięcie tego celu będzie jednak wymagało rozwiązania kilku złożonych i drażliwych kwestii. Po pierwsze, będzie to wymagało znacznie lepszej obserwowalności, monitorowania i analizy tego, co trafia do pakietu. Choć koncepcja umieszczania wielu żetonów w opakowaniu sięga lat 1990 moduły wieloukładowew przypadku chipletów matryce są zazwyczaj mniejsze i cieńsze, a dynamika sposobu ich charakteryzowania, testowania i obserwacji znacznie się zmieniła.

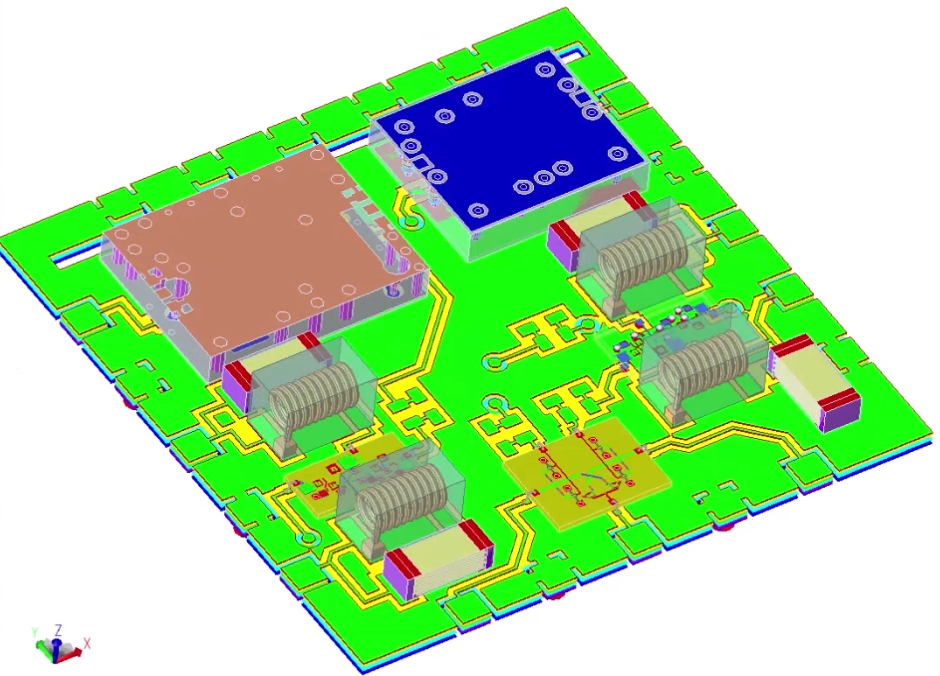

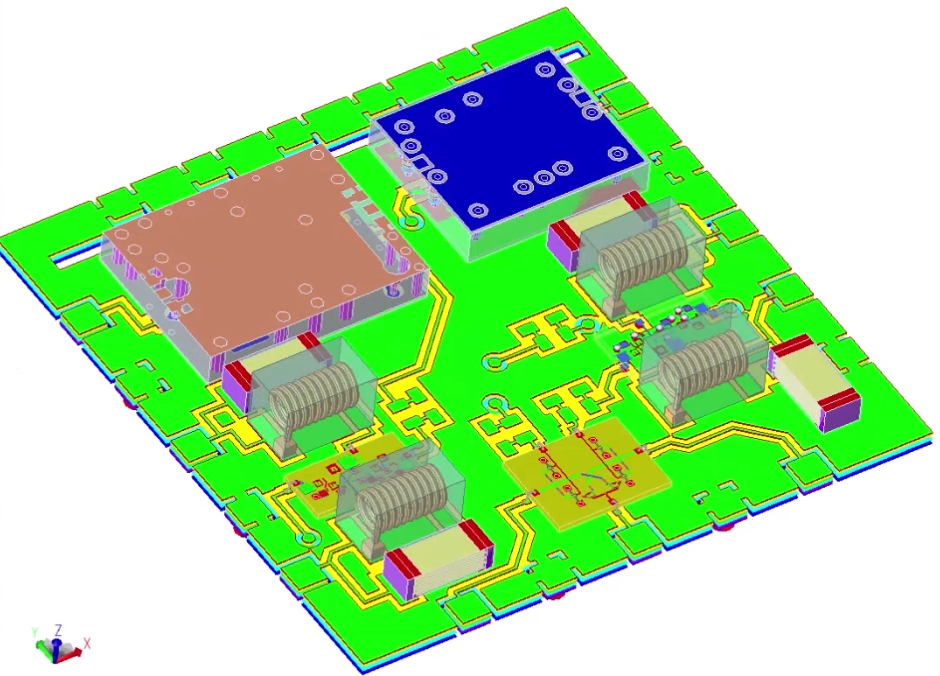

„Historycznie nazywaliśmy te moduły wielochipowe, które są obecnie bardzo popularne w świecie bezprzewodowym” – powiedział Nilesh Kamdar, kierownik ds. portfolio urządzeń RF/mikrofalowych w firmie Celownik. „Weź dowolny smartfon, a jego bezprzewodowy element to moduł front-end składający się z 20 do 30 chipów ściśniętych razem na małej przestrzeni mniejszej niż paznokieć. Dzieje się tak w branży od co najmniej dekady, jeśli nie dłużej. Tego rodzaju integracji wymagało także kilka problemów związanych z lotnictwem i kosmonautyką oraz innymi problemami o wysokiej częstotliwości, więc robiliśmy to w przeszłości”.

Rys. 1. Układ wielochipowego modułu RF pokazany w PathWave ADS firmy Keysight. źródło: Keysight

Zachodząca obecnie wielka zmiana obejmuje znacznie szersze zastosowanie tego podejścia, a także ulepszenia w konstrukcji chipletów oraz standardowe sposoby łączenia, testowania i mierzenia tego, co dzieje się wewnątrz samych chipletów, a także zaawansowanego pakietu, który je otacza.

„Motoryzacja jest doskonałym przykładem tego, co się zmienia” – powiedział Kamdar. „Na niedawnej konferencji wiceprezes dużego producenta OEM mówił, że nie można umieścić centrum danych na tylnym siedzeniu samochodu, ponieważ tego właśnie potrzeba dzisiaj, aby mieć pojazd autonomiczny. Jeśli dokonasz większej integracji — i jeśli w jakiś sposób sprawisz, że tablica zniknie i wszystko zostanie ściśnięte — może pionowo uda nam się wcisnąć to na tylne siedzenie samochodu. Istnieje wiele podobnych przypadków użycia. Zapotrzebowanie na moc chipletów może być niższe, jeśli weźmie się pod uwagę fizyczne centra danych. Istnieje wiele korzyści i to właśnie napędza dzisiejsze chipsety.”

Zmiany te są jednak zwodniczo złożone i być może branża będzie musiała wrócić do nauki w tym zakresie. „Budowanie chipletów na dużą skalę to model na tyle odmienny, że wszyscy musimy ponownie ocenić nasze umiejętności” – powiedział. „Musimy ponownie ocenić, w jaki sposób powstają organizacje i jak powstaje architektura. Musimy ponownie ocenić rolę projektanta systemu. Być może patrzyli na wszystko w inny sposób i mogli powiedzieć: „Jestem projektantem systemów”. Projektuję specyfikacje systemów. Dzielę go na mniejsze komponenty, pojedyncze układy scalone i rozpowszechniam specyfikacje. Wychodzę i wracam sześć miesięcy później i widzę, jak wszyscy sobie poradzili. Może to nawet nie jest możliwe. Być może istnieje wielu projektantów systemów, którzy muszą istnieć w górę i w dół łańcucha. Właśnie takie rozmowy muszą się odbyć. W gronie największych graczy w branży takie rozmowy już się toczą, ale nie wszędzie.

Liczba potencjalnych interakcji w kontekście projektu wielochipletowego jest znacząca i w wielu przypadkach specyficzna dla projektu. „Jeśli wierzysz w multi-diece, jeśli wierzysz w chiplety, musisz wierzyć, że to tylko zaostrzy cały problem [projektowania i integracji]” – powiedział Shekhar Kapoor, starszy dyrektor ds. zarządzania linią produktów w firmie Grupa Synopsys EDA. „Chiplets będą pochodzić z wielu miejsc i wielu źródeł. Będzie wiele możliwości wyboru, wiele opcji dla każdego. Największym problemem są obecne zastosowania tego wszystkiego. Duże firmy robią to w sposób szyty na miarę i dostosowany do indywidualnych potrzeb. Ale jeśli pójdziesz w kierunku standaryzacji, skąd wiesz, że nadchodzący chiplet będzie pasował do środowiska w produkcie, który próbujesz zbudować?”

Pomimo skupienia się na standardach takich jak UCIe i Bunch of Wires, nadal istnieją niuanse dotyczące charakterystyki poszczególnych chipletów w kontekście systemu. „Skąd tak naprawdę znasz jego profil? Wtedy pojawi się jeszcze więcej monitoringu, co będzie prawie jak podpis” – powiedział Kapoor. „Możesz to przeczytać i wiedzieć, czy jest idealny dla Twojego środowiska. Biorąc pod uwagę, że branża zmierza w kierunku szerszego wykorzystania chipletów, będzie to kluczowa kwestia. Pojawi się więcej wymagań, pojawi się więcej standardów, dzięki czemu będzie można zobaczyć, czy coś będzie pasować, czy nie.

Są też inne wyzwania, które trzeba pokonać.

„W przypadku chipletów wszystkie szybkie sygnały znajdują się w pakiecie, więc ich obserwowalność jest znacznie trudniejsza” – powiedziała Sue Hung Fung, menedżer ds. marketingu linii produktów w UCIe w firmie Kadencja. „Można tego dokonać poprzez sprawdzanie błędów łączy, skanowanie oczu, BiST itp., aby dostać się do znanej dobrej kości (KGD). Wszystkie metody testowe są zbudowane wokół tego. Ponadto cenne byłoby posiadanie dobrych monitorów stanu łącza, a od różnych dostawców pojawiają się nowe i różne propozycje”.

Kluczem jest monitorowanie jakości sygnału w kontekście pozostałych komponentów pakietu, co staje się trudniejsze w miarę podziału większej liczby funkcji na chiplety.

„Czy możemy monitorować sygnały i ich jakość podczas przesyłania danych? Techniki szkoleniowe są przeprowadzane przed trybem misji, aby poprawić niezawodność przesyłania danych” – zauważył Hung Fung. „Ponowne szkolenie nie jest pożądane, ponieważ może spowodować przerwanie transmisji danych. Musimy mieć możliwość ciągłego monitorowania i raportowania każdego pasa oraz wykrywania wszelkich zdarzeń, które mogą spowodować awarię, zanim awaria wystąpi. Zapobieganie awariom systemu i naprawa tych awarii obejmuje ponowne mapowanie pasów nadmiarowych lub inne metody naprawy w celu wykrycia marginalnie uszkodzonych pasów. Szkolenie i ciągłe monitorowanie tych wewnętrznych sygnałów chipletu stanowią wyzwania dla analizy zachowania łącza.

Grupy robocze UCIe chcą ujednolicić część tej obserwowalności, aby stworzyć ekosystem otwartych linków. Jednak dodanie obserwowalności i monitorowania również może się znacznie różnić w zależności od segmentu branżowego.

Randy Fish, dyrektor ds. zarządzania linią produktów w Grupie Synopsys EDA, wyjaśnił, że ze względu na brak standardowego podejścia i niewielu komercyjnych dostawców rozwiązań zapewniających obserwowalność, prawie wszystkie rozwiązania zostały wykonane na zamówienie. „Jeśli wejdziesz do któregokolwiek z czołowych półfinałów, oni coś zrobią” – powiedział. „Pytanie brzmi, czy istnieją funkcje związane z wieloma matrycami, które zmuszą nas do standaryzacji w celu posiadania spójnej infrastruktury do monitorowania i debugowania — zasadniczo po to, aby zobaczyć, co się dzieje, zwłaszcza jeśli otrzymujesz wiele kości od wielu dostawców. Niektóre rozwiązania z wieloma matrycami trafiają do motoryzacji i tam naprawdę dbają o takie rzeczy, jak starzenie się i to, co dzieje się z matrycami. A jak wiemy, są to zaawansowane węzły. To nie jest tak, że masz 6 kości dojrzałych, 10-letnich technologii. Są to zaawansowane węzły, które nie mają długiej historii. Z tego powodu istnieje wiele czynników, które to wymuszają.”

Chiplety również wprowadzają ciekawe kontrasty. Kamdar z Keysight zauważył, że podczas niedawnego panelu dyrektorów generalnych jeden z panelistów stwierdził, że chiplety charakteryzują się wyjątkową dychotomią. „Z jednej strony każdy chiplet może być niezależnym adresem IP, który można nabyć od dostawcy protokołu IP i zintegrować go ze swoim systemem stosunkowo niewielkim kosztem i stosunkowo łatwo. Jednak cały stos, który próbujesz zbudować, nagle zmusza cię do poznania wszystkiego. Wcześniej mogłeś po prostu powiedzieć: „Potrzebuję sześciu rzeczy”. Zamierzam kupić pięć z półki od dostawcy rozwiązań IP i oni dowiedzą się, czego potrzebuje. Skupię się na jednym. Ale teraz może ci się to nie udać. Być może będziesz musiał wiedzieć, jak wykonać wszystkie sześć i dowiedzieć się, jak to wszystko się dzieje, ponieważ złożoność problemu właśnie wzrosła. Może to zmusić branżę do początkowo umożliwienia rozwiązania tego problemu wyłącznie dużym graczom. Odniesienie sukcesu w tym środowisku może zająć mniejszym dostawcom znacznie więcej czasu”.

Niemniej jednak przyspieszenie integracji i przyjęcia chipletów zajmie więcej niż jedną firmę.

„Keysight wziął udział w sympozjum TSMC, które jest wydarzeniem bardziej publicznym, a po jego zakończeniu odbyły się warsztaty z udziałem wyłącznie partnerów będących częścią 3D Fabric Alliance” – powiedział Kamdar. „TSMC rozpoczęło i zakończyło cały dzień rozmową o tym, jak wszyscy musimy razem nad tym popracować, co potwierdzili inni uczestnicy, w tym AMD i Qualcomm. Prelegenci obu firm stwierdzili, że ani jedna firma EDA nie wie, jak samodzielnie rozwiązać problem chipletów. Cała branża musi współpracować.”

Wyzwania techniczne

Kolejnym kluczowym problemem związanym z chipletami jest rozpraszanie ciepła. Jest to część charakterystyki, ale w dużym stopniu zależy od przypadków użycia, wyboru opakowania i ogólnej architektury systemu w pakiecie.

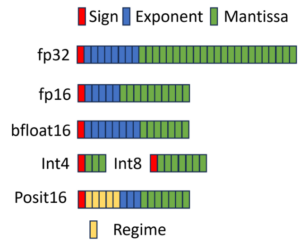

„W przypadku chipletów marginalność w projekcie jest niewielka, biorąc pod uwagę optymalny PPA (ukierunkowany na agresywną gęstość pj/bit i gęstość na plaży), co ma kluczowe znaczenie przy projektowaniu PHY chipletów” – powiedział Rishi Chugh, wiceprezes ds. marketingu produktów w Grupie IP w Cadence. „Niezawodność jest kluczowa, podobnie jak obserwowalność, która pozwala monitorować KGD, a także zapewniać komercyjny sukces operacyjny. Schematy integralności danych, takie jak CRC (cykliczna kontrola redundancji), skanowanie oczu, BiST i obwody monitorujące, zostały zaimplementowane w projekcie pod kątem wytrzymałości, a projekt musi być nadmiernie wyposażony w mechanizmy awarii, aby zapewnić odporność linii danych.

Cały rozdział w protokole UCIe poświęcony jest inicjalizacji i szkoleniu związanym z protokołem UCIe, co obejmuje aspekt obserwowalności protokołu, dodał Chugh.

Ponadto toczy się debata na temat tego, czy najtrudniejsze są faktyczne podstawy dodawania obserwowalności do systemu, czy też trudniejsza jest zmiana myślenia wokół tych koncepcji.

„Właściwie nie jest to aż tak skomplikowane w porównaniu z innymi rzeczami, ponieważ jest to «tylko» kolejny blok, z którym można się połączyć. Istnieje obserwacja, a my mamy możliwości śledzenia rzeczy” – powiedział Frank Schirrmeister, wiceprezes ds. rozwiązań i rozwoju biznesu w firmie Arteris IP. „Użytkownicy już żądają takich rzeczy, jak spojrzenie na rejestry z perspektywy oprogramowania. Zatem obecnie wyzwaniem staje się udostępnienie tych rejestrów w NoC. Z perspektywy NoC istnieją same protokoły, takie jak CHI, ACE, AMBA, OCP i inne, i to są mechanizmy języka – sposób, w jaki mówią i jak wchodzą w interakcje. W NoC, przy bardziej złożonych protokołach, pewne rzeczy dzieją się w wielu cyklach, więc musisz poczekać na odpowiedzi i odłożyć sprawy na później”.

Przypomina to spekulatywne wykonanie w procesorach. „Rozmawiamy o tych kredytach, na przykład o tym, jak długo muszę czekać na odpowiedź i tak dalej” – wyjaśnił Schirrmeister. – To wszystko są części protokołów. W NoC musisz zrozumieć takie kwestie, jak głębokość buforów? Kiedy właściwie czekam na dane? Częściowo jest to wydajność. Następnie, dla większej widoczności, możesz połączyć się z danymi, a czujniki mogą korzystać z własnej sieci, w zależności od tego, jak chcesz ją skonfigurować. W przypadku monitorów on-chip należy zdecydować, czy umieścić je na przykład na specjalnej szynie obserwowalności. Zawsze toczy się dyskusja, ile faktycznie mam debugowania? Ostatecznie jest to „tylko” kolejny interkonekt tych komponentów i trzeba zdecydować, jak go wyeksportować z chipa i tak dalej. To, ile przechowujesz na chipie, zależy tylko od tego, ile krzemu jestem skłonny na to wydać?”

Staje się to szczególnie ważne przy łączeniu chipsów. „Jak mogę się upewnić, że mam wystarczająco dużo miejsca na tę jednostkę obliczeniową, która wygląda jak dane i która w rzeczywistości nie dodaje żadnej wartości do bezpośredniej funkcji?” – pyta Gajinder Panesar, główny architekt w Picocom. „Może nie jestem ekspertem od monitorowania, ale wiem, że tego potrzebuję. Potrzebuję więc czegoś, co powie: „Po prostu naciśnij ten przycisk”. Masz środowisko, my projektujemy i „to” się dzieje. Idealnie byłoby, gdybyśmy obserwowali zachowanie wydajności procesora, a następnie dynamicznie dostrajali pewne aspekty rdzenia, aby uzyskać lepszą wydajność.

Jednym z elementów, który musi jeszcze zostać opracowany, jest dynamiczna kontrola urządzeń i regulacje, które można wprowadzać przez cały okres ich użytkowania.

„Załóżmy, że jesteśmy w stanie modelować wszystko od początku” – powiedział Lee Harrison, dyrektor ds. marketingu produktów w grupie Tessent w firmie Siemens Digital Industries Software. „Mamy wbudowane wszystkie monitory do wykonywania zadań wewnątrz systemu, ale to zamyka pętlę. W przypadku nowszych geometrii pozostaje jeszcze sporo do nauczenia się, aby naprawdę zoptymalizować sposób dostosowywania różnych parametrów urządzenia w celu zwiększenia jego niezawodności. Elementem, który zamyka pętlę prowadzącą do systemu życiowego, jest miejsce, w którym kryje się ogromna wartość. Jednak nadal jest wiele do zrobienia.

Zmiana ról odpowiedzialności

Komercyjne chiplety dodają kolejny drażliwy problem, a mianowicie, kto jest odpowiedzialny, gdy zostanie zaobserwowane coś nieoczekiwanego lub coś pójdzie nie tak.

„Jeśli jestem producentem chipów, robię chip i mogę przejść przez OSAT do testów” – powiedział Paul Karazuba, wiceprezes ds. marketingu w firmie Ekspedera. „Mogę używać ASE jako pakowalni, ale sprzedaję ją ze swoim nazwiskiem i moją gwarancją. Zrobi się ciekawie, gdy będziemy mieli chipsy. Na wszystkich naszych spotkaniach dotyczących chipletów zawsze pojawia się pytanie, kto będzie za co odpowiedzialny. Powiedzmy, że mam stworzyć chiplet AI i sprzedam go w systemie i pakiecie z chipletami sześciu innych firm. Która firma będzie udzielać gwarancji? Jaka firma wykona w nim usługę? W tej chwili nie ma prawdziwego konsensusu”.

Roboczy pomysł jest taki, że odpowiedzialna będzie firma, której nazwa znajduje się na zewnętrznej stronie opakowania, powiedział Karazuba. „To prawdopodobnie ta firma będzie ponosić ostateczną odpowiedzialność za obsługę swoich klientów, ale wnosi kolejny poziom usług, który muszą świadczyć producenci chipletów, a to będzie interesujące. Istnieje obawa, że około 2000 r. powstanie trójkąt Intel-Microsoft-Dell, w którym wszyscy będą wytykać się palcami. To obecnie niewypowiedziana obawa w branży”.

I może to nie jest jeden z chipsetów. Co się stanie, jeśli podłoże lub fizyczne połączenie międzysieciowe ulegną uszkodzeniu?

„Z testowego punktu widzenia chiplet może doskonale sprawdzać się w testach” – powiedział Karazuba. „Ale kiedy pojawia się problem z fizycznymi połączeniami, jak producent chipletów rozumie to w porównaniu z producentem modułów wielochipowych? To będzie interesujące. Jedynym sposobem rozwiązania tych problemów będzie metoda prób i błędów. Jako producenci półprzewodników możemy zaprojektować dowolną liczbę umów prawnych, ale jesteśmy na niezbadanych wodach i trzeba będzie dostosować. Modele wsparcia będą musiały zostać dostosowane, aby odzwierciedlić nową rzeczywistość, w której monolityczny krzem nie jest głównym narzędziem sprzedaży półprzewodników”.

Kapoor z Synopsys dostrzegł już swoje odbicie w ekosystemie. „Zawsze istniały ekosystemy, ale twój aktywny ekosystem, gdziekolwiek się znajdujesz, był może kolejnym kręgiem wokół niego. Jeśli zajmujesz się projektowaniem, będziesz zainteresowany jedynie zasadami projektowania odlewni i podręcznikiem zasad projektowania. To się zmienia, gdy mówisz o chipsach. Nawet mając projekt, teraz myślisz o testach jeszcze częściej niż kiedykolwiek wcześniej. Rozmawiasz z Przewaga i Teradyna. Nawet jeśli jesteś tylko projektantem, musisz dowiedzieć się, co musisz włożyć z punktu widzenia ATPG i jak to będzie testowane. Odpowiedni rozmiar ekosystemu rośnie.”

Mimo to branża nie ma innego wyjścia, jak tylko rozwiązać te problemy. „Rozmawialiśmy o rynku chipletów. Będziesz mógł wyciągnąć wykrojnik i przygotować go. Nadal jesteśmy od tego daleko, ale kroki w zakresie tego, co musimy osiągnąć, stają się coraz wyraźniejsze. Łączność to podstawa. Standardy UCIe są koniecznością, a wraz z nimi pojawiają się protokoły i zasady z punktu widzenia łączności, które należy ustalić. Następne byłyby bardzo jasno zdefiniowane modele. Na wyzwania, o których mówimy, wpływa w szczególności termika i moc. Istnieją już pewne standardy w tym zakresie i przejdziemy od łączności do modelu scharakteryzowanego, abyśmy mogli z niego bardziej niezawodnie korzystać. Wtedy będziemy potrzebować jakiegoś podpisu, na którym będziemy mogli zobaczyć, z testowalnego punktu widzenia, długość życia i to, jak każda śmierć będzie się zmieniać w różny sposób.

Dane wejściowe do tego wszystkiego będą pochodzić z chipów i monitorów systemowych, które również będą musiały opierać się na standardach.

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoAiStream. Analiza danych Web3. Wiedza wzmocniona. Dostęp tutaj.

- Wybijanie przyszłości w Adryenn Ashley. Dostęp tutaj.

- Kupuj i sprzedawaj akcje spółek PRE-IPO z PREIPO®. Dostęp tutaj.

- Źródło: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- :ma

- :Jest

- :nie

- :Gdzie

- $W GÓRĘ

- 1

- 20

- 30

- 3d

- a

- zdolność

- Zdolny

- O nas

- przyśpieszyć

- Osiągać

- aktywny

- rzeczywisty

- faktycznie

- Dodaj

- w dodatku

- dodanie

- dodatek

- Skorygowana

- Korekty

- Przyjęcie

- Reklamy

- zaawansowany

- Lotnictwo

- agresywny

- Starzenie się

- AI

- Wszystkie kategorie

- Alians

- dopuszczać

- już

- również

- zawsze

- am

- AMD

- ilość

- an

- analiza

- Analizując

- i

- Inne

- każdy

- Zastosowanie

- aplikacje

- podejście

- architektura

- SĄ

- na około

- AS

- aspekt

- aspekty

- powiązany

- At

- motoryzacyjny

- autonomiczny

- pojazd autonomiczny

- dostępny

- uniknąć

- z dala

- z powrotem

- na podstawie

- Gruntownie

- BE

- bo

- staje się

- staje

- być

- zanim

- Początek

- jest

- uwierzyć

- Korzyści

- BEST

- Ulepsz Swój

- Duży

- Najwyższa

- Bit

- Blokować

- deska

- obie

- przerwa

- Przynosi

- szeroki

- szerszy

- budować

- wybudowany

- Pęczek

- autobus

- biznes

- rozwój biznesu

- ale

- przycisk

- kupować

- by

- Kadencja

- nazywa

- CAN

- możliwości

- wózek

- który

- walizka

- Etui

- Spowodować

- Centrum

- Centra

- ceo

- pewien

- łańcuch

- wyzwanie

- wyzwania

- wyzwanie

- zmiana

- zmieniony

- Zmiany

- wymiana pieniędzy

- Rozdział

- charakteryzować

- charakteryzuje

- ZOBACZ

- Wykrywanie urządzeń szpiegujących

- szef

- żeton

- Frytki

- wybór

- wybory

- Okrągłe

- jaśniejsze

- wyraźnie

- Zamyka

- zamknięcie

- ZGODNY

- spoisty

- połączony

- jak

- byliśmy spójni, od początku

- przyjście

- handlowy

- Firmy

- sukcesy firma

- kompleks

- kompleksowość

- skomplikowane

- składniki

- pojęcie

- Koncepcje

- Troska

- zaniepokojony

- Konferencja

- Skontaktuj się

- połączony

- Łączność

- Zgoda

- Rozważać

- wynagrodzenie

- kontekst

- ciągły

- bez przerwy

- umowy

- kontrast

- kontrasty

- kontrola

- rozmowy

- rdzeń

- Koszty:

- mógłby

- obejmuje

- CPU

- CRC

- Kredyty

- istotny

- Aktualny

- Klientów

- dostosowane

- Cykle

- dane

- Centrum danych

- centra danych

- Daty

- dzień

- sprawa

- debata

- dekada

- zdecydować

- dedykowane

- głęboko

- zdefiniowane

- gęstość

- zależny

- W zależności

- Wnętrze

- zaprojektowany

- projektant

- projektanci

- projektowanie

- życzenia

- rozwinięty

- oprogramowania

- urządzenie

- urządzenia

- ZROBIŁ

- Umierać

- różne

- trudny

- cyfrowy

- Dyrektor

- znikać

- dyskusja

- dyskusje

- rozprowadzać

- do

- robi

- robi

- zrobić

- nie

- na dół

- jazdy

- podczas

- dynamiczny

- dynamicznie

- dynamika

- każdy

- z łatwością

- Ekosystem

- Ekosystemy

- wysiłek

- wyłaniać się

- umożliwiać

- włączanie

- zakończenia

- dość

- zapewnić

- Cały

- jednostka

- Środowisko

- błąd

- szczególnie

- zapewniają

- majątek

- itp

- Parzyste

- wydarzenie

- wydarzenia

- EVER

- wszyscy

- wszystko

- przykład

- egzekucja

- istnieć

- istnieje

- drogi

- ekspert

- wyjaśnione

- eksport

- rozciągać się

- oko

- tkanina

- Czynniki

- nie

- Brak

- daleko

- Moda

- strach

- kilka

- Figa

- Postać

- Ryba

- dopasować

- ustalony

- Skupiać

- W razie zamówieenia projektu

- wytrzymałość

- Siły

- naprzód

- Odlewnia

- od

- z przodu

- funkcjonować

- Funkcje

- fundamentalny

- Podstawy

- Sprzęt

- otrzymać

- miejsce

- dany

- Go

- cel

- Goes

- będzie

- dobry

- wspaniały

- bardzo

- Zarządzanie

- Grupy

- ręka

- zdarzyć

- Wydarzenie

- dzieje

- Have

- mający

- he

- Zdrowie

- tutaj

- Wysoki

- Wysoka częstotliwość

- wysoko

- historia

- dom

- W jaki sposób

- How To

- Jednak

- HTTPS

- olbrzymi

- i

- ICS

- pomysł

- idealny

- if

- Natychmiastowy

- Rezultat

- wpływ

- realizowane

- ważny

- niemożliwy

- podnieść

- ulepszenia

- in

- obejmuje

- Włącznie z

- wzrastający

- niezależny

- indywidualny

- przemysłowa

- przemysł

- Infrastruktura

- początkowo

- Wejścia

- integrować

- integracja

- integralność

- interakcji

- Interakcje

- ciekawy

- wewnętrzny

- najnowszych

- przedstawiać

- IP

- problem

- problemy

- IT

- JEGO

- właśnie

- Kapoor

- Klawisz

- Kicks

- Uprzejmy

- Wiedzieć

- znany

- Tor

- język

- duży

- później

- Prawo

- warstwa

- układ

- prowadzić

- prowadzący

- nauka

- najmniej

- Lee

- Regulamin

- poziom

- wifecycwe

- długość życia

- dożywotni

- lubić

- Linia

- LINK

- długo

- dłużej

- poszukuje

- Partia

- niski

- zrobiony

- Mainstream

- poważny

- robić

- producent

- Makers

- Dokonywanie

- i konserwacjami

- kierownik

- podręcznik

- zrobiony fabrycznie

- wiele

- rynek

- Marketing

- rynek

- dojrzały

- Maksymalna szerokość

- Może..

- zmierzyć

- Mechanizmy

- Spotkania

- metody

- może

- Misja

- Moda

- model

- modele

- moduł

- Moduły

- monitor

- monitorowanie

- monitory

- Monolityczny

- miesięcy

- jeszcze

- przeniesienie

- dużo

- wielokrotność

- musi

- my

- Nazwa

- Potrzebować

- wymagania

- sieć

- Nowości

- Następny

- Nie

- węzły

- zauważyć

- już dziś

- numer

- obserwować

- of

- poza

- on

- ONE

- trwający

- tylko

- koncepcja

- operacyjny

- Optymalny

- Optymalizacja

- Opcje

- or

- zamówienie

- organizacji

- Inne

- Inni uczestnicy

- Pozostałe

- ludzkiej,

- na zewnątrz

- zewnętrzne

- koniec

- ogólny

- Przezwyciężać

- własny

- pakiet

- pakowane

- opakowania

- płyta

- parametry

- część

- Uczestnicy

- szczególny

- szczególnie

- wzmacniacz

- strony

- Przeszłość

- Paweł

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- perspektywa

- fizyczny

- Fizycznie

- wybierać

- obraz

- kawałek

- sztuk

- rurociąg

- Miejsca

- planowanie

- plato

- Analiza danych Platona

- PlatoDane

- gracze

- punkt

- Punkt widzenia

- Popularny

- teczka

- możliwy

- potencjał

- power

- Możliwy do przewidzenia

- prezydent

- naciśnij

- Zapobieganie

- poprzednio

- pierwotny

- Wcześniejszy

- prawdopodobnie

- Problem

- problemy

- Procesory

- Produkt

- Profil

- Propozycje

- protokół

- protokoły

- zapewniać

- publiczny

- położyć

- Putting

- Qualcomm

- jakość

- pytanie

- Czytaj

- gotowy

- real

- nieruchomość

- Rzeczywistość

- naprawdę

- powód

- niedawny

- uznane

- odzwierciedlić

- Reflections

- rejestry

- stosunkowo

- niezawodność

- naprawa

- powtarzalne

- raport

- wymagać

- wymagany

- wymagania

- sprężysty

- odpowiedź

- Odpowiedzi

- odpowiedzialność

- odpowiedzialny

- REST

- prawo

- krzepkość

- Rola

- Zasada

- reguły

- Powiedział

- sprzedaż

- powiedzieć

- powiedzenie

- mówią

- Skala

- skalowaniem

- skanować

- systemy

- Szkoła

- Ekran

- widzieć

- widziany

- segment

- sprzedać

- Sprzedawanie

- Semiconductor

- senior

- czujniki

- usługa

- zestaw

- kilka

- Półka

- przesunięcie

- powinien

- pokazane

- bok

- Signal

- Sygnały

- znaczący

- znacznie

- Krzem

- podobny

- pojedynczy

- SIX

- Sześć miesięcy

- Rozmiar

- rozmiary

- umiejętności

- Spowolnienie

- mały

- mniejszy

- smartphone

- So

- Tworzenie

- Rozwiązania

- ROZWIĄZANIA

- Rozwiązywanie

- kilka

- coś

- Źródło

- Źródła

- Typ przestrzeni

- Głośniki

- specjalny

- okular

- spekulacyjny

- prędkość

- wydać

- Wyciskać

- stos

- standard

- standardy

- rozpoczęty

- Cel

- Nadal

- sklep

- sukces

- udany

- taki

- pozwać

- dostawcy

- wsparcie

- Sympozjum

- system

- systemy

- Brać

- trwa

- Mówić

- rozmawiać

- kierowania

- Techniki

- Technologies

- REGULAMIN

- test

- Testowanie

- niż

- że

- Połączenia

- ich

- Im

- sami

- następnie

- teoria

- Tam.

- termiczny

- Te

- one

- rzecz

- rzeczy

- Myślący

- to

- tych

- chociaż?

- Przez

- czas

- do

- już dziś

- razem

- w kierunku

- wyśledzić

- Trening

- przenieść

- próba

- próba i błąd

- TSMC

- zazwyczaj

- zrozumieć

- W toku

- Nieoczekiwany

- wyjątkowy

- us

- posługiwać się

- używany

- Cenny

- wartość

- różnorodny

- pojazd

- sprzedawca

- sprzedawców

- Przeciw

- pionowy

- pionowo

- początku.

- Wiceprezes

- Zobacz i wysłuchaj

- czekać

- Czekanie

- chcieć

- była

- Wody

- Droga..

- sposoby

- we

- DOBRZE

- poszedł

- Co

- Co to jest

- jeśli chodzi o komunikację i motywację

- czy

- który

- Podczas

- KIM

- cały

- którego

- rozpowszechniony

- będzie

- skłonny

- bezprzewodowy

- w

- w ciągu

- Praca

- pracować razem

- pracujący

- warsztat

- świat

- by

- Źle

- jeszcze

- ty

- Twój

- zefirnet