Banias Labs to firma produkująca półprzewodniki, która opracowuje rozwiązania infrastrukturalne dla komunikacji nowej generacji. Jej rynkiem docelowym jest rynek infrastruktury obliczeniowej o wysokiej wydajności, obejmujący hiperskalowe centra danych, sieci, sztuczną inteligencję, moduły optyczne i układy SoC przełączników Ethernet dla powstających projektów obliczeń o wysokiej wydajności. Te układy SoC wymagają konstrukcji szybkich sieci Ethernet i rozwiązań o niskim opóźnieniu, aby zapewnić zwiększoną wydajność systemu i skrócić czas wprowadzenia produktu na rynek. Firma opracowała optyczny układ SoC DSP w procesie technologicznym 5 nm, aby sprostać wymaganiom tego rynku.

![]()

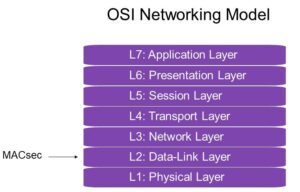

Optyczny układ DSP SoC to wyspecjalizowany typ układu na chipie (SoC) przeznaczony do stosowania w szybkich systemach komunikacji optycznej. Oprócz procesora DSP, optyczny układ SoC DSP zazwyczaj zawiera bloki IP szybkiego interfejsu, takie jak kontrolery pamięci Ethernet PHY IP, PCIe IP i DDR. Tego typu układy SoC umożliwiają szybkie przesyłanie danych przy małych opóźnieniach w celu przetwarzania sygnału w czasie rzeczywistym. Zostały również zaprojektowane tak, aby minimalizować zużycie energii, co czyni je idealnymi do zastosowań wymagających wydajnej pracy przy zmniejszonych problemach termicznych. Z zaletami wiążą się także wyzwania. Specjalistyczne wymagania systemów komunikacji optycznej sprawiają, że projektowanie optycznego SoC DSP jest większym wyzwaniem niż projektowanie zwykłego SoC.

Wyzwania wdrożeniowe

Wyzwania dotyczą złożoności projektu, wysokich wymagań dotyczących mocy i wydajności oraz konieczności spełnienia różnych standardów branżowych. Integracja wielu bloków IP, w tym procesora DSP, Ethernet PHY IP i innych niestandardowych bloków, wymaga starannego projektowania i sprawdzania poprawności. Dodatkowe szybkie interfejsy, takie jak PCIe i DDR, dodatkowo zwiększają złożoność projektu. Szybkie interfejsy i wiele bloków IP w systemie mogą powodować zniekształcenia sygnału, przesłuchy i zakłócenia elektromagnetyczne, co może mieć wpływ na wydajność i niezawodność systemu. Aby mieć pewność, że system spełni wymagania dotyczące wydajności i niezawodności, należy przeprowadzić analizę i optymalizację integralności sygnału i mocy na wczesnym etapie cyklu projektowania. Wreszcie, dotrzymanie wymagań dotyczących czasu wprowadzenia produktu na rynek może stanowić wyzwanie. Rynek infrastruktury obliczeniowej o wysokiej wydajności szybko się rozwija, a zespoły programistów SoC muszą szybko dostarczać swoje projekty, aby wyprzedzić konkurencję.

Dotarcie do sukcesu pierwszego przejścia krzemu

Pokonanie powyższych wyzwań wymaga kompleksowego podejścia. Jednym z kluczowych elementów rozwiązań o wysokiej wydajności i niskim opóźnieniu jest Ethernet PHY IP. Ethernet PHY IP jest odpowiedzialny za interfejs warstwy fizycznej pomiędzy SoC a siecią Ethernet. Adres IP musi obsługiwać szybkie interfejsy Ethernet, w tym 10G, 25G, 40G, 50G, 100G, 200G, 400G i 800G, a także zapewniać małe opóźnienia i niskie zużycie energii. Dodatkowo adres IP musi obsługiwać różne standardy, w tym IEEE 802.3 i Ethernet Alliance. Kolejnym ważnym elementem jest pakiet projektowy EDA. Pakiet projektowy EDA musi zapewniać kompleksowe rozwiązanie do projektowania i weryfikacji SoC, w tym optymalizację mocy, analizę wydajności, optymalizację obszaru i analizę wydajności. W zakresie, w jakim pakiet projektowy EDA zawiera zaawansowane funkcje, takie jak sztuczna inteligencja (AI) i uczenie maszynowe (ML), tym lepiej, jeśli chodzi o większą produktywność i krótszy czas wprowadzenia produktu na rynek.

Synopsys przyspiesza sukces pierwszego przejścia krzemu

Synopsys oferuje rozwiązania, które odpowiadają unikalnym wyzwaniom związanym z rozwojem układów SoC dla rynku infrastruktury obliczeniowej o wysokiej wydajności. Firma zapewnia kompleksowe rozwiązanie IP, które obejmuje studium wykonalności routingu, wytyczne dotyczące podłoża, modele integralności sygnału i mocy oraz dokładną analizę przesłuchów. Jest to konieczne, aby sprostać wyzwaniom związanym z integralnością sygnału i mocy, jakie stoją przed opracowywaniem optycznego SoC DSP. 112G Ethernet PHY IP firmy Synopsys oferuje niskie opóźnienia, elastyczne długości zasięgu i dojrzałość w technologii procesowej 5 nm, co czyni go idealnym rozwiązaniem dla hiperskalowych centrów danych, sieci, sztucznej inteligencji, modułów optycznych i układów SoC przełączników Ethernet. Ponadto Synopsys oferuje pakiet EDA Design Suite, który zapewnia wysokiej jakości wyniki przy zoptymalizowanej mocy, wydajności, powierzchni i wydajności. Oparty na sztucznej inteligencji pakiet EDA Design Suite firmy Synopsys zapewnia rozwiązania zwiększające wydajność systemu i skracające czas wprowadzenia produktu na rynek, co czyni go niezbędnym elementem udanego rozwiązania dla rynku infrastruktury obliczeniowej o wysokiej wydajności.

Podsumowanie

Synopsys zapewnia rozwiązania o wysokiej wydajności i niskim opóźnieniu, które przyspieszają rozwój zaawansowanych przełączników Ethernet i sieciowych układów SoC. Aby dowiedzieć się więcej o kompleksowych rozwiązaniach IP firmy Synopsys, kompleksowym pakiecie EDA Design Suite i pakiecie EDA z ulepszoną sztuczną inteligencją, odwiedź następujące strony.

Kompleksowe rozwiązania IP firmy Synopsys

Kompleksowy pakiet EDA firmy Synopsys

Pakiet EDA Design Suite oparty na sztucznej inteligencji firmy Synopsys

Przeczytaj także:

Systemy Multi-Die: największe zakłócenia w informatyce od lat

Zaspokajanie rosnącego głodu przepustowości za pomocą szybkiego Ethernetu

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- Platoblockchain. Web3 Inteligencja Metaverse. Wzmocniona wiedza. Dostęp tutaj.

- Wybijanie przyszłości w Adryenn Ashley. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/327703-synopsys-accelerates-first-pass-silicon-success-for-banias-labs-networking-soc/

- :ma

- :Jest

- a

- O nas

- powyżej

- przyśpieszyć

- przyspiesza

- dodatek

- Dodatkowy

- do tego

- adres

- zaawansowany

- Zalety

- przed

- AI

- Alians

- również

- an

- analiza

- i

- Inne

- aplikacje

- podejście

- SĄ

- POWIERZCHNIA

- na około

- sztuczny

- sztuczna inteligencja

- Sztuczna inteligencja (AI)

- AS

- At

- przepustowość

- BE

- Ulepsz Swój

- pomiędzy

- Najwyższa

- Bloki

- podnieść

- CAN

- ostrożny

- Centrum

- wyzwania

- wyzwanie

- jak

- Komunikacja

- Komunikacja

- sukcesy firma

- konkurencja

- kompleksowość

- składnik

- składniki

- wszechstronny

- computing

- konsumpcja

- Stwórz

- krytyczny

- zwyczaj

- cykl

- dane

- Centrum danych

- dostarczyć

- dostarcza

- Wnętrze

- zaprojektowany

- projektowanie

- projekty

- rozwinięty

- rozwijanie

- oprogramowania

- rozwija się

- Zakłócenie

- Wcześnie

- wydajny

- wschodzących

- umożliwiać

- wzmocnione

- zapewnić

- niezbędny

- ewoluuje

- w obliczu

- FAST

- Korzyści

- W końcu

- i terminów, a

- elastyczne

- następujący

- W razie zamówieenia projektu

- od

- dalej

- Rozwój

- wytyczne

- wysoka wydajność

- wysokiej jakości

- HTML

- HTTPS

- głód

- idealny

- IEEE

- obraz

- Rezultat

- tryb rozkazujący

- ważny

- in

- obejmuje

- Włącznie z

- wzrosła

- przemysł

- standardy przemysłowe

- Infrastruktura

- integracja

- integralność

- Inteligencja

- Interfejs

- interfejsy

- IP

- problemy

- IT

- JEGO

- Labs

- Utajenie

- warstwa

- UCZYĆ SIĘ

- nauka

- niski

- maszyna

- uczenie maszynowe

- robić

- Dokonywanie

- rynek

- dojrzałość

- Maksymalna szerokość

- Poznaj nasz

- Spotkanie

- Pamięć

- wzmiankowany

- ML

- modele

- moduł

- jeszcze

- wielokrotność

- Potrzebować

- sieć

- sieci

- następna generacja

- of

- Oferty

- on

- ONE

- działanie

- optymalizacja

- zoptymalizowane

- Inne

- własny

- opakowania

- przechodzić

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- fizyczny

- plato

- Analiza danych Platona

- PlatoDane

- Post

- power

- wygląda tak

- przetwarzanie

- Procesor

- wydajność

- zapewniać

- zapewnia

- szybko

- szybko

- dosięgnąć

- Czytaj

- w czasie rzeczywistym

- Zredukowany

- regularny

- niezawodność

- wymagać

- wymagania

- Wymaga

- odpowiedzialny

- Efekt

- Ryzyko

- Semiconductor

- Signal

- Krzem

- rozwiązanie

- Rozwiązania

- wyspecjalizowanym

- standardy

- pobyt

- Badanie

- sukces

- udany

- taki

- apartament

- wsparcie

- Przełącznik

- system

- systemy

- cel

- Zespoły

- Technologia

- niż

- że

- Połączenia

- ich

- Im

- termiczny

- Te

- one

- to

- do

- także

- transfery

- typy

- zazwyczaj

- wyjątkowy

- posługiwać się

- uprawomocnienie

- różnorodny

- weryfikacja

- przez

- Odwiedzić

- który

- w

- Wydajność

- Twój

- zefirnet